Abstract

In the modern era, the demand for high-speed communication has led to a growing preference for higher bandwidth. However, in wideband scenarios, the presence of neighboring bands can introduce nonlinearity issues in mixers. The RF stage and Switching stage are identified as the primary contributors to nonlinearity in down-conversion mixers. This article presents a basic principle as well as circuit architectures of the mixer, including a performance parameters comprehensive review of linearity improvement techniques employed in down-conversion mixers. The paper categorizes various previously reported methods to enhance the linearity of the RF stage into five approaches: (1) MGTR/Derivative superposition (DS), (2) Complementary DS (CDS), (3) noise cancellation (NC), (4) post distortion (PD), and (5) feedforward or feedback approach. These techniques aim to enhance the Second-order nonlinearity (\(g_{m}^{\prime }\)) or third-order nonlinearity (\(g_{m}^{\prime \prime }\)) of the RF stage. Among these approaches, Noise Cancellation (NC) methods demonstrate superior optimization in terms of Conversion Gain, Linearity, and Noise Figure. Furthermore, to improve the linearity of the switching stage in mixers, the static and dynamic current injection methods can be employed. The objective of this review is to contribute to the advancement of linearity improvement techniques for wideband active down-conversion mixers, while also facilitating future research and development in this field.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The demand for fast data-rate wireless communication is experiencing rapid growth in today’s world, especially in urban areas, placing significant emphasis on the RF Front end (RFFE), which must operate across a wide range of frequencies [1]. Several receiver architectures are available for implementing wireless systems, including super-heterodyne, low IF, direct conversion, image rejection, and digital IF receivers [2]. Among these, the low IF architecture shown in Fig. 1 is a preferred solution for wideband applications due to its ability to eliminate DC offsets and the tendency to reduce the flicker (1/f) noise [3, 4].

Direct-conversion Receiver architectures for Ultra-Wideband (UWB) [2]

The RF Front End (RFFE) comprises several crucial elements, such as low noise amplifiers (LNA),down-conversion mixers, and oscillators (VCO). Among these components, the performance of the LNA - MIXER pair plays a pivotal role in the overall performance of the RFFE, including aspects like linearity, Noise Figure (NF), and Conversion gain. Therefore, it is essential to enhance the performance of the LNA–MIXER pair simultaneously to achieve significant improvements in the overall RFFE performance [5].

The upper limit of the dynamic range in the Radio Frequency Front-End (RFFE) system is determined by linearity [6], with the lower limit influenced by system noise. The Noise Figure (NF) of the mixer significantly impacts RF system performance, affecting both received and processed signals. Implementing mixers with CMOS technology ensures optimal performance, characterized by low power consumption and high integration density [7, 8].

The CMOS mixer can be divided into two types: active and passive. The active mixer utilizes a current signal for frequency conversion, while the passive mixer employs a voltage signal for the conversion. Passive mixers showcase advantages such as less flicker noise (1/f), superior linearity, and wideband properties compared to their active counterparts [5]. However, passive mixers require higher LO signal power for driving, leading to inherent conversion losses, poor reverse isolation, and potential issues with larger noise coefficients and troublesome IQ crosstalk. As a remedy, compensatory peripheral circuits become necessary for passive mixers.

On the flip side, active mixers demand less LO signal power, offer higher conversion gain (\(G_{c}\)) performance, and provide better isolation between RF, LO, and IF ports than passive mixers, enhancing noise rejection for subsequent circuit modules [9]. Nevertheless, they tend to exhibit lower linearity compared to passive mixers [2]. The choice between active and passive mixers in the design process must be made based on the expected performance index (Table 1). With the continuous improvement in mixer performance, most mixers now include modules based on the Gilbert double-balanced mixer [10].

The active mixer consists of two types [11]:

-

Switched Transconductance (Sw+Gm) Mixer: The mixers depicted in Fig. 2 utilize Switched Transconductance (Sw+Gm) technology, employing four CS MOSFETs (\(M_{3}\)–\(M_{6}\)) within their RF input stage to create RF transconductance pairs. These mixers also feature an LO switching stage (\(M_{1}\)–\(M_{2}\)) that operates differentially, modulating the bias current (\(I_{B}\)+\(i_{RF}\)) that passes through the RF transconductance pairs. Furthermore, they incorporate a load stage (\(R_{L}\)) where periodically commutated RF signal current is transformed into an IF signal voltage. The Sw+Gm Mixer demonstrates superior thermal noise performance due to minimal noise from switching devices, making it advantageous for applications with low-voltage requirements. This aspect is emphasized in an analysis detailed in [12], focusing on a mixer tailored for low-voltage operation challenges. It achieves competitive performance at reduced supply voltages by employing switches tied exclusively to supply voltages. This design choice addresses gate-oxide reliability issues and minimizes voltage headroom requirements by employing two transconductors with cross-coupled outputs activated by switches, effectively competing with traditional mixers. Moreover, the integration of low-ohmic switches minimizes voltage drop, maximizing supply voltage headroom and enhancing conversion gain. Furthermore, [11] presents a mathematical model addressing flicker noise mechanisms in Switching Transconductance (Sw+Gm) mixers, along with challenges posed by parasitic capacitance at high frequencies (HF). Additionally, in [13], the Sw+Gm mixer is evaluated for its high mixer common-mode rejection ratio (MCMRR). Recommendations from this analysis include utilizing sinusoidal LO driving for noise advantages and integrating an inductor resonating structure to tackle operation frequency limitations due to tail parasitic capacitances. The paper also discusses strategies for reducing flicker noise in mixers designed for direct-conversion receivers, such as incorporating a PMOS transconductance structure.

-

Gilbert (Gm+Sw) Mixers: These mixers utilize LO switch pairs (\(M_{3}\)–\(M_{6}\)) to modulate the RF current (\(I_{B}\)+\(i_{RF}\)) from an RF transconductance stage(\(M_{1}\)–\(M_{2}\)), controlled by a large LO signal. This process completes the frequency conversion from RF to IF. The configuration of this Gilbert cell mixer is illustrated in Figs. 3 and 4. The operational aspects of this mixer type are extensively discussed in [14].

Fig. 3 Double balanced mixer (Gm+Sw) configuration [19]

Fig. 4 Single balanced mixer configuration [19]

Table 2 presents a discussion comparing Gilbert (Gm+Sw) Mixers with Switched Transconductance (Sw+Gm) Mixers. Moreover, as the number of cascaded stages increases, there is a corresponding increase in nonlinearity and noise, leading to various effects such as harmonic distortion, intermodulation, cross-modulation, gain compression, and desensitization [4]. Therefore, the role of the mixer is crucial as it directly influences the linearity (IIP2, IIP3), noise figure (NF), and conversion gain (\(G_{c}\)).

Designing down-conversion active mixers for wideband applications requires special attention to linearity due to 2nd order intermodulation (IM2) and 3rd order intermodulation (IM3) occurring within the frequency bands [2]. Therefore, ensuring high linearity is vital to mitigate the impact of these intermodulation distortions in wideband scenarios.

The Active double-balanced mixer consists of 3 stages [10]:

-

(i)

RF transconductance stage (\(M_{1}\)–\(M_{2}\)): This stage converts the RF voltage signal into current, utilizing a biased differential pair that functions as the RF transconductance amplifier.

-

(ii)

Switching Stage (\(M_{3}\)–\(M_{6}\)): Driven by a local oscillator signal (LO), the switching stage (\(M_{3}\)–\(M_{6}\)) is tasked with performing the mixing operation.

-

(iii)

Load/IF Stage (\(R_{L}\)): This stage plays a dual role by converting current to IF voltage and serving as the load for the mixer. Additionally, it functions as the intermediate frequency (IF) amplifier.

The operation of the active mixer is extensively discussed in [14]. The double-balanced structure provides advantages such as LO rejection, rejection of even-order distortion products, higher conversion gain (\(G_{c}\)), and improved noise performance. However, it exhibits considerably worse linearity [5, 15] and flicker noise performance [12].

Flicker noise (1/f noise), becomes a significant consideration especially when mixers are used in Direct Conversion Receivers (DCR) applications. This type of noise manifests in all three stages of the mixer: the RF stage, the load stage, and particularly in the switching MOS devices.

RF Stage Flicker noise is up-converted into LO frequency and that does not appear at the baseband [14]. Properly sizing active load devices or using poly resistors in the mixer can minimize flicker noise in the load stage. major concern about the Switching noise: Mismatches in the switching pair contribute to flicker noise which is extensively discussed in [16]. Various techniques have been reported to reduce flicker noise in CMOS active mixers, such as negative Impedance [16], dynamic current injection [17] and RF leakageless static current bleeding with resonating inductors [18]. These methods aim to enhance mixer performance, particularly in applications demanding low noise and high linearity for the Direct Conversion Receivers (DCR) applications.

2 Sources of non-linearity in mixer

The active mixer consists of 3 stages: RF transconductance, switching, and load/IF. Non-linearity in mixers can be traced back to two main stages:

-

1.

RF transconductance stage: The primary source of non-linearity in this stage is attributed to the MOSFET (\(M_{1}\)–\(M_{2}\)), as discussed in Sect. 2.1.

-

2.

Switching stage: The non-linearity of the mixer is influenced by the non-ideal switching behavior exhibited by MOSFETs (\(M_{3}\)–\(M_{6}\)), as discussed in Sect. 2.2.

These two stages, RF transconductance and switching play significant roles in the occurrence of non-linearity in the active mixer, and their effects are thoroughly explored in the respective sections of the paper.

2.1 Transconductance stage non-linearity (RF stage \(M_{1}\)–\(M_{2}\))

Active mixer gets an amplified version of the input from LNA (\(v_{RF}\)) and converts it into current (\(i_{RF}\)) through the of RF MOSFET (\(M_{1}\)–\(M_{2}\)) as shown in Fig. 3.

The non-linearity introduced by the RF stage originates from two sources [20, 21]:

-

1.

Transconductance (\(g_{m}\)): Converts the linear input (\(v_{RF}\)) into non-linear output current (\(i_{RF}\)).

-

2.

Non-linear output conductance (\(g_{ds}\)): The effect of this component becomes noticeable when there is a high output voltage swing at the drain node of (\(M_{1}\)–\(M_{2}\)).

The non-linear behavior exhibited by the RF stage (\(M_{1}\)), as illustrated in Fig. 4, can be modeled using a power series, with the higher-order coefficients being omitted.

where

where \(g_{m1}\) = Transconductance of MOSFET \(M_{1}\) and \(i_{RF}\) = Output current of MOSFET \(M_{1}\).

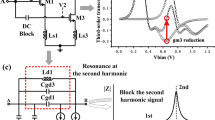

Figure 5 illustrates the simulated profile of 2nd order non-linearity (\(g_{m1}^{\prime }\)) and 3rd order non-linearity (\(g_{m1}^{\prime \prime }\)) for the RF stage (\(M_{1}\)). The presence of non-zero \(g_{m}^{\prime }\) and \(g_{m}^{\prime \prime }\) of the RF stage degrades the IIP3 (third-order intercept point) performance of the mixer according to Eq. 3. Consequently, different techniques have been reported in the literature [20, 21] to mitigate or nullify the effects of \(g_{m}^{\prime }\) and \(g_{m}^{\prime \prime }\) of the RF stage (\(M_{1}\)). These techniques include (1) Multiple Gated Transistor (MGTR)/Derivative Superposition (DS) [15, 22,23,24], (2) Complementary Derivative Superposition (CDS) [25,26,27], (3) Noise/Distortion cancellation (NC) [24, 28,29,30,31,32], (4) Post Distortion (PD) [33, 34], and (5) Feedback Approach [35].

RF stage MOS (\(M_{1}\)) transconductance profile (gpdk 90nm CMOS process, W/L = 120/100, Vds = 1 Volt) [19]

2.2 Switching stage non-linearity (\(M_{3}\)–\(M_{4}\))

The mixing process takes place in the switching stage (\(M_{3}\)–\(M_{4}\)), where the current (\(i_{RF}\)) is combined with the LO signals, as depicted in Fig. 4. The desired condition for an ideal mixing operation is to have one MOSFET in the switching stage in the ON state while the other MOSFET is in the OFF state. However, in practical scenarios, achieving this ideal condition is not possible due to the sinusoidal nature of the Local Oscillator (LO) signal. The sinusoidal LO signal causes both the switching stage MOSFETs to be turned ON simultaneously for a certain period [19]. To ensure that both the RF stage (\(M_{1}\)) and the switching MOSFETs (\(M_{3}\)–\(M_{4}\)) remain in the saturation regime, the voltage at the drain node of the switching MOSFETs must be sufficiently high. If the voltage at the drain node of the switching MOSFETs is not adequately high, the switching MOSFETs (\(M_{3}\)–\(M_{4}\)) will operate in the triode region, introducing non-linearity into the switching stage [36].

The small signal current (\(i_{01}\)) of an \(M_{3}\) is a function of the instantaneous values of the transconductance stage’s output current (\(i_{RF}\)) and Local oscillator voltage \(V_{LO}(t)\) shown in Fig. 6. This relationship can be represented by the equation:

In the equation above, \(I_{B}\) and \(i_{01}\) represent the DC currents resulting from the biasing conditions Comparison table of Gilbert (Gmat the RF stage and the output of the LO stage, respectively. The third-order Taylor expression of Eq. 5

where

Periodic waveforms of non-linearity coefficients are shown in Fig. 6. For sinusoidal LO, will be non-zero for the time interval \(\left( \Delta \right)\) in which either \(M_{2}\) or \(M_{3}\) enters in triode regime before the other MOSFET turns OFF. This deteriorates the linearity of mixer [19].

Typical waveforms of \((q_1\left( t\right) {,\ q}_2\left( t\right) \,and \ q_3\left( t\right) )\) [19]

3 Linearization methods

In an active CMOS mixer, the non-linearity of the RF transconductor stage MOSFETs (\(M_{1}\)–\(M_{2}\)) can be mitigated by canceling out the effects of \(g_{m}^{\prime }\) and \(g_{m}^{\prime \prime }\). Similarly, to enhance the linearity of the switching stage, it is important to maintain a sufficient voltage at the drain node of (\(M_{3}\)–\(M_{4}\)) to prevent these MOSFETs from entering the triode region [17], as well as to keep \(M_{1}\) and \(M_{2}\) in the saturation regime.

Sections 3.1 to 3.4 discuss various methods for boosting the linearity of the RF transconductor stage. On the other hand, Sect. 3.5 specifically focuses on techniques to enhance the non-linearity of the switching stage.

3.1 Multiple gated transistor (MGTR)/derivative superposition (DS)

The simulations of \(g_{m1}^{\prime }\) and \(g_{m1}^{\prime \prime }\) for the RF stage MOSFET (\(M_{1}\)) are depicted in Fig. 5. The profile of \(g_{m1}^{\prime \prime }\) exhibits both a positive peak and a negative peak. In order to mitigate the impact of \(g_{m1}^{\prime \prime }\), an auxiliary MOSFET (\(M_{1A}\)) is introduced and connected in parallel with \(M_{1}\), as depicted in Fig. 7. The Simulation results presented in Figs. 8 and 9. By precisely adjusting the biasing voltage for the weak inversion region and sizing of the auxiliary MOSFET (\(M_{1A}\)), it is possible to achieve cancellation by overlapping the negative peak of \(g_{m1}^{\prime \prime }\) for \(M_{1}\) and the positive peak of \(g_{m1A}^{\prime \prime }\) for \(M_{1A}\). Consequently, the overall value of \(g_{m1}^{\prime \prime }+g_{m1A}^{\prime \prime }\) becomes zero as shown in Fig. 9, effectively eliminating the undesired non-linearity caused by \(g_{m1}^{\prime \prime }\). This cancellation technique helps in enhancing the linearity of the RF stage by minimizing the distortions introduced by \(g_{m1}^{\prime \prime }\).

However, utilizing a single auxiliary MOSFET (\(M_{1A}\)) has limitations in terms of achieving a corrected flat zone due to the asymmetrical positive and negative properties. To extend the flat zone and improve linearity, multiple auxiliary MOSFETs can be connected in parallel with \(M_{1}\). However, this approach leads to gain degradation due to increased parasitic capacitance [20]. The \(g_{m1}^{\prime }\) and \(g_{m1A}^{\prime }\) profiles for transistors \(M_{1}\) and \(M_{1A}\) exhibit only a positive peak as depicted in Fig. 8. Biasing \(M_{1}\) and \(M_{1A}\) to mitigate 3rd order non-linearity reduces \(g_{m}^{\prime \prime }\) but introduces 2nd order non-linearity in the form of increased total \(g_{m}^{\prime }\) (\(g_{m1}^{\prime }+g_{m1A}^{\prime }\)). Consequently, this trade-off leads to a degradation in the 2nd order input intercept point (IIP2), negatively impacting the linearity performance.

Limitations of using an auxiliary MOSFET in the weak inversion region in the Derivative Superposition (DS) method include (a) Limited frequency range of operation, (b) Inability to handle large input signals, and (c) Sensitivity to PVT variations (process, voltage, and temperature) for linearity improvement.

The Derivative Superposition (DS) technique has been employed in various literature [15, 22,23,24, 37, 38] to linearize the \(g_{m1A}^{\prime \prime }\) of the CS transconductance stage MOSFET \(M_{1}\), either on its own or in combination with other techniques.

3.2 Complementary derivative superposition (CDS)

Derivative superposition (DS) linearization approach to improve the IIP3 but degrade the IIP2 performance of the mixer. To address this issue, the auxiliary NMOS (\(M_{1A}\)) can be replaced with a PMOS (\(M_{1P}\)) in the Complementary Derivative Superposition (CDS) method [39] as shown in Fig. 10. Output current (\(i_{RF}\)) can be written as,

From Eq. 7, the total \(g_{m}\) will increase to (\(g_{m1}\) + \(g_{m1p}\)). \(g_{m1}^{\prime }\) of \(M_{1}\) and \(g_{m1p}^{\prime }\) of \(M_{1P}\) are added with opposite signs, resulting in an overall \(g_{m}^{\prime }\) of zero, while \(g_{m1}^{\prime \prime }\) of \(M_{1}\) and \(g_{m1p}^{\prime \prime }\) of \(M_{1P}\) are subtracted with the same sign, resulting in a reduction in \(g_{m}^{\prime }\), as shown in Figs. 11 and 12. A cancellation window for \(g_{m}^{\prime \prime }\) is wider for DS compared to CDS. Therefore, the enhancement in IIP3 is not as substantial as that observed in Derivative Superposition (DS).

In the Complementary DS (CDS) technique, the optimal biasing of \(g_{m1}^{\prime }\) and \(g_{m1}^{\prime \prime }\) does not coincide. Consequently, two options are available: \(g_{m1}^{\prime \prime }\) and \(g_{m1p}^{\prime \prime }\) can be matched to achieve a good 3rd order input intercept point (IIP3) while partially cancelling \(g_{m1}^{\prime }\), and \(g_{m1p}^{\prime }\) can be matched to attain the optimal 2nd order input intercept point (IIP2).

The CDS technique is used to linearize the transconductance stage of the down-conversion mixer, which is operated for Band-1 (3.1\(-\)4.8 GHz) of the UWB mixer [25]. In [26] and [27], various versions of CDS are discussed which can be used in the mixer to improve the IIP3 and IIP2. \(g_{m1}^{\prime \prime }\) of the RF stage of an active mixer can be canceled by applying a voltage to the bulk terminal, called the Gate-Bulk Interaction Technique [40, 41].

3.3 Post distortion (PD)

The Post-distortion method, as compared to the DS method, employs an auxiliary MOSFET connected at the drain of the RF stage MOSFET. This auxiliary MOSFET is utilized to cancel out the \(g_{m}^{\prime }\) and \(g_{m1}^{\prime \prime }\) characteristics of the RF stage MOSFET (\(M_{1}\)) in mixers [33].

Figures 13 and 14 illustrate the implementation of CG and CS post-distortion, with MOSFETs \(M_{1}\) and \(M_{2}\) degenerated by resistance (\(Z_{s}\)). The increased parasitic capacitance reduces conversion gain (\(G_{c}\)) at higher frequencies, mainly due to Cgs of the LO MOSFET (\(M_{3}\) - \(M_{6}\)) as shown in Fig. 3. To counteract the effects of parasitic capacitance at the source node of the switching stage and ensure a consistent conversion gain (\(G_{c}\)) across a wider frequency range, inductor \(L_{1}\) (depicted in Fig. 13) and inductor \(L_{2}\) (depicted in Fig. 14) are introduced between the LO and RF stages. Recent research, as reported in [42], proposes the utilization of Active Inductor (AI) instead of simple inductors, offering enhanced bandwidth.

The implementation of CG and CS post-distortion are shown in Figs. 13 and 14, where MOSFET \(M_{1}\) and \(M_{2}\) is degenerated by resistance (\(R_s\)). For CG implementation, current flowing through the \(M_{1}\) and \(M_{1Q}\) can be written as,

where,

By observing Eqs. 11 and 12, it becomes evident that the linearity (IIP3) can be enhanced by reducing the term (\(g_{m1}^{\prime \prime }\) + \(g_{m1Q}^{\prime \prime }\)). To achieve this, proper biasing of the transistors (\(M_{1}\)) and (\(M_{1Q}\)) is required.

Common Gate (CG) Post-distortion [33]

Common Source (CS) Post-distortion [33]

However, the post-distortion (PD) method offers advancements in 2 key aspects:

-

1.

The auxiliary MOSFET is connected to the output of the main MOSFET rather than directly to the input. This minimizes the impact on input matching, ensuring better overall performance.

-

2.

All MOSFET operates in saturation, providing a more robust cancellation of distortions.

These advancements make the post-distortion method a more suitable technique for canceling out \(g_{m1}^{\prime }\) and \(g_{m1}^{\prime \prime }\) in the RF stage MOSFET (\(M_{1}\)). The post-distortion method involves operating both MOSFETs \(M_{1}\) and \(M_{1Q}\) in the saturation region, which results in no degradation of the conversion gain (\(G_{c}\)) and noise figure compared to the DS and CDS methods.

3.4 Noise/distortion cancellation

Noise is a crucial consideration in mixer design, with the Noise Figure (NF) often being relatively high. Various circuit topologies are employed to minimize both flicker [16] and white noise in CMOS mixers. In [43], a novel RF CMOS Gilbert mixer is proposed to enhance NF. This mixer utilizes a PMOS switching circuit with an inductor to sharpen switching transitions and reduce flicker noise at the switching stage. Additionally, in [24, 28,29,30,31, 44], circuit topologies are utilized to minimize RF stage noise in CMOS down-conversion mixers. The principle of noise cancellation is depicted in Fig. 15, with \(R_{s}\) representing the source impedance. The concept of noise cancellation [45] involves the identification of two nodes (X and Y) in the RF stage. At these nodes, the signal exhibits opposite polarities, while the noise from the input transistor exhibits the same polarity. When nodes X and Y satisfy this condition, their voltages can be appropriately scaled and combined, resulting in the addition of signal components and cancellation of noise components.

Two topologies can be utilized for noise cancellation in the RF stage of the Mixer: (1) Common Gate (CG)-Common Source (CS) topology (2) Common Source (CS) topology with feedback (resistive).

CG- CS approach differential output [30]

CG-CS approach single ended output [31]

CS Resistive feedback [29]

3.4.1 CG-CS topology

The CG-CS approach offers two possible output configurations, namely the differential output [30] and the single-ended output [31, 46], as illustrated in Figs. 16 and 17 respectively. The utilization of a differential output in the differential approach eliminates the requirement for a balun at the input of the RF stage. However, there are various trade-offs to consider among gain, IIP3 (3rd order intercept point), and noise figure. To mitigate these trade-offs, one can introduce an additional NMOS (\(M_{1F}\)) to convert the differential output to single-ended output as shown in Fig. 17. This conversion helps in eliminating the trade-offs associated with the differential approach.

In the CG-CS noise cancellation approach, the input CG MOSFET (\(M_{1E}\)) generates a noise voltage with opposite polarity at nodes X and Y, while the input signal remains in phase, as depicted in Figs. 15 and 16 respectively. To combine the input signal and effectively cancel the noise (channel, thermal) and distortion generated by the input MOSFET (\(M_{1E}\)) at the output, it is necessary for the gain of the CG stage (\(M_{1E}\)) and the CS stage (\(M_{1}\)) to be equal. This condition results in the Noise Cancellation Condition for differential output as,

For single-ended output,

In the CG-CS topology, the RF signal is applied to the source of the CG MOSFET (\(M_{1E}\)). The impedance seen at the source of (\(M_{1E}\)) is approximately \(\left( {\frac{1}{{g_{{m1E}} }}} \right)\), allowing for the straightforward achievement of wideband input matching by appropriately setting the value of (\(g_{m1E}\)). Limitations:

-

1.

The inclusion of an additional MOSFET (\(M_{1F}\)) in the CG-CS single-ended output configuration of Fig. 17 leads to increased noise compared to the CG-CS differential configuration.

-

2.

While the noise and distortion originating from (\(M_{1E}\)) are effectively eliminated by the noise cancellation (NC) methods, it is important to note that the presence of (\(M_{1F}\)) and (\(M_{1}\)) can still introduce residual noise and distortion. These residual factors can potentially impact the linearity performance of the mixer.

3.4.2 CS-resistive feedback topology

This approach, as shown in Fig. 18, replaces the CG input MOSFET (\(M_{1E}\)) with a CS MOSFET (\(M_{1C}\)), distinguishing it from the CG-CS topology. As discussed in the CG-CS topology, the noise and RF signal from the input MOSFET (\(M_{1C}\)) generate opposite polarity noise voltage at Node X and an in-phase RF signal at Node Y. Noise cancellation condition for CS-Resistive feedback topology can be written as,

Modified noise cancellation approach [29]

This approach suffers from insufficient output impedance, making it unsuitable for direct integration as the RF stage in the down-conversion mixer. However, in [29], an enhanced resistive feedback noise cancellation approach is presented. This modification involves substituting the source follower (\(M_{1D}\)) with a common-gate (CG) amplifier and replacing the input RF stage with a complementary resistive feedback amplifier (\(M_{2NC}\), \(M_{2PC}\) and \(R_F\)). Additionally, the output is converted into a complementary output stage, as depicted in Fig. 19. This modification results in additional feed-forward signal amplification, leading to increased gain and reduced noise in the circuit. Furthermore, the modified approach exhibits a desirable characteristic of high output impedance, making it well-suited for use as an RF stage in the down-conversion mixer. The noise cancellation condition for Fig. 19 can be modified as given in [29].

where, \(g_{m1N}\), \(g_{m1P}\), \(g_{m1D}\) are the transconductance of MOSFET \(M_{1N}\), \(M_{1P}\) and \(M_{1D}\) respectively. The output complementary stage allows the cancellation of distortion from \(M_{1N}\) and \(M_{1D}\) effectively by \(M_{1P}\), which is biased in the weak inversion region and carefully optimized around the sweet spot to minimize \(g_{m1N}^{\prime \prime }\) and \(g_{m1D}^{\prime \prime }\). This optimization leads to a noticeable improvement in IIP3. Furthermore, to remove the impact of second-order interaction on IIP3, complementary configurations are proposed in [28]. The CG-CS noise cancellation approach for the RF stage in a mixer is superior to the CS-Resistive approach, especially in situations where wideband (WB) input matching, higher conversion gain (\(G_{c}\)), and low Noise Figure (NF) are required.

3.5 Current injection

The methods mentioned above, such as noise cancellation (NC), post-distortion (PD), CDS (complementary DS), and DS (Derivative Superposition), are utilized to eliminate \(g_{m1}'\) and \(g_{m1}''\) in the RF STAGE \(M_{1}\), resulting in an enhancement of IIP3.

Moreover, as explained in Sect. 2.2, the mixer’s IIP3 is affected by the time interval (\(\left( \Delta \right)\)) when one of the switching MOSFETs enters the triode region, leading to deterioration in the linearity of the mixer, as depicted in Fig. 6. To prevent the switching MOSFETs from entering the triode region, it is necessary to maintain a sufficient voltage at the drain node of \(M_{3}\) and \(M_{4}\). To accomplish this, both static and dynamic current injection approaches have been proposed in [17], as illustrated in Figs. 20 and 21.

Minimum node voltages at X and Y can be written as,

where, \(V_{ovn}\) = Overdrive voltage of MOSFET \(M_{n}\).(n = 1,2,3,4)

Static current injection method [17]

Dynamic current injection method [17]

The implementation of static current injection involves the connection of PMOS transistors \(M_{7}\) and \(M_{8}\) across the load resistor (\(R_{L}\)), as depicted in Fig. 20. To ensure that the external current sources (\(M_{7}\) and \(M_{8}\)) remain in saturation during LO zero crossings, it is necessary to maintain a sufficient voltage across the load resistor.

The static current injection method [17] involves the continuous injection of a constant current throughout the entire duration of the LO signal. While this approach provides only a limited improvement in conversion gain, it helps mitigate signal compression at the output. To further enhance conversion gain and reduce signal compression, dynamic current injection is utilized. In this method, the current is injected at the nodes X and Y using a PMOS (\(M_{7}\) - \(M_{10}\)) cross-coupled pair, as depicted in Fig. 21. Additionally, dynamic current injection eliminates the voltage across the \(R_{L}\) at the zero crossing LO signal.

Furthermore, the current bleeding/Injection method also enhances flicker (1/f) noise performance, which involves reducing the current in the switching stage to decrease the height of noise pulses [18]. This reduction is achieved by introducing additional bias current (\(I_{bld}\)) at the source node of the switching stage, as illustrated in Fig. 22. The current bleeding technique aims to lower the bias current of the LO switches. However, this action leads to an increase in the impedance of the LO switches as observed from the RF stage. Furthermore, RF leakage current enters the bleeding circuit, resulting in reduced conversion gain (\(G_{c}\)) and allowing more RF current to be diverted by the parasitic capacitance (\(C_{p}\)) at the node between the LO switches and the RF transconductance stage. Minimizing \(C_{p}\) is crucial for indirectly reducing flicker noise [16]. To achieve this, using smaller device sizes for the LO switches is appropriate, although it may increase intrinsic flicker (1/f) noise. Another proposed technique, dynamic current bleeding, enhances flicker-noise performance by injecting a dynamic current equal to the bias current of the LO switches only during LO switching events [16].

4 Research scope, challenges and future direction

4.1 Research Scope and Challenges

In the field of communication technology, Ultra-Wideband (UWB) devices have experienced rapid growth across diverse domains, including medical applications, short-range distance communication, positional tracking, and beyond [2, 3, 15, 21]. The extensive adoption of UWB underscores the need for continuous advancements in downconversion mixer research, offering both opportunities for future developments and significant challenges.

-

(A)

Challenges in mixer design for specific applications: Creating a down-conversion mixer tailored for a specific job is quite a challenge. It needs to perform well in areas like conversion gain (\(G_{c}\)), Noise Figure (NF), Linearity (IIP3, IIP2, P1dB), Port-to-Port Isolation, and more [10]. Achieving this optimal performance depends on how well we design and optimize CMOS mixers. However, this task comes with its share of difficulties, such as managing extra flicker noise, reducing LO port leakage, controlling high power consumption, and solving other tricky problems. Designing CMOS mixers is like solving a complex puzzle with many different elements that need to be just right. It’s not just about making something that works; it’s about making something that works well while navigating through all these challenges [10].

-

(B)

Growing demand for bandwidth and research focus: In recent years, the surge in demand for expanded bandwidth has propelled intensified research efforts in multiband mixers [10, 47]. The exploration of Multiband or Wideband mixers exposes challenges associated with nonlinearity stemming from neighboring bands. Consequently, the pursuit of enhanced linearity, particularly concerning 2nd and 3rd order non-linearity, has become a noteworthy and actively researched domain in the realm of multiband mixers.

-

(C)

Linearization techniques and ongoing challenges: This review article delves into various linearization techniques, providing a thorough analysis and detailed comparisons. Table 3 encapsulates a comprehensive overview of reported linearization techniques for down-conversion mixers. Notably, challenges persist in achieving an optimal balance. The Capacitive feedback approach [37] achieves an Average Value of IIP3 of 20.5 dBm, but at the expense of noise performance (NF = 16.9 dB). Despite advancements, challenges linger, as evidenced by higher Noise Figure (NF) ranging from 11 to 14 dB in methods like CDS and DS/MGTR [15, 22, 23].

4.2 Future direction

-

(a)

Optimizing down-conversion mixer parameters:

-

(b)

Addressing challenges through innovative techniques:

-

Methods like noise cancellation have been applied in the context of mixer design [31, 28, 29]. Although these strategies show positive results in aspects such as IIP3, conversion gain (\(G_{c}\)), and noise figure (NF), obstacles still exist. The challenge lies in achieving simultaneous enhancements in both IIP3 and IIP2 at the RF stage while addressing signal compression at the IF stage, presenting a substantial hurdle. This emphasizes the possibility of future improvements to enhance the overall performance across the Wideband (WB) spectrum.

-

-

(c)

Incorporating innovative techniques from LNA architectures:

-

Incorporating inventive methodologies from various Low-Noise Amplifier (LNA) architectures into mixers has the potential to augment performance. The utilization of various gain (gm) boosting techniques at the Common Gate (CG) stage [29, 30] can diminish the matching inductor size (\(L_{in}\)) and enhance matching. The integration of this improved LNA with a down-conversion mixer shows promise for enhancing linearity at the RF stage. Exploring additional techniques like inductive peaking [31, 50], active inductors [42], bulk LO injection, etc., in mixer design aims to widen the bandwidth. It’s essential to acknowledge that these methods may introduce additional parasitic capacitance. Subsequent research in this field could focus on layout optimizations to further refine and propel these concepts.

-

5 Conclusion

This article has explored various linearity improvement methods for CMOS Active current commutating mixers. The investigation involved considering trade-offs between linearity, conversion gain, and power dissipation. The use of DS and CDS techniques proved effective in enhancing the linearity of the RF stage (\(g_{m}^{\prime }\) and \(g_{m}^{\prime \prime }\)), but it led to a degradation in the Noise Figure. To further improve IIP3, IIP2, and \(P_{1}dB\) in the RF stage, noise cancellation techniques in combination with linearization methods such as DS, CDS, or post-distortion can be applied simultaneously. Additionally, dynamic current injection can be implemented to enhance the linearity of the switching stage. By employing linearization techniques at both the switching and RF stages of the mixer, better overall linearization performance can be achieved. These findings contribute to advancing linearity techniques for CMOS Active current commutating mixers and guide the design of high-performance and linear mixers in practical wideband applications.

References

Wang L-C, Wong V, Schober R, Ng D. Key technologies for 5G wireless systems. 1st ed. Cambridge: Cambridge University Press; 2017.

Manstretta D, Laurenti N, Castello R. A reconfigurable narrow-band MB-OFDM UWB receiver architecture. Circuits Syst II Express Briefs IEEE Trans. 2008;55(4):324–8. https://doi.org/10.1109/TCSII.2008.922168.

Chung T.-C, Chen C.-W, Chen O.T.C, Tsen R.Y.J. A multi-band rf front-end receiver for bluetooth, WCDMA, and GPS applications. 2003 46th Midwest Symp Circuits Syst. 2003;3:1175–11783. https://doi.org/10.1109/MWSCAS.2003.1562503.

Razavi B. RF Microelectronics (2nd Edition) (Prentice Hall Communications Engineering and Emerging Technologies Series). 2nd ed. USA: Prentice Hall Press; 2011.

Gharpurey R. Linearity enhancement techniques in radio receiver front-ends. Circuits Syst I Regular Papers IEEE Trans. 2012;59:1667–79. https://doi.org/10.1109/TCSI.2012.2206507.

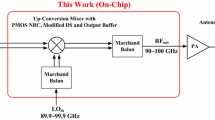

Tsai J-H, Wu P-S, Lin C-S, Huang T-W, Chern J, Huang W-C. A 25–75 GHz broadband gilbert-cell mixer using 90-nm CMOS technology. Microwave Wirel Compon Lett IEEE. 2007;17:247–9. https://doi.org/10.1109/LMWC.2007.892934.

Depari A, Sisinni E, Flammini A, Ferri G, Stornelli V, Barile G, Parente F. Autobalancing analog front end for full-range differential capacitive sensing. IEEE Trans Instrum Meas. 2018. https://doi.org/10.1109/TIM.2017.2785160.

Dan S, Xiaolin Z. Low-voltage CMOS folded-cascode mixer. Chin J Aeronaut. 2010;23:198–203. https://doi.org/10.1016/S1000-9361(09)60205-3.

Suriya K, Durga G. Design of 50-75 ghz v-band low power and high gain down-conversion mixer. In: 2014 International conference on communication and signal processing, pp. 1625– 1629 ( 2014). https://doi.org/10.1109/ICCSP.2014.6950123

Satyanarayana R, Avvaru S. Design and optimization of double balanced gilbert cell mixer in 130 nm CMOS process. Solid State Electron Lett. 2020;2:129–39. https://doi.org/10.1016/j.ssel.2020.12.004.

Guo B, Gong J, Wang Y, Liu C, Li L, Wu J, Liu H. Low-frequency noise in CMOS switched-gm mixers: a quasi-analytical model. IEEE Access. 2020;8:191219–30. https://doi.org/10.1109/ACCESS.2020.3032297.

Klumperink EAM, Louwsma SM, Wienk GJM, Nauta B. A CMOS switched transconductor mixer. IEEE J Solid-State Circuits. 2004;39(8):1231–40. https://doi.org/10.1109/JSSC.2004.831797.

Guo B, Gong J. A dual-band low-noise CMOS switched-transconductance mixer with current-source switch driven by sinusoidal lo signals. IEEE Int Midwest Sympos Circuits Syst (MWSCAS). 2021. https://doi.org/10.1109/MWSCAS47672.2021.9531696.

Terrovitis MT, Meyer RG. Noise in current commutating CMOS mixers. IEEE J Solid-State Circuits. 1999;34:772–83. https://doi.org/10.1109/4.766811.

Chen J.-D. A low-voltage high-linearity ultra-wideband down-conversion mixer in 0.18-\(\mu\)m CMOS technology. Microelectron J. 2011;42:113–26. https://doi.org/10.1016/j.mejo.2010.08.019.

Cheng W, Annema AJ, Wienk GJM, Nauta B. A flicker noise/im3 cancellation technique for active mixer using negative impedance. IEEE J Solid-State Circuits. 2013;48(10):2390–402. https://doi.org/10.1109/JSSC.2013.2272339.

Mohsenpour M. Method to improve the linearity of active commutating mixers using dynamic current injection. IEEE Trans Microwave Theory Tech. 2016. https://doi.org/10.1109/MWSYM.2016.7540373.

Park J, Lee CJ, Kim B-S, Laskar J. Design and analysis of low flicker-noise CMOS mixers for direct-conversion receivers. IEEE Trans Microwave Theory Tech. 2007;54:4372–80. https://doi.org/10.1109/TMTT.2006.885582.

Terrovitis M, Meyer R. Intermodulation distortion in current-commutating CMSO mixers. IEEE J Solid-State Circuits. 2000;35:1461–73. https://doi.org/10.1109/4.871323.

Zhang H, Sanchez-Sinencio E. Linearization techniques for CMOS low noise amplifiers: a tutorial. IEEE Trans Circuits Syst I Regul Papers. 2011;58:22–36. https://doi.org/10.1109/TCSI.2010.2055353.

Patel NK, Koringa HP. Systematic analysis of linearization techniques for wideband RF low-noise amplifier. In: Darji AD, Joshi D, Joshi A, Sheriff R, editors. Adv VLSI Embed Syst. Singapore: Springer; 2023. p. 27–44. https://doi.org/10.1007/978-981-19-6780-1_3.

Bidi A, Karimi G. Design of high linearity inductor-less active CMOS mixer based on volterra series analysis. Circuits Syst Signal Process. 2020. https://doi.org/10.1007/s00034-020-01407-9.

Abbasi H, Yavari M. A wideband low-noise inductor less CMOS active mixer with improved linearity. Iran Int Conf Microelectron. 2021. https://doi.org/10.1109/IICM55040.2021.9730140.

Solati P, Yavari M. A wideband high linearity and low-noise CMOS active mixer using the derivative superposition and noise cancellation techniques. Circuits Syst Signal Process. 2019;38:1–21. https://doi.org/10.1007/s00034-019-01023-2.

Parvizi M, Nabavi A. Low-power highly linear UWB CMOS mixer with simultaneous second- and third-order distortion cancellation. Microelectron J. 2010;41:1–8. https://doi.org/10.1016/j.mejo.2009.10.005.

Yarahmadi A, Jannesari A. Design of a highly linear gain stage with complementary derivative superposition technique. Wireless Pers Commun. 2019;107:1–8. https://doi.org/10.1007/s11277-019-06352-8.

Qin P, Xue Q. A low voltage folded-switching mixer using area-efficient CCG transconductor. IEEE Trans Circuits Systems II Express Briefs. 2016. https://doi.org/10.1109/TCSII.2016.2611609.

Guo B, Wang X, Chen H, Chen J. A 0.5-6.5-GHz 3.9-dB NF 7.2-mW active down-conversion mixer in 65-nm CMOS. Mod Phys Lett B. 2018;32:1850278. https://doi.org/10.1142/S0217984918502780.

Guo B, Wang H, Yang G. A wideband merged CMOS active mixer exploiting noise cancellation and linearity enhancement. IEEE Trans Microwave Theor Tech. 2014;62:2084–91. https://doi.org/10.1109/TMTT.2014.2334555.

Vallee H, Taris T, Mesnard T, Montoriol G, Hours X. A 1–9 GHz wideband downconverter with noise cancellation and gm-boosted transconductance cell. IEEE Int Conf Electron Circuits Syst. 2018. https://doi.org/10.1109/ICECS.2018.8618012.

Ho S. A CMOS broadband low-noise mixer with noise cancellation. IEEE Trans Microwave Theor Tech. 2010;58:1126–32. https://doi.org/10.1109/TMTT.2010.2045568.

Zhang H, Tang S, Cai M, Jiang Y. A 77-GHz down-conversion mixer with +18.4 dB high gain, +12.2 dBm OIP3, and low noise in 90-nm CMOS technology. J Infrared Millimeter Terahertz Waves. 2023;44(5):379–96. https://doi.org/10.1007/s10762-023-00917-2.

Gladson C, Vijayalakshmi S, Lakshmi M, Manickam B. Linearity improvement of RF mixer using double-linearization for 5GHz applications. AEU - Int J Electron Commun. 2019. https://doi.org/10.1016/j.aeue.2019.152856.

Bijari A, Zandian S. Linearity improvement in a CMOS down-conversion active mixer for WLAN applications. Analog Integrated Circuits Signal Process. 2019. https://doi.org/10.1007/s10470-019-01482-2.

Seyedi H, Dehdasht-Heydari R, Roshani S. UWB down-conversion mixer using an im3 cancellation modified technique for zero and low if applications. Microelectron J. 2021;109:104983. https://doi.org/10.1016/j.mejo.2020.104983.

Manstretta D, Brandolini M, Svelto F. second-order intermodulation mechanisms in CMOS downconverters. IEEE J Solid-State Circuits. 2003;38:394–406. https://doi.org/10.1109/JSSC.2002.808310.

Lin H-H, Lin Y-H, Wang H. A high linearity 24-GHz down-conversion mixer using distributed derivative superposition technique in 0.18-\(\mu\)m CMOS process. IEEE Microwave Wireless Compon Lett. 2017. https://doi.org/10.1109/LMWC.2017.2774142.

Yargholi M, Darvishi F. A 1.2v, low-power, and high linear UWB down-conversion CMOS mixer. Eng Appl Sci Res. 2021;48(3):280–6.

Im D, Nam I, Kim HT, Lee K. A wideband CMOS low noise amplifier employing noise and IM2 distortion cancellation for a digital TV tuner. IEEE J Solid-State Circuits. 2009;44:686–98. https://doi.org/10.1109/JSSC.2008.2010804.

Asghari M, Yavari M. Using the gate-bulk interaction and a fundamental current injection to attenuate im3 and im2 currents in rf transconductors. IEEE Trans Very Large Scale Integr VLSI Syst. 2015;24:1–1. https://doi.org/10.1109/TVLSI.2015.2394244.

Bansal G, Chaturvedi A, Kumar M. High linearity and high gain bulk driven down conversion mixer for UWB system. Int Conf Comput Commun Network Technol (ICCCNT). 2017. https://doi.org/10.1109/ICCCNT.2017.8204022.

Bhatt D. Design of wideband active mixer by using an active inductor. IEEE Asia-Pac Microwave Conf (APMC). 2019. https://doi.org/10.1109/APMC46564.2019.9038630.

Yoon J, Kim H, Park C, Yang J, Song H, Lee S, Kim B. A new RF CMOS gilbert mixer with improved noise figure and linearity. IEEE Trans Microw Theory Tech. 2008;56(3):626–31. https://doi.org/10.1109/TMTT.2008.916942.

Guo B, Wang H, Chen J, Deilamsalehi M. A CMOS low-noise active mixer with enhanced linearity and isolation by exploiting capacitive neutralization technique. Mod Phys Lett B. 2019;33:1950204. https://doi.org/10.1142/S021798491950204X.

Bruccoleri F, Klumperink E, Nauta B. Wide-band CMOS low-noise amplifier exploiting thermal noise canceling. IEEE J Solid-State Circuits. 2004;39:275–82. https://doi.org/10.1109/JSSC.2003.821786.

Bae B, Han J. 24–40 GHz gain-boosted wideband CMOS down-conversion mixer employing body-effect control for 5G NR applications. IEEE Trans Circuits Syst II Express Briefs. 2022;69(3):1034–8. https://doi.org/10.1109/TCSII.2021.3119995.

Chiou H-K, Chen Y, Yen H-L. A 5–12 GHz double-balanced power mixer with differential transmission-line transformer in 0.18-\(\mu\)m CMOS. IEEE CPMT Sympos Japan (ICSJ). 2017. https://doi.org/10.1109/ICSJ.2017.8240060.

Piccinni G, Avitabile G, Coviello G, Talarico C. A novel optimization framework for the design of gilbert cell mixers. Int Midwest Sympos Circuits Syst (MWSCAS). 2017. https://doi.org/10.1109/MWSCAS.2017.8053198.

Piccinni G, Talarico C, Avitabile G, Coviello G. Innovative strategy for mixer design optimization based on gm/ID methodology. Electronics. 2019. https://doi.org/10.3390/electronics8090954.

Bijari A, Mallaki MA. A merged LNA-mixer with wide variable conversion gain and low noise figure for WLAN direct-conversion receivers. J Electr Comput Eng Innovat (JECEI). 2024;12(1):175–86. https://doi.org/10.22061/jecei.2023.10124.679.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Vaghela, A., Koringa, H. Advances in active down-conversion mixer linearity techniques: a comprehensive review. Discov Electron 1, 3 (2024). https://doi.org/10.1007/s44291-024-00004-3

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s44291-024-00004-3