Abstract

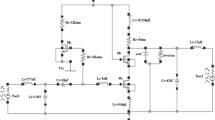

In this work, a 0.18 μm CMOS LNA is designed which is favorable for a wireless application and the topology used in this design is cascode inductive source degeneration. This proposed LNA is basically designed for ultra-wideband which will be suitable for RF receiver. For an LNA to be in RF receiver, the LNA must be able to amplify very weak signal of – 100 dBm (3.2 uV), must consume very minimum power and lastly, noise generated by LNA must be very small. These requirements are achieved with help of cascode inductive source degeneration topology. This work also presents noise analysis of MOSFET along with LNA’s noise and other parameters analysis. Possible types of topologies are also discussed. The proposed LNA provides a good gain of 19.79 dB, an NF of 2.03 dB, reverse isolation (S12) of − 35.2 dB, input return loss (S11) of − 12.2 dB, and output return loss (S22) of − 12 dB, while consuming 10.8 mW from the supply of 1.8 V. The proposed LNA is simulated in Cadence Spectra using 180 nm UMC technology.

Similar content being viewed by others

References

Balodi D, Verma A, Govidacharyulu PA (2016) A high gain low noise amplifier design & comparative analysis with other MOS-topologies for Bluetooth applications at 130 nm CMOS. In: Proceedings of IEEE industrial electronics and applications conference, pp 378–383

Bhale VP, Dalal UD (2014) Optimization of CMOS 0.18 μm low noise amplifier for wireless applications. Int J Inf Electron Eng 4(2):92–97

Chiu H-W, Lu S-S, Lin Y-S (2005) A 2.17-dB NF 5-GHz-band monolithic CMOS LNA with 10-mW DC power consumption. IEEE Trans Microw Theory Tech 53(3):813–824

Chu Y, Liao C, Chuang H (2003) 5.7 GHz 0.18/spl mu/m CMOS gain-controlled LNA and mixer for 802.11a WLAN applications. In: Proceedings of IEEE radio frequency integrated circuits symposium, pp 221–224

Feng YuX, Lim WM, Gu J, Sui W (2013) Compact 50–62 GHz current-reused low-noise amplifier with gate-drain transformer feedback. Electron Lett 49(11):720–722

Gatta F et al (2001) A 2-dB noise figure 900-MHz differential CMOS LNA. IEEE J Solid State Circuits 36(10):1444–1452

Guo W, Huang D (2002) The noise and linearity optimization for 1.9 GHz CMOS low noise amplifier. In: Proceedings of IEEE Asia Pacific conference on ASIC, pp 253–257

Han K et al (2005) Complete high-frequency thermal noise modeling of short-channel MOSFETs and design of 5.2-GHz low noise amplifier. IEEE J Solid State Circuits 40(3):726–735

Haraz O (2012) Why do we need ultra-wideband? (1). VLSI Egypt. https://www.vlsiegypt.com/home/?p=518. Accessed 19 Nov 2012

Huang Z-Y, Huang C-C (2007) A CMOS low noise amplifier with RLC-impedance feedback for 3–5 GHz ultra-wideband wireless system. In: Proceedings of IEEE international symposium on integrated circuits, pp 600–603

Ibrahim AB, Othman AR, Husain MN, Johal MS (2012) The cascode and cascaded techniques LNA at 5.8 GHz using T-matching network for WiMAX applications. Int J Comput Theory Eng 4(1):93–97

Jafarnejad R, Jannesaria A, Sobhib J (2017a) Pre-distortion technique to improve linearity of low noise amplifier. Microelectron J 61:95–105

Jafarnejad R, Jannesari A, Sobhi J (2017b) A linear ultra wide band low noise amplifier using pre-distortion technique. Int J Electron Commun 79:172–183

Kumar R, Kumar M, Srivastava VM (2012) Design and noise optimization for an RF low noise amplifier. Int J VLSI Des Commun Syst 3(2):165–173

Kumar R, Devi A, Sarkar A, Talukdar FA (2016) Design of 5.5 GHz linear low noise amplifier using post-distortion technique with body biasing. Microsyst Technol 22(11):2681–2690

Lee TH (1998) The design of CMOS radio-frequency integrated circuits. Cambridge University Press, Cambridge

Liao CH, Chuang HR (2003) A 5.7 GHz 0.18 nm CMOS gain-controlled differential LNA with current reuse for WLAN receiver. IEEE Microw Wirel Compon Lett 13(12):526–528

Meaamar Chye BC, Anh M, Seng YK (2009) A 3 to 8 GHz low noise CMOS amplifier. IEEE Microw Wirel Compon Lett 19(4):245–247

Nejati H, Ragheb T, Nieuwoudt A, Massoud Y (2007) Modeling and design of ultrawideband low noise amplifiers with generalized impedance matching networks. In: Proceedings of IEEE ISCAS, pp 2622–2625

Nejati H, Ragheb T, Massoud Y (2008) Analytical modeling of common-gate low noise amplifiers. In: Proceedings of IEEE ISCAS, pp 888–891

Oluwajobi FI, Wasiu L (2014) Multisim design and simulation of 2.2 GHz LNA for wireless communication. Int J VLSI Des Commun Syst 5(4):65–74

Park B, Choi S, Hong S (2010) A low noise amplifier with tunable interference rejection for 3.1 to 10.6 GHz UWB systems. IEEE Microw Wirel Compon Lett 20(1):40–42

Rastegar H, Ryu J-Y (2015) A broadband low noise amplifier with built-in linearizer in 0.13-mm CMOS process. Microelectron J 46(8):698–705

Rastegar H, Saryazdi S, Hakimi A (2013) A low power and high linearity UWB low noise amplifier (LNA) for 3.1–10.6 GHz wireless applications in 0.13 mm CMOS process. Microelectron J 44(3):201–209

Razavi Behzad (2011) RF microelectronics, 2nd edn. Prentice Hall, New York

Razavi B (2013) Design of analog CMOS integrated circuits. McGraw Hill Education Private Limited, Chennai

Shaeffer DK, Lee TH (1997) A 1.5-V, 1.5-GHz CMOS low noise amplifier. IEEE J Solid State Circuits 32(5):745–759

Singh CL, Baishnab KL, Anandini Ch (2017) Analysis and optimization of noises of an analog circuit via PSO algorithms. Microsyst Technol. https://doi.org/10.1007/s00542-017-3573-8

Wei YL, Jin JD (2009) A low power low noise amplifier for K-band applications. IEEE Microw Wirel Compon Lett 19(2):116–118

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Anandini, C., Talukdar, F.A., Singh, C.L. et al. Analysis of CMOS 0.18 μm UWB low noise amplifier for wireless application. Microsyst Technol 26, 3243–3257 (2020). https://doi.org/10.1007/s00542-018-4005-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-018-4005-0