Abstract

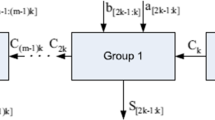

Fault tolerance is the ability of a system to retain its normal operation without failure when some part of the system fails to operate properly. It increases the wear-out time for any system at a cost of increased hardware. Fault tolerant approaches must be incorporated in any safety-critical system for continuing its job without failure even if an error occurs in the system. Adder is the most essential block in any digital architecture. In this Paper we present the design of a fault tolerant conditional sum adder with an efficient testing methodology and self-reconfiguring approach.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Biernat, J.: Fast fault-tolerant adders. International Journal Critical Computer-Based Systems 1(1/2/3), 117–127 (2010)

Koren, I.: Computer Arithmetic Algorithms. A K Peters (2011)

Lu, S.K., Wang, J.C., Wu, C.W.: C-testable design techniques for iterative logic arrays. IEEE Trans. VLSI Systems 3, 146–152 (1995)

Miczo, A.: Digital logic testing and simulation. John Wiley & Sons, New Jersey (2003)

Li, J.F., Hsu, C.C.: Efficient testing methodologies for conditional sum adders. In: Proc. Asian Test Symp., pp. 319–324 (2004)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2012 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Mukherjee, A., Dhar, A.S. (2012). Design of a Fault-Tolerant Conditional Sum Adder. In: Rahaman, H., Chattopadhyay, S., Chattopadhyay, S. (eds) Progress in VLSI Design and Test. Lecture Notes in Computer Science, vol 7373. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-31494-0_25

Download citation

DOI: https://doi.org/10.1007/978-3-642-31494-0_25

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-31493-3

Online ISBN: 978-3-642-31494-0

eBook Packages: Computer ScienceComputer Science (R0)