Abstract

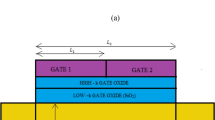

An analytical model has been examined in this work for dielectric engineered gate stack high K cylindrical junctionless nanowire ferrolectric field effect transistor (HCJNFe FET). HCJNFe FET (High K junctionless nanowire ferrolectric field effect transistor) modulated with high K dielectric HfO2 has been compared with Conventional CJNFe FET (cylindrical junctionless nanowire field effect transistor). It has been illustrated that HCJNFe FET exhibits much higher efficiency than the traditional CJNFe FET and possess excellent device performance, including low sub-threshold slope, low leakage currents, increased drain current, better transconductance gm, output conductance gd, Ion/Ioff ratio, cutoff frequency, gain frequency product (GFP), Gain transconductance frequency product (GTFP), intrinsic gain, etc. Thus, the device is suitable for high frequency applications and also for low power digital applications. The proposed device also showed moderate linearity performance for various parameters like second order harmonics (gm2), third order harmonics (gm3), extrapolated input power (IIP2), voltage intercept point (VIP2), voltage intercept point (VIP3), Intermodulation distortion (IMD3). The parabolic approximation of potential is used to predict drain current model in different operating region. Landau Khalatnikov model is used to explain the negative capacitance phenomenon because of which subthreshold slope can be reduced below 60 mV/dec. Due to negative capacitance phenomenon internal voltage amplification take place. Thus, the value of threshold voltage has been reduced. The simulated results using ATLAS 3-D simulator are coherent with the analytical results produced from the model.

Similar content being viewed by others

Data availability

Not applicable.

References

Aziz A, Ghosh S, Datta S, Gupta SK (2016) Physics-based circuit-compatible SPICE model for ferroelectric transistors. IEEE Electron Device Lett 37(6):805–808

Colinge J-P, Lee C-W, Afzalian A, Dehdashti Akhavan N, Yan R, Ferain I, Razavi P, O’Neill B, Blake A, White M, Kelleher A-M, McCarthy B, Murphy R (2010) nanowire transistors without junctions. Nat Nanotechnol 5(3):225–229

Duarte JP, Choi S-J, Moon D-I, Choi Y-K (2011a) Simple analytical bulk current model for long-channel double-gate junctionless transistors. IEEE Electron Device Lett 32(6):704–706

Duarte JP, Choi S-J, Choi Y-K (2011b) A Full-range drain current model for double-gate junction-less transistors. IEEE Trans Electron Devices 58(12):4219–4225

Enz CC, Krummenacher F, Vittoz EA (1998) An analytical MOS transistor model valid in all regions of operation and dedicated to low-voltage and low-current applications. Analog Integr Circ Sig Process 8(1):83–114

Francis P, Terao A, Flandre S (1994) Modeling of ultrathin double-Gate nMOS/SOI transistors. IEEE Trans Electron Devices 41(5):715–720

Goel A, Rewari S, Verma S, Gupta RS (2020) High-K spacer dual-metal gate stack underlap junctionless gate all around (HK-DMGS-JGAA) MOSFET for high frequency applications. Microsyst Technol 26:1697–1705

Gupta S, Steiner M, Aziz A, NarayananGupta V (2017) Device-circuit analysis of ferroelectric FETs for low-power logic. IEEE Trans Electron Devices 64(8):3092–3100

Intekhab Amin S, Sarin RK (2013) Junctionless transitor: a review. In: International Conference on Computational Intelligence and Information Technology

Kansal M, Sharma SC (2022a) Plasma-based nanoarchitectonics for vertically aligned dual-metal carbon nanotube field effect transistor (VA-DMCNFET) device: effect of plasma parameters on transistor properties. Appl Phys A 128:1–11

Kansal M, Sharma SC (2022b) Performance evaluation & linearity distortion analysis for plasma-assisted dualmaterial carbon nanotube field effect transistor with a SiO2-HfO2 stacked gate-oxide structure (DM-SGCNFET). Silicon

Kansal M, Sharma SC (2022c) Exploration of novel hafnium oxide (HfO2) based plasma-assisted gate all around carbon nanotube FET (GAA-CNTFET) for high sensing applications. ECS J Solid State Sci Technol 11(10):101002

Kansal M, Sharma SC (2022d) Impact of PECVD characteristics on metrics of a plasma-assisted vertically aligned carbon nanotube FET (VA-CNTFET) device. In: 2022d IEEE International Conference on Nanoelectronics, Nanophotonics, Nanomaterials, Nanobioscience & Nanotechnology (5NANO)

Khan AI, Radhakrishna U, Salahuddin S, Antoniadis D (2017) Work function engineering for performance improvement in leaky negative capacitance FETs. IEEE Electron Device Lett 38(9):1335–1338

Kobayashi M, Hiramoto T (2015) Device design guideline for slope ferroelectric FET using negative capacitance in sub-0.2 operation. In: Operation Speed, Material Requirement and Energy Efficiency” pp. T212-T213, IEEE 2015

Kranti A, Haldar S, Gupta RS (2001) Analytical model for threshhold voltage and I-V characteristics of fullt depleted short channel cylindrical/surrounding gate MOSFET. Microelectron Eng 56:241–259

Kwon D, Chatterjee K, Tan AJ, Yadav AK, Zhou H, Sachid AB, Dos Reis R, Hu C, Salahuddin S (2017) Improved subthreshold swing and short channel effect in FDSOI n-channel negative capacitance field effect transistors. IEEE Electron Device Lett 39(2):300–303

Li Y, Kang Y, Gong X (2017) Evaluation of negative capacitance ferroelectric MOSFET for analog circuit applications. IEEE Trans Electron Devices 64(10):4317–4321

Mehta H, Kaur H (2016) Modeling and simulation study of novel Double Gate Ferroelectric Junction-less (DGFJL) transistor. Superlattices Microstruct 97:536–547

Mehta H, Kaur H (2018) Impact of Gaussian doping profile and negative capacitance effect on double-gate junction-less transistors (DGJLTs). IEEE Trans Electron Devices 65(7):2699–2706

Mehta M, Kaur H (2019) Subthreshold analytical model for dual-material double gate ferroelectric field effect transistor (DMGFeFET). Semicond Sci Technol 34(6):065008

Mohsenifar S, Shahrokhabadi M (2015) Gate stack high-Κ materials for Si-based MOSFETs past, present, and futures. Microelectron Solid State Electron 4(1):12–24

Moldovan O, Cerdeira A, Jiménez A, Raskin J-P, Kilchytska V, Flandre D, Collaert N, Iñiguez B (2007) Compact model for highly-doped double-gate SOI MOSFETs targeting baseband analog applications. Solid State Electron 51:655–661

Müller J, Polakowski P, Mueller S, Mikolajick T (2015) Ferroelectric hafnium oxide based materials and devices: assessment of current status and future prospects. ECS J Solid State Sci Technol 4:N30

Nandy S, Srivastava S, Rewari S, Nath V, Gupta RS (2019) Dual metal Schottky barrier asymmetric gate stack cylindrical gate all around (DM-SB-ASMGS-CGAA) MOSFET for improved analog performance for high frequency application. Microsyst Technol. https://doi.org/10.1007/s00542-019-04577-y

Neeraj AG, Sharma S, Rewari S, Gupta RS (2022) SiC Based analytical model for Gate-Stack Dual Metal (DM) nanowire FET with enhanced analog performance. Int J Numer Model Electron Netw Devices Fields 35(4):e2986

Nirmali, Kumar V, Samuel PC , Shruthi, Thomas DM, Kumar M (2011) Analysis of dual gate Mosfets using high K Dielectrics. In: 3rd International conference on electronics computer technology, IEEE, vol 1, pp 20–25

Pahwa G, Dutta T, Agarwal A, Chauhan YS (2017) Compact model for ferroelectric negative capacitance transistor with MFIS structure. IEEE Trans Electron Devices 64(3):1366–1374

Pahwa G, Agarwal A, Chauhan YS (2018) Numerical investigation of short-channel effects in negative capacitance MFIS and MFMIS transistors: Subthreshold behavior. IEEE Trans Electron Devices 65(11):5130–5136

Park J-T, Colinge J-P (2022) Multiple Gate SOI MOSFETs: device design guidelines. IEEE Trans Electron Devices 49(12):2222–2229

Rollo T, Wang H, Han G, Esseni D (2018) A simulation based study of NC-FETs design: off-state versus on-state perspective. In: 2018 IEEE International Electron Devices Meeting (IEDM), pp. 9–5. IEEE, 2018

Roy K, Mahmoodi H, Mukhopadhyay S, Ananthan H, Bansal A, Cakici T (2005) Double gate SOI devices for low power and high performance applications. In: IEEE International Conference on computer aided design

Roy S, Chakarabarty P, Pally R (2022) Assessing RF/AC performance and linearity analysis of NCFET in CMOS compatible thin body FDSOI. IEEE Trans Electron Devices 69(2):475–481

Saha R (2021) Simulation study on ferrolectric layer thickness dependence RF/Analog and linearity parameters in ferrolectric tunnel junction (TFET). Microelectrocn J 113:105081

Sahu SR, Agrawal RS, Balwani SM (2012) Review of junctionless transistor using CMOS technology and MOSFETs. In: National Conference on innovative paradigms in Engineering &Technology

Saha R, Bhowmick B, Baishya S (2021) Study on impact of ferroelectric layer thickness on RF/ analog and linearity parameters in ferroelectric-FinFET. Int J RF Microwave Comput Aided Eng

Salmani-Jelodar M, Ilatikhameneh H, Kim S, Sarangapani GK (2014) Optimum High-k oxide for the best performance of ultra-scaled double-gate MOSFETs. IEEE Trans Nanotechnol J 13(9):904–910

Solankia T, Parmar N (2011) A Review paper: A Comprehensive study of Junctionless transistor. In: National Conference on Recent Trends in Engineering & Technology

Suzuki K, Tanaka T, Tosaka Y, Horie H, Arimoto Y (1993) Scaling theory for double gate SO1 MOSFET’s. IEEE Trans Electron Devices 40(12):2326–2329

Thakur RR, Singh P (2019) Performance reliability of ultra-thin Si-SiO2, Si-Al2O3, Si-ZrO2 and Si-HfO2 interface in rectangular steep retrograded nano-regimes devices. Microelectron Reliab 96:21–28

Young KK (1989) Analysis of conduction in fully depleted SOI MOSFETs. IEEE Trans Electron Devices 36(3):504–506

Yu C, Yuan JS, Yang H (2004) MOSFET linearity performance degradation subject to drain and gate voltage stress. IEEE Trans Device Mater Reliab 4(4):681–689

Yu B, Lu H, Liu M, Taur Y (2007) Explicit continuous model for double gate and surrounding gate MOSFET. IEEE Tran on Electronic Device 54(10):2715–2722

Zhang Z, Xu G, Zhang Q, Hou Z, Liu J (2019) FinFET with improved subthreshold swing and drain current using 3-nm ferroelectric Hf 0.5 Zr 0.5 O 2. IEEE Electron Device Lett 40(3):367–370

Acknowledgements

Authors are gratified to the Director, Maharaja Agrasen Institute of Technology for providing necessary facilities to carry out this research work.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Garg, S., Kaur, J., Goel, A. et al. Physics based analytical modeling and simulation of Cylindrical Junctionless Nanowire Ferroelectric field effect transistor (CJNFe-FET) for enhanced analog performance. Microsyst Technol 29, 1417–1429 (2023). https://doi.org/10.1007/s00542-023-05468-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-023-05468-z