Abstract

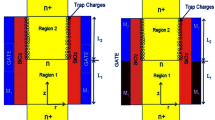

This paper presents investigation about the drain current parameters of Surrounding Gate MOSFET (SG MOSFET) with junction and junctionless transistor. The junctionless SG MOSFET (JLSG MOSFET) exhibits more current available at low voltage but junction based SG MOSFET exhibits less current at same voltage but depends on parameters. The junction based devices are less costly. Device length also improved in JLSG MOSFET. General variable issues like oxide thickness, channel length and doping concentration are also discussed.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Srivastava MA, Kumar A, Rai S (2017) Analytical model and performance investigation of electric potential for junctionless cylindrical surround gate (JLCSG) MOSFET. In: 4th international conference signal processing and integrated networks 2017, pp 256–261. IEEE

Pratap Y, Halder S, Gupta R, Gupta M (2014) Performance evolution and reliability issues of junctionless CSG MOSFET for RFIC Design. IEEE Trans Device Mater Reliab 14(1):418–425

Trivedi N, Kumar M, Halder S, Deswal S, Gupta M, Gupta R (2017) Charge plasma technique based dopingless accumulation mode junctionless cylindrical surrounding gate MOSFET: analog performance improvement. Appl Phys A Mater Sci Process Cross Mark 123:564. Springer

Duarte J, Choi S, Moon D, Choi Y (2011) Sensitivity of threshold voltage to nanowire width variation in junctionless transistor. IEEE Electron Device Lett 32(2):125–127

Ansari L, Feldman B, Fags G, Colinge J, Career J (2010) Simulation of junctionless si nanowire transistors with 3 nm gate length. Appl Phys Lett 97(6): 062105-1–062105-3

Gnudi A, Reggiani S, Gnani E, Baccarani G (2012) Analysis of threshold voltage variability due to random dopant fluctuations in junctionless FETs. IEEE Electron Device Lett 33(3):3336–3338

Auth C, Plummer J (1997) Scaling theory for cylindrical, fully depleted, surrounding gate MOSFET’s. IEEE Electro Device Lett. 18(2):74–76

Sallese J, Chevillon N, Lallement C, Iniguez B, Pregaldiny F (2011) Charge based modeling of junctionless double gate field effect transistors. IEEE Electron Devices 58(8):2628–2637

Gnani A, Gnudi A, Reggiani S, Baccarani G (2011) Theory of junctionless nanowire FET. IEEE Trans Electron Device 58(9):2903–2910

Agarwal A, Sharma R, Mani P (2018) Analytical modeling electrical conduction of nano scaled surrounding gate MOSFET. In: International conference on micro-electronics and telecommunication engineering (ICMETE) 2018, pp 331–334. IEEE, Ghaziabad

Agarwal A, Sharma R, Mani P (2018) A study of characterization of surrounding gate MOSFET. VSRD Int J Techn NON Tech Res 9(1):67–70

Christopher P, James P (1998) A simple model for threshold voltage of surrounding gate MOSFET’s. IEEE Trans Electron Devices 45(11):2381–2383

Srivastava V, Yadav K, Singh G (2013) Explicit model of cylindrical surrounding gate MOSFET. WSEAS Trans Circ Syst 12(3):81–90

Colinge JP, Lee CW, Afzalian A (2010) Nanowire transistors without junctions. Nat Nanotechnol 5(3):225–229

Guangxi H, Xiang P, Ding Z, Liu R, Wang L, Tang T (2014) Analytical models for electric potential, threshold voltage and subthreshold swing of junctionless surrounding gate transistors. IEEE Trans Electron Devices 61(3):688–694

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2020 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Agarwal, A., Sharma, R.L., Mani, P. (2020). An Investigation on Drain Current of Junction and Junctionless Surrounding Gate MOSFET. In: Sharma, D.K., Balas, V.E., Son, L.H., Sharma, R., Cengiz, K. (eds) Micro-Electronics and Telecommunication Engineering. Lecture Notes in Networks and Systems, vol 106. Springer, Singapore. https://doi.org/10.1007/978-981-15-2329-8_60

Download citation

DOI: https://doi.org/10.1007/978-981-15-2329-8_60

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-15-2328-1

Online ISBN: 978-981-15-2329-8

eBook Packages: EngineeringEngineering (R0)