Abstract

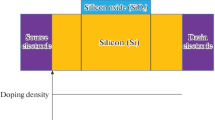

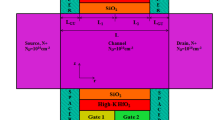

Research on double-gate MOSFET has already exhibited several novel solutions of existing problems like reducing leakage current or short-channel effect. For both long-channel structure or microscopic devices, the role of the bottom-gate becomes more critical for making higher ON-to-OFF current ratio, and therefore, individual-gate architecture becomes more popular than tied-gate architecture owing to the possibility of individual tuning. Junctionless devices come into the limelight due to better mobility control than the other DG configurations, and considered the subject of investigation in the last few years. The current chapter investigates the effect of negative bottom gate voltage on the analog and RF performances of Asymmetric Junctionless Dual Material Double Gate (AJDMDG) MOSFET. TCAD device simulator was used to investigate the effect of negative bottom gate voltage on analog and RF parameters. The results show that utilizing a low value of the work function of the bottom gate terminal improved the analog and RF performance.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

International technology roadmap for semiconductors 2009 Edition and 2010 Update. http://www.itrs.net. Accessed 2018

Mohsenifar S, Shahrokhabadi MH (2015) Gate stack high-κ materials for Si-based MOSFETs past, present, and futures. Microelectron Solid State Electron 4:12–24

Datta S (2013) Recent advances in high performance CMOS transistors: from planar to non-planar. Electrochem Soc Interfac 22:41–46. https://doi.org/10.1149/2.F04131if

Chiang TK (2016) A short-channel-effect-degraded noise margin model for junctionless double-gate MOSFET Working on subthreshold CMOS logic gates. IEEE Trans Electron Devices 63

Hong S (2019) Compact charge modeling of double-gate MOSFETs considering the density-gradient equation. IEEE J Electron Devices Soc 7

Xie Q, Wang Z, Taur Y (2017) Analysis of short-channel effects in junctionless DG MOSFETs. IEEE Trans Electron Devices 64:3511–3514

Gnudi A, Reggiani S, Gnani E, Baccarani G (2013) Semianalytical model of the subthreshold current in short-channel junctionless symmetric double-gate field-effect transistors. IEEE Trans Electron Devices 60:1342–1348

Bari S, De D, Sarkar A (2015) Effect of gate engineering in JLSRG MOSFET to suppress SCEs: an analytical study. Physica E Low-dimens Syst Nanostruct 67:143–151

Biswal SM, Baral B, De D, Sarkar A (2015) Analytical subthreshold modeling of dual material gate engineered nano-scale junctionless surrounding gate MOSFET considering ECPE. Superlattices Microstruct 82:103–112

Reddy GV, Kumar MJ (2005) A new dual-material double-gate (DMDG) nanoscale SOI MOSFET-two-dimensional analytical modeling and simulation. IEEE Trans Nanotechnol 4:260–268

Singh J, Gadi V, Kumar MJ (2016) Modeling a dual-material-gate junctionless FET under full and partial depletion conditions using finite-differentiation method. IEEE Trans Electron Devices 63:2282–2287

Kumari V, Modi N, Saxena M, Gupta M (2015) Theoretical investigation of dual material junctionless double gate transistor for analog and digital performance. IEEE Trans Electron Devices 62:2098–2105

Taur Y (2000) An analytical solution to a double-gate MOSFET with undoped body. IEEE Electron Device Lett 21(5):241–247

Taur Y (2001) Analytic solutions of charge and capacitance in symmetric and asymmetric double-gate MOSFETs. IEEE Trans Electron Devices 48(12):2861–2869

Ortiz-Conde A, Garcia-Sanchez FJ, Muci J (2005) Rigorous analytic solution for the drain current of undoped symmetric dual-gate MOSFETs. Solid State Electron 49(4):640–647

Ortiz-Conde A, García-Sánchez FJ, Muci J, Malobabic S, Liou JJ (2007) A review of core compact models for undoped double-gate SOI MOSFETs. IEEE Trans Electron Devices 54(1):131–140

Roy K, Chowdhury AR, Deyasi A, Sarkar A (2019) Computing surface potential and drain current in nanometric double-gate MOSFET using Ortiz-Conde model. In: Advances in intelligent systems and computing book serie: contemporary advances in innovative and applicable information technology, vol 812, pp 41–47

Chakraborty D, Bhowmick S, Deyasi A (2018) Computing surface potential of double gate MOSFET for both free and doped carrier concentrations. In: IEEE 2nd international conference on electronics, materials engineering & nano-technology, Kolkata, India, pp 1–4

Nath A, Khanam F, Mukhopadhyay S, Deyasi A (2021), Surface potential computation for asymmetric Si–Si1−xGex ID-DG MOSFET following Ortiz-Conde model. In: Lecture notes in electrical engineering: nanoelectronics, circuits and communication systems, vol 692, pp 239–246

Vimala P, Balamurugan NB (2012) Quantum mechanical compact modeling of symmetric double-gate MOSFETs using variational approach. J Semicond 33(3):034001

Deyasi A, Chowdhury AR, Roy K, Sarkar A (2018) Effect of high-K dielectric on drain current of ID-DG MOSFET using Ortiz-Conde model. In: IEEE electron devices Kolkata conference, pp 176–181

Chakraborty R, Mondal D, Deyasi A (2020) Investigating effect of structural parameters on static characteristics of ultrathin DG MOSFET using Taur’s model. In: Lecture notes in networks and systems: information, photonics and communication, vol 79, Chapter 2, pp 11–19

Biswas K, Sarkar A, Sarkar CK (2015) Impact of barrier thickness on Analog, RF and Linearity performance of nanoscale DG heterostructure MOSFET. Superlattices Microstruct 86:95–104

Sarkar A, Sarkar CK (2013) RF and analogue performance investigation of DG tunnel FET. Int J Electron Lett 1:210–217

Biswas K, Sarkar A, Sarka CK (2018) Fin shape influence on analog and RF performance of junctionless accumulation-mode bulk FinFETs. Microsyst Technol 24:2317–2324

Sarkar A, De S, Dey A, Sarkar CK (2011) A new analytical subthreshold model of SRG MOSFET with analogue performance investigation. Int J Electron 99:267–283

Basak A, Chanda M, Sarkar A (2019) Drain current modelling of unipolar junction dual material double-gate MOSFET (UJDMDG) for SoC applications. Microsyst Technol 27(11):3995–4005

Koley K, Syamal B, Kundu A, Mohankumar N, Sarkar CK (2012) Subthreshold analog/RF performance of underlap DG FETs with asymmetric source/drain extensions. Microelectron Reliab 52:2572–2578

Koley K, Dutta A, Syamal B, Saha SK, Sarkar CK (2013) Subthreshold analog/RF performance enhancement of underlap DG FETs with high- K spacer for low power applications. IEEE Trans Electron Devices 60:63–69

Chebaki E, Djeffal F, Hichem F, Bentrcia T (2016) Improved analog/RF performance of double gate junctionless MOSFET using both gate material engineering and drain/source extensions. Superlattices Microstruct 92:80–91

Sharma RK, Bucher M (2012) Device design engineering for optimum analog/RF performance of nanoscale DG MOSFETs. IEEE Trans Nanotechnol 11:992–998

Roy NC, Gupta A, Rai S (2015) Analytical surface potential modeling and simulation of junctionless double gate (JLDG) MOSFET for ultra-low-power analog/RF circuits. Microelectron J 46:916–922

Ghosh D, Pariha MS, Armstrong GA, Kranti A (2012) High-performance junctionless MOSFETs for ultralow-power analog/RF applications. IEEE Electron Device Lett 33:1477–1479

Deyasi A, Sarkar A, Roy K, Chowdhury AR (2021) Effect of high-K dielectric on differential conductance and transconductance of ID-DG MOSFET following Ortiz-Conde model. Microsyst Technol 27(11):3967–3975

Deyasi A, Chakraborty R, Mondal D, Pramanik N, Mukhopadhyay S (2021) Analytical investigation of transconductance and differential conductance of ultrathin ID-DG MOSFET with gradual channel approximation. In: Lecture notes in electrical engineering: fifth international conference on microelectronics, computing and communication systems, vol 748, pp 117–126

Mukhopadhyay S, Ray P, Deyasi A (2020) Computing gate asymmetric effect on drain current of DG-MOSFET following Ortiz-Conde model. In: IEEE national conference on emerging trends on sustainable technology and engineering applications, pp 1–5

Sarkar A, De S, Dey A et al (2012) Analog and RF performance investigation of cylindrical surrounding-gate MOSFET with an analytical pseudo-2D model. J Comput Electron 11:182–195

Sarkar A (2014) Study of RF performance of surrounding gate MOSFET with gate overlap and underlap. Adv Natl Sci Nanosci Nanotechnol 5

Bhowmick S, Chakraborty D, Deyasi A (2017) Computation of electrical parameters for single-gate high-K nanoscale MOSFET with cylindrical geometry. In: Advances in intelligent systems and computing: international conference on modelling and simulation, vol 749, pp 47–53

Deyasi A, Mukherjee S, Bhattacharjee AK, Sarkar A (2020) Classification of single and double-gate nanoscale MOSFET with different dielectrics from electrical characteristics using soft computing techniques. Int J Inf Technol 12(1):165–174

Basak A, Sarkar A (2020) Impact of back gate work function for enhancement of analog/RF performance of AJDMDG Stack MOSFET. Solid State Electron Lett 2:117–123

Abdullah G (2015) ATLAS device simulation software, Santa Clara, CA, USA

Goudan T, Miljanović V, Schmeiser C (2006) On the Shockley-Read-Hall model: generation-recombination in semiconductors. SIAM J Appl Math

Ringhofer C, Schmeiser C (1989) An approximate newton method for the solution of the basic semiconductor device equations. SIAM J Numer Anal 26:507–516

Ferron A, Cottle B, Curatola G, Fiori G, Guichard E (2004) Schrödinger approach and density gradient model for quantum effects modeling. J Process Device Eng

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2022 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this chapter

Cite this chapter

Basak, A., Deyasi, A., Sarkar, A. (2022). Impact of Negative Bottom Gate Voltage for Improvement of RF/Analog Performance in Asymmetric Junctionless Dual Material Double Gate MOSFET. In: Acharyya, A., Biswas, A., Inokawa, H. (eds) New Horizons in Millimeter-Wave, Infrared and Terahertz Technologies. Lecture Notes in Electrical Engineering, vol 953. Springer, Singapore. https://doi.org/10.1007/978-981-19-6301-8_12

Download citation

DOI: https://doi.org/10.1007/978-981-19-6301-8_12

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-19-6300-1

Online ISBN: 978-981-19-6301-8

eBook Packages: Physics and AstronomyPhysics and Astronomy (R0)