Abstract

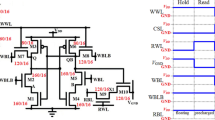

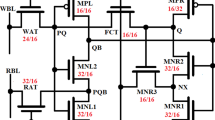

This work presents a new bit-interleaving low-power 11T subthreshold SRAM cell with the Data-Dependent Partial-Feedback Cutting to improve the write ability. The isolated read path of 11T enhances the read static noise margin (RSNM) which is equivalent to that of its hold SNM (HSNM), while the incorporated PMOS stacking in each of the inverter helps to reduce the leakage power of the cell. The half-select free behavior of the proposed 11T cell facilitates the bit-interleaving architecture of memory array that reduces the multi-bits error occurrence in a single word of data, and thus enhance the soft error tolerance. Using the proposed cell, a four-input FPGA lookup table (LUT) has been implemented working on 0.4V supply, which consumes 0.59\(\times \) less leakage power as compared to that of 6T LUT. Finally, a two adjacent bits error correction technique is also suggested to incorporate with the proposed bit-interleaving 11T array, so that the effect of soft error can almost be neglected. It consumes comparable leakage and read access energy to that of one-bit error correcting conventional hamming code.

Supported by Special Manpower Development Program for Chips to System Design (SMDP-C2SD) research project of Department of Electronics and Information Technology (DEITY), Government of India.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Safarulla, I.M., Manilal, K.: Design of soft error tolerance technique for FPGA based soft core processors. In: 2014 International Conference on Advanced Communication Control and Computing Technologies (ICACCCT), pp. 1036–1040. IEEE (2014)

Ullah, Z., Jaiswal, M.K., Cheung, R.C.: Z-TCAM: an SRAM-based architecture for TCAM. IEEE Trans. Very Large Scale (VLSI) Integr. Syst. 23(2), 402–406 (2015)

Sharma, V., Gopal, M., Singh, P., Vishvakarma, S.K.: A 220 mV robust read-decoupled partial feedback cutting based low-leakage 9T SRAM for Internet of Things (iot) applications. AEU-Int. J. Electron. Commun. 87, 144–157 (2018)

Roy, K., Prasad, S.C.: Low-power CMOS VLSI Circuit Design. Wiley, Hoboken (2009)

Sharma, V., Kumar, S.: Design of low-power CMOS cell structures using subthreshold conduction region. Int. J. Sci. Eng. Res. 2(2), 29–34 (2011)

Chang, M.-F., et al.: A sub-0.3 V area-efficient l-shaped 7T SRAM with read bitline swing expansion schemes based on boosted read-bitline, asymmetric read-port, and offset cell VDD biasing techniques. IEEE J. Solid-State Circuits 48(10), 2558–2569 (2013)

Pal, S., Islam, A.: 9-T SRAM cell for reliable ultralow-power applications and solving multibit soft-error issue. IEEE Trans. Device Mater. Reliab. 16(2), 172–182 (2016)

Andrei, P., Oniciuc, L.: Suppressing random dopant-induced fluctuations of threshold voltages in semiconductor devices. J. Appl. Phys. 104(10), 104508 (2008)

Chang, L., et al.: An 8T-SRAM for variability tolerance and low-voltage operation in high-performance caches. IEEE J. Solid-State Circuits 43(4), 956–963 (2008)

Chang, M.-F., Chang, S.-W., Chou, P.-W., Wu, W.-C.: A 130 mV SRAM with expanded write and read margins for subthreshold applications. IEEE J. Solid-State Circuits 46(2), 520–529 (2011)

Wang, B., Nguyen, T.Q., Do, A.T., Zhou, J., Je, M., Kim, T.T.-H.: Design of an ultra-low voltage 9T SRAM with equalized bitline leakage and cam-assisted energy efficiency improvement. IEEE Trans. Circuits Syst. I: Regul. Pap. 62(2), 441–448 (2015)

Lo, C.-H., Huang, S.-Y.: PPN based 10T SRAM cell for low-leakage and resilient subthreshold operation. IEEE J. Solid-State Circuits 46(3), 695–704 (2011)

Chiu, Y.-W., et al.: 40 nm bit-interleaving 12T subthreshold SRAM with data-aware write-assist. IEEE Trans. Circuits Syst. I: Regul. Pap. 61(9), 2578–2585 (2014)

Kim, J., Mazumder, P.: A robust 12T SRAM cell with improved write margin for ultra-low power applications in 40 nm CMOS. Integr. VLSI J. 57, 1–10 (2017)

Jahinuzzaman, S.M., Rennie, D.J., Sachdev, M.: A soft error tolerant 10T sram bit-cell with differential read capability. IEEE Trans. Nucl. Sci. 56(6), 3768–3773 (2009)

Lage, C., et al.: Soft error rate and stored charge requirements in advanced high-density SRAMS. In: International Electron Devices Meeting, 1993. IEDM 1993 Technical Digest, pp. 821–824. IEEE (1993)

Hazucha, P., et al.: Neutron soft error rate measurements in a 90-nm CMOS process and scaling trends in sram from 0.25-/spl mu/m to 90-nm generation. In: IEEE International Electron Devices Meeting, 2003. IEDM 2003 Technical Digest, p. 21.5. IEEE (2003)

Chang, I.J., Kim, J.-J., Park, S.P., Roy, K.: A 32 kb 10T sub-threshold SRAM array with bit-interleaving and differential read scheme in 90 nm CMOS. IEEE J. Solid-State Circuits 44(2), 650–658 (2009)

Wen, L., Duan, Z., Li, Y., Zeng, X.: Analysis of a read disturb-free 9T sram cell with bit-interleaving capability. Microelectron. J. 45(6), 815–824 (2014)

Seevinck, E., List, F.J., Lohstroh, J.: Static-noise margin analysis of MOS SRAM cells. IEEE J. Solid-State Circuits 22(5), 748–754 (1987)

Li, J., Reviriego, P., Xiao, L., Argyrides, C., Li, J.: Extending 3-bit burst error-correction codes with quadruple adjacent error correction. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 26(2), 221–229 (2018)

Li, J., Xiao, L., Reviriego, P., Zhang, R.: Efficient implementations of 4-bit burst error correction for memories. IEEE Trans. Circ. Syst. II: Express Briefs 65(12), 2037–2041 (2018)

Acknowledgment

The authors would like to thank Special Manpower Development Program for Chips to System Design (SMDP-C2SD) research project of Department of Electronics and Information Technology (DEITY) under Ministry of Communication and Information Technology, Government of India to provide the lab facilities.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2019 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Sharma, V., Bisht, P., Dalal, A., Chouhan, S.S., Jattana, H.S., Vishvakarma, S.K. (2019). A Write-Improved Half-Select-Free Low-Power 11T Subthreshold SRAM with Double Adjacent Error Correction for FPGA-LUT Design. In: Rajaram, S., Balamurugan, N., Gracia Nirmala Rani, D., Singh, V. (eds) VLSI Design and Test. VDAT 2018. Communications in Computer and Information Science, vol 892. Springer, Singapore. https://doi.org/10.1007/978-981-13-5950-7_46

Download citation

DOI: https://doi.org/10.1007/978-981-13-5950-7_46

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-13-5949-1

Online ISBN: 978-981-13-5950-7

eBook Packages: Computer ScienceComputer Science (R0)