Abstract

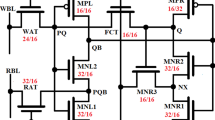

Portable applications and battery-operated devices require highly reliable, stable, and low-power nanometer-sized embedded cache static random access memory (SRAM) cells. The conventional 6-transistor (6 T) SRAM cell and its variants suffer from malfunctioning during the read/write operations, and instability, and are vulnerable to the multi-bit soft-error rate at scaled technology node and low supply voltage (VDD). In this regard, this paper proposes an 12 T SRAM cell with reliable functioning and reduced multi-bit soft-errors appropriate for low-power portable applications. This cell performs single-end bitline decoupled read operation and write data-dependent feedback-cutting-aware differential write operation to improve the read static noise margin (RSNM) and write static noise margin (WSNM), respectively. The presence of stack transistors in the cell core and read path, and also high virtual ground (VGND) minimize the leakage power dissipation. The proposed cell is compared with other state-of-the-art SRAM cells at VDD = 0.7 V and under harsh process, voltage, and temperature (PVT) variations. It offers at least 1.18X higher RSNM, 1.27X higher WSNM, and 2.02X lower leakage power dissipation. It also shows the second-best read power and incurs a penalty in write power. This cell shows at least 1.17X, 1.32X, and 1.04X smaller spread in read delay, RSNM, and WSNM, respectively, when subjected to PVT variations. In addition, the proposed cell eliminates the write half-select disturbance by employing a separate gate to drive the access transistors and thus column-interleaving structure and error correction coding can be applied to reduce multiple-bit upset and increase soft-error immunity. The soft-error in the proposed cell is reduced by at least 1.37X in critical charge. Generally, the proposed cell offers the best overall performance among all the compared cells by showing the highest proposed figure of merit.

Similar content being viewed by others

Data availability

The data that support the finding of this study are available from the corresponding author upon reasonable request.

References

Pal, S., Bose, S., Ki, W.-H., & Islam, A. (2019). Half-select-free low-power dynamic loop-cutting write assist SRAM cell for space applications. IEEE Transactions on Electron Devices, 67, 80–89.

Lorenzo, R., & Pailly, R. (2020). Single bit-line 11T SRAM cell for low power and improved stability. IET Computers & Digital Techniques, 14, 114–121.

Kulkarni, J. P., & Roy, K. (2011). Ultralow-voltage process-variation-tolerant Schmitt-trigger-based SRAM design. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 20, 319–332.

Ataei, S., Stine, J. E., & Guthaus, M. R. (2016). A 64 kb differential single-port 12T SRAM design with a bit-interleaving scheme for low-voltage operation in 32 nm SOI CMOS. In 2016 IEEE 34th international conference on computer design (ICCD) (499–506).

Sharma, V., Gopal, M., Singh, P., Vishvakarma, S. K., & Chouhan, S. S. (2019). A robust, ultra low-power, data-dependent-power-supplied 11T SRAM cell with expanded read/write stabilities for internet-of-things applications. Analog Integrated Circuits and Signal Processing, 98, 331–346.

Alouani, I., Elsharkasy, W. M., Eltawil, A. M., Kurdahi, F. J., & Niar, S. (2017). AS8-static random access memory (SRAM): Asymmetric SRAM architecture for soft error hardening enhancement. IET Circuits, Devices & Systems, 11, 89–94.

Jahinuzzaman, S. M., Sharifkhani, M., & Sachdev, M. (2009). An analytical model for soft error critical charge of nanometric SRAMs. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 17, 1187–1195.

Pal, S., & Islam, A. (2016). 9-T SRAM cell for reliable ultralow-power applications and solving multibit soft-error issue. IEEE Transactions on Device and Materials Reliability, 16, 172–182.

Calhoun, B. H., & Chandrakasan, A. P. (2007). A 256-kb 65-nm sub-threshold SRAM design for ultra-low-voltage operation. IEEE Journal of Solid-State Circuits, 42, 680–688.

Ahmad, S., Gupta, M. K., Alam, N., & Hasan, M. (2017). Low leakage single bitline 9 t (sb9t) static random access memory. Microelectronics Journal, 62, 1–11.

Sharma, V., Vishvakarma, S., Chouhan, S. S., & Halonen, K. (2018). A write-improved low-power 12T SRAM cell for wearable wireless sensor nodes. International Journal of Circuit Theory and Applications, 46, 2314–2333.

Wang, B., Nguyen, T. Q., Do, A. T., Zhou, J., Je, M., & Kim, T.T.-H. (2014). Design of an ultra-low voltage 9T SRAM with equalized bitline leakage and CAM-assisted energy efficiency improvement. IEEE Transactions on Circuits and Systems I: Regular Papers, 62, 441–448.

Islam, A., & Hasan, M. (2012). A technique to mitigate impact of process, voltage and temperature variations on design metrics of SRAM Cell. Microelectronics Reliability, 52, 405–411.

Abbasian, E., Gholipour, M., & Birla, S. (2022) A single-bitline 9T SRAM for low-power near-threshold operation in FinFET technology. Arabian Journal for Science and Engineering, pp. 1–17.

Abbasian, E., Mani, E., Gholipour, M., Karamimanesh, M., Sahid, M., & Zaidi, A. (2022). A schmitt-trigger-based low-voltage 11 T SRAM cell for low-leakage in 7-nm FinFET technology. Circuits, Systems, and Signal Processing, 41(6), 3081–3105.

Abbasian, E., Gholipour, M., & Izadinasab, F. (2021). Performance evaluation of GNRFET and TMDFET devices in static random access memory cells design. International Journal of Circuit Theory and Applications, 49, 3630–3652.

Abbasian, E., & Gholipour, M. (2021). Design of a Schmitt-trigger-based 7T SRAM cell for variation resilient low-energy consumption and reliable internet of things applications. AEU-International Journal of Electronics and Communications, 138, 153899.

Abbasian, E., & Gholipour, M. (2022). Design of a highly stable and robust 10T SRAM cell for low-power portable applications. Circuits, Systems, and Signal Processing, 1–19.

Abbasian, E., Birla, S., & Mojaveri Moslem, E. (2022). Design and investigation of stability-and power-improved 11T SRAM cell for low-power devices. International Journal of Circuit Theory and Applications, 50(11), 3827–3845.

Abbasian, E., Birla, S., & Gholipour, M. (2022). A 9T high-stable and low-energy half-select-free SRAM cell design using TMDFETs. Analog Integrated Circuits and Signal Processing, pp. 1–9, 2022.

Abbasian, E., Birla, S., & Gholipour, M. (2022) Ultra-low-power and stable 10-nm FinFET 10T sub-threshold SRAM. Microelectronics Journal, p. 105427.

Cho, K., Park, J., Oh, T. W., & Jung, S.-O. (2020). One-sided schmitt-trigger-based 9T SRAM cell for near-threshold operation. IEEE Transactions on Circuits and Systems I: Regular Papers, 67, 1551–1561.

Oh, T. W., Jeong, H., Kang, K., Park, J., Yang, Y., & Jung, S.-O. (2016). Power-gated 9T SRAM cell for low-energy operation. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 25, 1183–1187.

Ahmad, S., Gupta, M. K., Alam, N., & Hasan, M. (2016). Single-ended Schmitt-trigger-based robust low-power SRAM cell. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 24, 2634–2642.

Lorenzo, R., & Paily, R. Half‐selection disturbance free 8T low leakage SRAM cell. International Journal of Circuit Theory and Applications.

Tu, M.-H., Lin, J.-Y., Tsai, M.-C., Lu, C.-Y., Lin, Y.-J., Wang, M.-H., et al. (2012). A single-ended disturb-free 9T subthreshold SRAM with cross-point data-aware write word-line structure, negative bit-line, and adaptive read operation timing tracing. IEEE Journal of Solid-State Circuits, 47, 1469–1482.

Abbasian, E., & Gholipour, M. (2021). Single-ended half-select disturb-free 11T static random access memory cell for reliable and low power applications. International Journal of Circuit Theory and Applications, 49, 970–989.

Abbasian, E., Izadinasab, F., & Gholipour, M. (2022). A reliable low standby power 10T SRAM cell with expanded static noise margins. IEEE Transactions on Circuits and Systems I: Regular Papers.

Abbasian, E., & Gholipour, M. A low‐leakage single‐bitline 9T SRAM cell with read‐disturbance removal and high writability for low‐power biomedical applications. International Journal of Circuit Theory and Applications.

Kulkarni, J. P., Kim, K., & Roy, K. (2007). A 160 mV robust Schmitt trigger based subthreshold SRAM. IEEE Journal of Solid-State Circuits, 42, 2303–2313.

Sanvale, P., Gupta, N., Neema, V., Shah, A. P., & Vishvakarma, S. K. (2019). An improved read-assist energy efficient single ended PPN based 10T SRAM cell for wireless sensor network. Microelectronics Journal, 92, 104611.

Abbasian, E., & Gholipour, M. (2022). Improved read/write assist mechanism for 10‐transistor static random access memory cell. International Journal of Circuit Theory and Applications.

Lu, C.-Y., Chuang, C.-T., Jou, S.-J., Tu, M.-H., Wu, Y.-P., Huang, C.-P., et al. (2014). A 0.325 V, 600-kHz, 40-nm 72-kb 9T subthreshold SRAM with aligned boosted write wordline and negative write bitline write-assist. IEEE Transactions on Very Large Scale Integration VLSI Systems, 23, 958–962.

Nabavi, M., & Sachdev, M. (2017). A 290-mV, 3.34-MHz, 6T SRAM with pMOS access transistors and boosted wordline in 65-nm CMOS technology. IEEE Journal of Solid-State Circuits, 53, 656–667.

Fujiwara, H., Chen, Y.-H., Lin, C.-Y., Wu, W.-C., Sun, D., Wu, S.-R. et al. (2016) A 64-Kb 0.37 V 28nm 10T-SRAM with mixed-Vth read-port and boosted WL scheme for IoT applications. In 2016 IEEE asian solid-state circuits conference (A-SSCC) (pp. 185–188).

Aly, R. E., & Bayoumi, M. A. (2007). Low-power cache design using 7T SRAM cell. IEEE Transactions on Circuits and Systems II: Express Briefs, 54, 318–322.

Pal, S., Gupta, V., Ki, W. H., & Islam, A. (2019). Transmission gate-based 9T SRAM cell for variation resilient low power and reliable Internet of things applications. IET Circuits, Devices & Systems, 13, 584–595.

Liu, Z., & Kursun, V. (2008). Characterization of a novel nine-transistor SRAM cell. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 16, 488–492.

Lu, Y., & Chuang, C.-T. (2013). A disturb-free subthreshold 9T SRAM cell with improved performance and variation tolerance. In 2013 IEEE international SOC conference (pp. 325–329).

Shin, K., Choi, W., & Park, J. (2017). Half-select free and bit-line sharing 9T SRAM for reliable supply voltage scaling. IEEE Transactions on Circuits and Systems I: Regular Papers, 64, 2036–2048.

Wang, D.-P., Lin, H.-J., Chuang, C.-T., & Hwang, W. (2014). Low-power multiport SRAM with cross-point write word-lines, shared write bit-lines, and shared write row-access transistors. IEEE Transactions on Circuits and Systems II: Express Briefs, 61, 188–192.

Chang, I. J., Kim, J.-J., Park, S. P., & Roy, K. (2009). A 32 kb 10T sub-threshold SRAM array with bit-interleaving and differential read scheme in 90 nm CMOS. IEEE Journal of Solid-State Circuits, 44, 650–658.

Sharma, V., Bisht, P., Dalal, A., Gopal, M., Vishvakarma, S. K., & Chouhan, S. S. (2019). Half-select free bit-line sharing 12T SRAM with double-adjacent bits soft error correction and a reconfigurable FPGA for low-power applications. AEU-International Journal of Electronics and Communications, 104, 10–22.

Sharma, V., Gupta, N., Shah, A. P., Vishvakarma, S. K., & Chouhan, S. S. (2021). A reliable, multi-bit error tolerant 11T SRAM memory design for wireless sensor nodes. Analog Integrated Circuits and Signal Processing, 107, 339–352.

Yadav, N., Shah, A. P., & Vishvakarma, S. K. (2017). Stable, reliable, and bit-interleaving 12T SRAM for space applications: A device circuit co-design. IEEE Transactions on Semiconductor Manufacturing, 30, 276–284.

Pal, S., Bose, S., Ki, W.-H., & Islam, A. (2020). A highly stable reliable SRAM cell design for low power applications. Microelectronics Reliability, 105, 113503.

Chiu, Y.-W., Hu, Y.-H., Tu, M.-H., Zhao, J.-K., Chu, Y.-H., Jou, S.-J., et al. (2014). 40 nm bit-interleaving 12T subthreshold SRAM with data-aware write-assist. IEEE Transactions on Circuits and Systems I: Regular Papers, 61, 2578–2585.

Anh-Tuan, D., Low, J. Y. S., Low, J. Y. L., Kong, Z.-H., Tan, X., & Yeo, K.-S. (2011). An 8T differential SRAM with improved noise margin for bit-interleaving in 65 nm CMOS. IEEE Transactions on Circuits and Systems I: Regular Papers, 58, 1252–1263.

Kim, J., & Mazumder, P. (2017). A robust 12T SRAM cell with improved write margin for ultra-low power applications in 40 nm CMOS. Integration, 57, 1–10.

Predictive Technology Model (PTM), http://ptm.asu.edu/

Verma, N., Kwong, J., & Chandrakasan, A. P. (2007). Nanometer MOSFET variation in minimum energy subthreshold circuits. IEEE Transactions on Electron Devices, 55, 163–174.

Rabaey, J. M., Chandrakasan, A. P., & Nikolić, B. (2003). Digital integrated circuits: A design perspective (7th ed.). Upper Saddle River, NJ: Pearson Education.

Ahmad, S., Iqbal, B., Alam, N., & Hasan, M. (2018). Low leakage fully half-select-free robust SRAM cells with BTI reliability analysis. IEEE Transactions on Device and Materials Reliability, 18, 337–349.

Saha, S. K. (2014). Compact MOSFET modeling for process variability-aware VLSI circuit design. IEEE Access, 2, 104–115.

Pasandi, G., & Fakhraie, S. M. (2014). A 256-kb 9T near-threshold SRAM with 1k cells per bitline and enhanced write and read operations. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 23, 2438–2446.

Narendra, S., De, V., Borkar, S., Antoniadis, D. A., & Chandrakasan, A. P. (2004). Full-chip subthreshold leakage power prediction and reduction techniques for sub-0.18-/spl mu/m CMOS. IEEE Journal of Solid-State Circuits, 39, 501–510.

Seevinck, E., List, F. J., & Lohstroh, J. (1987). Static-noise margin analysis of MOS SRAM cells. IEEE Journal of solid-state circuits, 22, 748–754.

Abbasian, E., & Gholipour, M. (2020). A variation-aware design for storage cells using Schottky-barrier-type GNRFETs. Journal of Computational Electronics, 1–15.

Abbasian, E., & Gholipour, M. (2021). Single-ended half-select disturb-free 11T static random access memory cell for reliable and low power applications. International Journal of Circuit Theory and Applications, 49(4), 970–989.

E. Abbasian and M. Gholipour, "Robust transmission gate-based 10T subthreshold SRAM for internet-of-things applications," Semiconductor Science and Technology, 2022.

Ahmad, S., Alam, N., & Hasan, M. (2018). Pseudo differential multi-cell upset immune robust SRAM cell for ultra-low power applications. AEU-International Journal of Electronics and Communications, 83, 366–375.

Weste, N. H., & Harris, D. (2015) CMOS VLSI design: A circuits and systems perspective. Pearson Education India.

Alioto, M. (2010). Understanding DC behavior of subthreshold CMOS logic through closed-form analysis. IEEE Transactions on Circuits and Systems I: Regular Papers, 57, 1597–1607.

Chang, I. J., Mohapatra, D., & Roy, K. (2011). A priority-based 6T/8T hybrid SRAM architecture for aggressive voltage scaling in video applications. IEEE Transactions on Circuits and Systems for Video Technology, 21, 101–112.

Hazucha, P., & Svensson, C. (2000). Impact of CMOS technology scaling on the atmospheric neutron soft error rate. IEEE Transactions on Nuclear Science, 47, 2586–2594.

Chen, J., Chong, K.-S., Gwee, B.-H., & Chang, J. S. (2012) An ultra-dynamic voltage scalable (U-DVS) 10T SRAM with bit-interleaving capability. In 2012 IEEE international symposium on circuits and systems (pp. 1835–1838).

Jiao, H., Qiu, Y., & Kursun, V. (2016). Low power and robust memory circuits with asymmetrical ground gating. Microelectronics Journal, 48, 109–119.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflicts of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Abbasian, E., Sofimowloodi, S. A robust multi-bit soft-error immune SRAM cell for low-power applications. Analog Integr Circ Sig Process 115, 49–66 (2023). https://doi.org/10.1007/s10470-023-02144-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-023-02144-0