Abstract

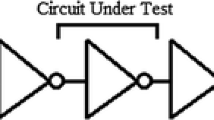

High noise margins and low power dissipation are the major attributes of the SRAM cells used in ultra-low power applications. This paper proposes a 10T Static Random-Access memory (SRAM) with data aware dynamic feedback control and disturb free read which enhances the noise margins in the sub-threshold region. Exploiting the dynamic threshold MOS transistors (DTMOS) technique reduces the read access time of the proposed memory cell. As this cell offers single ended write operation with the bitlines kept at logic HIGH which leads to large saving in dynamic power due to charging/discharging operation on bitlines. Therefore, proposed SRAM reduces the activity factor of discharging the bitlines for each write pattern. The simulation has been carried out in 65 nm technology node to show the comparison among the existing techniques and proposed cell. The proposed memory cell has write static noise margin (WSNM) of 1.7x and 1.48x compared to iso-area 6T and Schmitt Trigger based (ST2) SRAM cells respectively at supply voltage of 300 mV. Read operation is data controlled which improves the read margin. Dynamic threshold technique increases read current for faster read operation. Read SNM is 2x, 1.16x and 1.4x of iso-area 6T, differential data aware 9T and Schmitt trigger SRAM (ST2) respectively. These features enable the cell for ultralow power applications.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Rabaey, J.M., Chandrakasan, A., Nikolic, B.: Digital Integrated Circuits: A Design Perspective, 2nd edn. Prentice-Hall, New Delhi (2005)

Karandikar, A., Parhi, K.K.: Low power SRAM design using hierarchical divided bit-line approach. In: Proceedings of International Conference Computer Design, pp. 82–88 (1998)

Zhai, B., Hanson, S., Blaauw, D., Sylvester, D.: A variation-tolerant sub-200 mV 6-T subthreshold SRAM. IEEE J. Solid-State Circuits of 43(10), 2338–2348 (2008)

Pilo, H., Barwin, J., Braceras, G., Browning, C., Burns, S., Gabric, J., Lamphier, S., Miller, M., Roberts, A., Towler, F.: An SRAM design in 65 nm and 45 nm technology nodes featuring read and write-assist circuits to expand operating voltage. In: Symposium on VLSI Circuits, Digest of Technical Papers, pp. 15–16, June 2006

Bhavnagarwala, A., Kosonocky, S., Radens, C., Stawiasz, K., Mann, R., Ye, Q., Chin, K.: Fluctuation limits and scaling opportunities for CMOS SRAM cells. In: International Electron Devices Meeting (IEDM) Digest, pp. 659–662, December 2005

Suzuki, T., Yamauchi, H., Yamagami, Y., Satomi, K., Akamatsu, H.: A stable 2-port SRAM cell design against simultaneously read/write-disturbed accesses. IEEE J. Solid-State Circuits 43(9), 2109–2119 (2008)

Hirabayashi, O., Kawasumi, A., Suzuki, A., Takeyama, Y., Kushida, K., Sasaki, T., Katayama, A., Fukano, G., Fujimura, Y., Nakazato, T., Shizuki, Y., Kushiyama, N., Yabe, T.: A process-variation-tolerant dual-power-supply SRAM with 0.179 m cell in 40 nm CMOS using level-programmable wordline driver. In: IEEE Int. Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, pp. 458–459, February 2009

Zhang, K., Bhattacharya, U., Chen, Z., Hamzaoglu, F., Murray, D., Vallepalli, N., Wang, Y., Zheng, B., Bohr, M.: A 3-GHz 70-Mb SRAM in 65-nm CMOS technology with integrated column-based dynamic power supply. IEEE J. Solid-State Circuits 41(1), 146–151 (2006)

Bai, N., Wu, X., Yang, J., Shi, L.: A robust high density 7T SRAM bitcell for subthreshold applications. Chin. J. Electron. 20(2), 243–246 (2011)

Singh, J., Mathew, J., Pradhan, D.K., Mohanty, S.P.: A subthreshold single ended I/O SRAM cell design for nanometer CMOS technologies. In: 2008 IEEE International SOC Conference, 17–20 September 2008

Chang, M.-F., Wu, J.-J., Chen, K.-T., Chen, Y.-C., Chen, Y.-H., Lee, R., Liao, H.-J., Yamauchi, H.: A differential data-aware power-supplied (D-AP) 8T SRAM cell with expanded write/read stabilities for lower VDDmin applications. IEEE J. Solid-State Circuits 45(6), 1234–1245 (2010)

Yoshimoto, M.: A 64 kb CMOS RAM with divided word line structure. In: Technical Digest IEEE International Solid-State Circuits Conference, pp. 58–59 (1983)

Yang, B., Kim, L.: A low-power SRAM using hierarchical bit line and local sense amplifiers. IEEE J. Solid-State Circuits 40(6), 1366–1376 (2005)

Hwang, M.-E., Roy, K.: A 135 mV 0.13-μW process tolerant 6T subthreshold DTMOS SRAM in 90 nm technology. In: Proceedings IEEE Custom Integrated Circuits Conference, September 2008, pp. 419–422 (2008)

Chang, M.F., Chang, S.W., Chou, P.W., Wu, W.C.: A 130 mV SRAM with expanded write and read margins for subthreshold applications. IEEE J. Solid-State Circuits 46(2), 520–529 (2011)

Kulkarni, J.P., Roy, K.: Ultralow-voltage process-variation-tolerant Schmitt-trigger-based SRAM design. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 20(2), 319–332 (2012)

Hassanzadeh, S., Zamani, M., Hajsadeghi, K.: A 32 kb 90 nm 10T-cell sub-threshold SRAM with improved read and write SNM. In: Proceedings of 21st Iranian Conference Electrical Engineering (ICEE), May 2013, pp. 1–5 (2013)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2017 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Swaati, Das, B.P. (2017). A 10T Subthreshold SRAM Cell with Minimal Bitline Switching for Ultra-Low Power Applications. In: Kaushik, B., Dasgupta, S., Singh, V. (eds) VLSI Design and Test. VDAT 2017. Communications in Computer and Information Science, vol 711. Springer, Singapore. https://doi.org/10.1007/978-981-10-7470-7_48

Download citation

DOI: https://doi.org/10.1007/978-981-10-7470-7_48

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-10-7469-1

Online ISBN: 978-981-10-7470-7

eBook Packages: Computer ScienceComputer Science (R0)