Abstract

The Channel Hot Carrier (CHC) degradation mechanisms are studied in 3-dimensional n-FinFET devices. In long channel devices, the most degraded condition is at low vertical electric field stress (VG ∼ VD/2) due to the interface degradation by hot carriers, while cold/hot carrier injection to the oxide bulk defect dominates at the high vertical field stress condition (VG = VD). In short channel devices, however, the most degraded condition is at high field stress around VG = VD, because hot carriers are generated continuously at high VG = VD and injected into the oxide bulk defects. The cold carrier contribution to the total CHC degradation is negligible in the short channel n-FinFETs.

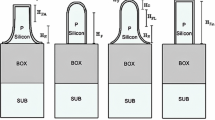

Then, the CHC reliability is studied as a function of fin width at VG = VD stress condition, where higher CHC degradation is observed on narrower fin devices. Both interface degradation by hot carriers and pre-existing bulk oxide defects filling contribute significantly to the total CHC degradation. Though the CHC degradation magnitude is higher in narrower FinFETs, the degradation mechanism does not change as a function of fin width.

Lower CHC degradation is observed in 45° rotated substrate devices, due to the lower initial Nit at the fin side-walls than for the non-rotated device. The lower Si atom density in the 45° rotated FinFET device leads to lower interface degradation.

The effect of fin corners is also discussed. Rounded and sharp corner n-FinFETs do not show a significant difference in PBTI. Since the vertical field applied to the oxide is lower in CHC than PBTI, the corner rounding effect is expected to be negligible in CHC reliability.

An overview of measurement and simulation methodologies for the self-heating effect (SHE) is provided in the last section. It is found that self-heating is a non-negligible phenomenon in the SOI and FinFET technologies, compared to the planar devices. In FinFETs, degradation mechanisms can be activated even at usual operating conditions, which potentially impact device reliability.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

G. Groeseneken, R. Degraeve, B. Kaczer, K. Martens, Trends and perspectives for electrical characterization and reliability assessment in advanced CMOS technologies, in IEEE ESSDERC Proceedings (2010), pp. 64–72

G. Groeseneken, R. Bellens, G. Van den Bosch, H.E. Maes, Hot-carrier degradation in submicrometre MOSFETs: from uniform injection towards the real operating conditions. Semicond. Sci. Technol. 10, 1208–1220 (1995)

C. Hu, S.C. Tam, F.-C. Hsu, P.-K. Ko, T.-Y. Chan, K.W. Terrill, Hot-electron-induced MOSFET degradation – model, monitor, and improvement. IEEE J. Solid State Circuits SC-20(1), 295–305 (1985)

C. Guerin, V. Huard, A. Bravaix, M. Denais, J.M. Roux, F. Perrier, W. Baks, Combined effect of NBTI and channel hot carrier effects in pMOSFETs, in International Integrated Reliability Workshop (2005), pp. 10–16

E. Amat, T. Kauerauf, R. Degraeve, A. De Keersgieter, R. Rodríguez, M. Nafría, X. Aymerich, G. Groeseneken, Channel hot-carrier degradation in short-channel transistors with high-k/metal gate stacks. IEEE Trans. Device Mater. Reliab. 9(3), 425–430 (2009)

C.D. Young, J.-W. Yang, K. Matthews, S. Suthram, M.M. Hussain, G. Bersuker, C. Smith, R. Harris, R. Choi, B.H. Lee, H.-H. Tseng, Hot carrier degradation in HfSiON/TiN fin shaped field effect transistor with different substrate orientations. J. Vac. Sci. Technol. B 27(1), 468–471 (2009)

S.E. Rauch, G. La Rosa, The energy‐driven paradigm of NMOSFET hot‐carrier effects. IEEE Trans. Device Mater. Reliab. 5(4), 701 (2005)

C. Guérin, V. Huard, A. Bravaix, The energy driven hot‐carrier degradation modes in NMOSFETs. IEEE Trans. Device Mater. Reliab. 7(2), 225–235 (2007)

A. Bravaix, C. Guerin, V. Huard, D. Roy, J.‐M. Roux, E. Vincent, Hot‐carrier acceleration factors for low power management in DC–AC stressed 40 nm NMOS node at high temperature, in IEEE International Reliability Physics Symposium (IRPS) Proceedings (2009), pp. 531–548

A. Bravaix, Y.M. Randriamihaja, V. Huard, D. Angot, X. Federspiel, W. Arfaoui, P. Mora, F. Cacho, M. Saliva, C. Besset, S. Renard, D. Roy, E. Vincent, Impact of the gate-stack change from 40 nm node SiON to 28 nm high-K metal gate on the hot-carrier and bias temperature damage, in IEEE IRPS Proceedings (2013), p. 2D.6

S. Ramey, A. Ashutosh, C. Auth, J. Clifford, M. Hattendorf, J. Hicks, R. James, A. Rahman, V. Sharma, A. St Amour, C. Wiegand, Intrinsic transistor reliability improvements from 22 nm tri-gate technology, in IEEE IRPS Proceedings (2013), p. 4C.5

C. Auth et al., A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors, in IEEE Symposium on VLSI Technology Digest of Technical Papers (2012), pp. 131–132

B. Kaczer, S. Mahato, V. Valduga de Almeida Camargo, M. Toledano-Luque, Ph.J. Roussel, T. Grasser, F. Catthoor, P. Dobrovolny, P. Zuber, G. Wirth, G. Groeseneken, Atomistic approach to variability of bias-temperature instability in circuit simulations, in IEEE IRPS Proceedings (2011), pp. 915–919

M. Denais, A. Bravaix, V. Huard, C. Parthasarathy, G. Ribes, F. Perrier, Y. Rey-Tauriac, N. Revil, On-the-fly characterization of NBTI in ultra-thin gate oxide PMOSFET’s, in IEEE International Electron Devices Meeting (2004), pp. 109–112

B. Kaczer, T. Grasser, Ph.J. Roussel, J. Martin-Martinez, R. O’Connor, B.J. O’Sullivan, G. Groeseneken, Ubiquitous relaxation in BTI stressing—New evaluation and insights, in IEEE IRPS Proceedings (2008), pp. 20–27

R. Bellens, P. Heremans, G. Groeseneken, H.E. Maes, A new procedure for lifetime prediction of N-channel mostransistors using the charge pumping techniqueieee, in IEEE IRPS Proceedings (1988), pp. 8–14

D.P. Ioannou, E. Cartier, Y. Wang, S. Mittl, PBTI response to interfacial layer thickness variation in Hf-based HKMG nFETs, in IEEE IRPS Proceedings (2010), pp. 1044–1048

M. Cho, M. Aoulaiche, R. Degraeve, B. Kaczer, T. Kauerauf, L.-Å. Ragnarsson, C. Adelmann, S. Van Elshocht, T.Y. Hoffmann, G. Groeseneken, Advanced PBTI reliability with 0.69 nm EOT GdHfO gate dielectric. Solid State Electron. 63, 5–7 (2011)

E. Cartier, B.P. Linder, V. Narayanan, V.K. Paruchuri, Fundamental understanding and optimization of PBTI in nFETs with SiO2/HfO2 gate stack, in IEEE International Electron Devices Meeting (2006), pp. 1–4

M. Cho, J.-D. Lee, M. Aoulaiche, B. Kaczer, P. Roussel, T. Kauerauf, R. Degraeve, J. Franco, L.-A. Ragnarsson, G. Groeseneken, Insight into negative and positive bias temperature instability (N/PBTI) mechanism in sub 1-nanometer EOT devices. IEEE Trans. Electron Devices 59(8), 2042–2048 (2012)

M. Cho, P. Roussel, B. Kaczer, R. Degraeve, J. Franco, M. Aoulaiche, T. Chiarella, T. Kauerauf, N. Horiguchi, G. Groeseneken, Channel hot carrier degradation mechanism in long/short channel n-FinFETs. IEEE Trans. Electron Devices 60(12), 4002–4007 (2013)

Jacopo Franco’s chapter in this book

B. Eitan, D. Frohman-Bentchkowsky, J. Shappir, Impact ionization at very low voltages in silicon. J. Appl. Phys. 53(2), 1244–1247 (1982)

P. Su, K.-I. Goto, T. Sugii, C. Hu, A thermal activation view of low voltage impact ionization in MOSFETs. IEEE Electron Device Lett. 23(9), 550–552 (2002)

B. Fischer, A. Ghetti, L. Selmi, R. Bez, E. Sangiorgi, Bias and temperature dependence of homogeneous hot-electron injection from silicon into silicon dioxide at low voltages. IEEE Trans. Electron Devices 44(2), 288–296 (1997)

J.M. Roux, X. Federspiel, D. Roy, P. Abramowitz, Correction of self-heating for HCI lifetime prediction, in IEEE IRPS Proceedings (2007), pp. 281–287

C. Prasad, L. Jiang, D. Singh, M. Agostinelli, C. Auth, P. Bai, T. Eiles, J. Hicks, C. H. Jan, K. Mistry, S. Natarajan, B. Niu, P. Packan, D. Pantuso, I. Post, S. Ramey, A. Schmitz, B. Sell, S. Suthram, J. Thomas, C. Tsai, P. Vandervoorn, Self-heat reliability considerations on Intel’s 22nm Tri-Gate technology, in IEEE IRPS Proceedings (2013), pp. 5D.1.1–5D.1.5

Y.-K. Choi, D. Ha, E. Snow, J. Bokor, T.-J. King, Reliability study of CMOS FinFETs, in IEEE International Electron Devices Meeting (2003), pp. 7.6.1–7.6.4

M. Koyanagi, H. Kaneko, S. Shimizu, Optimum design of n+−n- double-diffused drain MOSFET to reduce hot-carrier emission. IEEE Trans. Electron Devices 32(3), 562–570 (1985)

B.-K. Choi, K.-R. Han, Y.M. Kim, Y.J. Park, J.-H. Lee, Threshold-voltage modeling of body-tied FinFETs (Bulk FinFETs). IEEE Trans. Electron Devices 54(3), 537–545 (2007)

G.V. Groeseneken, Hot carrier degradation and ESD in submicrometer CMOS technologies: how do they interact? IEEE Trans. Device Mater. Reliab. 1(1), 23–32 (2001)

M. Cho, R. Ritzenthaler, R. Krom, Y. Higuchi, B. Kaczer, T. Chiarella, G. Boccardi, M. Togo, N. Horiguchi, T. Kauerauf, G. Groeseneken, Negative bias temperature instability (NBTI) in p-FinFETs with 45-degree substrate rotation. IEEE Electron Device Lett. 34(10), 1211–1213 (2013)

A.N. Tallarico, M. Cho, J. Franco, R. Ritzenthaler, M. Togo, N. Horiguchi, G. Groeseneken, F. Crupi, Impact of the substrate orientation on CHC reliability in n-FinFETs—separation of the various contributions. IEEE Trans. Device Mater. Reliab. 14(1), 52–56 (2014)

J.G. Fossum, J.-W. Yang, V.P. Trivedi, Suppression of corner effects in triple-gate MOSFETs. IEEE Electron Device Lett. 24(12), 745–747 (2003)

R.H. Tu, C. Wann, J.C. King, P.K. Ko, C. Hu, An AC conductance technique for measuring self-heating in SOI MOSFET’s. IEEE Electron Device Lett. 16(2), 67–69 (1995)

D.A. Dallmann, K. Shenai, Scaling constraints imposed by self-heating in sub-micron SO1 MOSFET’s. IEEE Trans. Electron Devices 42(3), 489–496 (1995)

C. Fiegna, Y. Yang, E. Sangiorgi, A.G. O’Neill, Analysis of self-heating effects in ultrathin-body SOI MOSFETs by device simulation. IEEE Trans. Electron Devices 55(1), 233–244 (2008)

R. Rhyner, M. Luisier, Self-heating effects in ultra-scaled Si nanowire transistors, in IEEE International Electron Devices Meeting (2013), pp. 790–793

D. Vasileska, K. Raleva, A. Hossain, S.M. Goodnick, Current progress in modeling self-heating effects in FD SOI devices and nanowire transistors. J. Comput. Electron 11, 238–248 (2012)

W. Liu, M. Asheghi, Phonon-boundary scattering in ultra-thin single crystal silicon layers. Appl. Phys. Lett. 84, 3819–3821 (2004)

J. Lee, A. Liao, E. Pop, W.P. King, Electrical and thermal coupling to a single-wall carbon nanotube device using an electrothermal nanoprobe. Nano Lett. 9(4), 1356–1361 (2009)

N. Beppu, S. Oda, K. Uchida, Experimental study of self-heating effect (SHE) in SOI MOSFETs: accu-rate understanding of temperatures during AC conductance measurement, proposals of 2ω method and modified pulsed IV, in IEEE International Electron Devices Meeting (2012), pp. 642–645

A. Scholten, G.D.J. Smit, R.M.T. Pijper, L.F. Tiemeijer, H.P. Tuinhout, J.-L.P.J. van der Steen, A. Mercha, M. Braccioli, D.B.M. Klaassen, Experimental assessment of self-heating in SOI FinFETs, in IEEE International Electron Devices Meeting (2009), pp. 305–308

B.M. Tenbroeck, M.S.L. Lee, W. Redman-White, R.J.T. Bunyan, M.J. Uren, Self-heating effects in SOI MOSFET’s and their measurement by small signal conductance techniques. IEEE Trans. Electron Devices 43(12), 2240–2248 (1996)

S. Makovejev, S. Olsen, J.-P. Raskin, RF extraction of self-heating effects in FinFETs. IEEE Trans. Electron Devices 58(10), 3335–3341 (2011)

K. Raleva, E. Bury, D. Vasileska, B. Kaczer, Uncovering the temperature of the hotspot in nanoscale devices, in Accepted for 17th International Workshop on Computational Electronics, Paris (2014)

T. Takahashi, T. Matsuki, T. Shinada, Y. Inoue, K. Uchida, Comparison of self-heating effect (SHE) in short-channel bulk and ultra-thin BOX SOI MOSFETs: impacts of doped well, ambient temperature, and SOI/BOX thicknesses on SHE, in IEEE International Electron Devices Meeting (2013), pp. 184–187

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2015 Springer International Publishing Switzerland

About this chapter

Cite this chapter

Cho, M., Bury, E., Kaczer, B., Groeseneken, G. (2015). Channel Hot Carrier Degradation and Self-Heating Effects in FinFETs. In: Grasser, T. (eds) Hot Carrier Degradation in Semiconductor Devices. Springer, Cham. https://doi.org/10.1007/978-3-319-08994-2_10

Download citation

DOI: https://doi.org/10.1007/978-3-319-08994-2_10

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-319-08993-5

Online ISBN: 978-3-319-08994-2

eBook Packages: EngineeringEngineering (R0)