Abstract

The biggest stumbling block to make formal verification widely acceptable is the state space explosion problem. Abstraction is used to simplify a design so that the number of reachable states is reduced. In this paper, we first introduce a concurrency model, called integer combinational/sequential (ICS), capable of describing hardware systems at high and low levels of abstractions. ICS uses finite relations, interpreted and uninterpreted integer functions and predicates, interpreted memory functions, and supports non-determinism and fairness constraints. As a subset, it includes finite-state systems with general fairness constraints. Verification in this framework is performed using language containment as follows.

-

1.

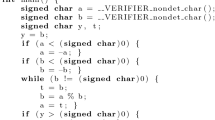

For a subclass of “control-intensive” ICS models, we prove that finite small instantiations can be used to decide the properties without sacrificing accuracy. A linear time algorithm for recognizing these subsets is given. These results also hold for the standard finite-state systems and thus also provide some generic methods for automatic data abstraction for such systems. Using these results, we are able to verify a memory model by reducing integer data values to binary, and unbounded memory addresses to a small number.

-

2.

For verifying properties of circuits with complex datapaths, the model can be executed symbolically to find the reachable states. In some cases, the set of reachable states is finite, and the verification can be completed exactly. In other cases, given n, the verifier checks that no errors of length less than n exist.

Chapter PDF

Similar content being viewed by others

Keywords

These keywords were added by machine and not by the authors. This process is experimental and the keywords may be updated as the learning algorithm improves.

References

R. E. Bryant, “Graph Based Algorithms for Boolean Function Manipulation”, IEEE Trans. on Computers, C-35(8):677–691, August 1986.

J. Burch, D. Dill, “Automated Verification of Pipelined Micro-processors”, Computer-Aided Verification, 1994.

D. Cyrluk, P. Narendran, “Ground Temporal Logic: A Logic for Hardware Verification”, Computer-Aided Verification, 1994.

R. Hojati, R. K. Brayton, “An Environment for Formal Verification Based On Symbolic Computations”, Journal of Formal Methods, 1995.

R. Hojati, S. Krishnan, R. K. Brayton, “Heuristic Algorithms for Early Quantification and Partial Product Minimization”, ERL Memorandum M94/11, March 1994, UC Berkeley.

R. Hojati, R. Mueller-Thuns, P. Lowenstein, R. K. Brayton, “Automatic Verification of Memory System Using Language Containment and Abstraction”, to be submitted to CHDL 95.

C. N. Ip, D. Dill, “Better Verification through Symmetry”, Symp. on Computer Hardware Description Languages and Their Application, 1993.

E. Macii, B. Plessier, F. Somenzi, “Verification of Systems Containing Counters”, IEEE/ACM International Conference on Computer-Aided Design, 1992.

R. P. Kurshan, “Automata-Theoretic Verification of Coordinating Processes”, UC Berkeley notes, 1992.

N. Shankar, S. Owre, J. M. Rushby, “The PVS Specification and Verification System”, SRI International, 1993.

R. E. Shostak, “A Practical Decision Procedure for Arithmetic With Function Symbols”, JACM Volume 26, No. 2, April 1979, pp. 351–360.

P. Wolper, “Expressing Interesting Properties of Programs”, 13th Annual ACM Symp. on Principles of Prog. Languages, 1986.

Editor information

Rights and permissions

Copyright information

© 1995 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Hojati, R., Brayton, R.K. (1995). Automatic datapath abstraction in hardware systems. In: Wolper, P. (eds) Computer Aided Verification. CAV 1995. Lecture Notes in Computer Science, vol 939. Springer, Berlin, Heidelberg. https://doi.org/10.1007/3-540-60045-0_43

Download citation

DOI: https://doi.org/10.1007/3-540-60045-0_43

Published:

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-60045-9

Online ISBN: 978-3-540-49413-3

eBook Packages: Springer Book Archive