Abstract

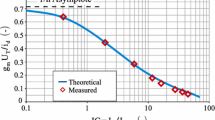

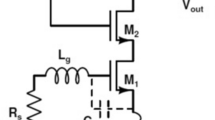

This paper presents in front of us a novel approach for the optimal design of a Low Noise Amplifier (LNA) with inductive source degeneration circuit using a recently proposed evolutionary optimization technique called PSO with Aging Leader and Challenger (ALC-PSO). The proposed ALC-PSO based approach has succeeded in dealing with the disadvantages faced by PSO algorithm and is employed in this paper for the optimal design of LNA circuit. The MOSFET widths and component’s values are optimized by using ALC-PSO algorithm in order to maximize the gain, minimize the Noise Figure (NF) and to optimize the overall performance of the LNA circuit. The simulation results obtained for the designed LNA circuit confirm the effectiveness of the ALC-PSO based approach over PSO in terms of solution quality, design specifications, and design objectives. The optimally implemented LNA circuit in 0.35 µm CMOS technology yields the gain of 18.64 dB, noise figure of 1.779 dB and power dissipation of 10.60 mW.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Sheffer, D.K., Lee, T.H.: A 1.5 V, 1.5 GHz CMOS low-noise amplifier. IEEE J. Solid-State Circuits 32(5), 745–759 (1997)

Sheffer, D.K., Lee, T.H.: Corrections to “A 1.5 V, 1.5 GHz CMOS low-noise amplifier”. IEEE J. Solid-State Circuits 40(6), 1397–1398 (2005)

Nguyen, T.K., Kim, C.H., Ihm, G.J., Yang, M.S., Lee, S.G.: CMOS low-noise amplifier design optimization tehcniques. IEEE Trans. Microw. Theory Tech. 52(5), 1433–1442 (2004)

Lee, T.H.: The Design of CMOS Radio-Frequency Integrated Circuits. Cambridge University Press, Cambridge, U.K. (2006)

Bonabeau, E., Dorigo, M., Theraulaz, G.: Swarm Intelligence: From Natural to Artificial System. Oxford University Press, New York (1999)

Behbahani, F., Leete, J.C., Kishigami, Y., Roithmeier, A., Hoshino, K., Abidi, A.A.: A 2.4-GHz low-IF receiver for wideband WLAN in 0.6 µm CMOS-architecture and front-end. IEEE J. Solid-State Circuits 35, 1908–1916 (2000)

Hashemi, H., Hajimiri, A.: Concurrent dual-band CMOS low noise amplifiers and receiver architectures. In: VLSI Circuits Symposium of Digest of Technical Papers, pp. 247–250, June 2001

Li, X., Brogan, T., Esposito, M., Myers, B., Kenneth, K.O.: A comparison of CMOS and SiGe LNA’s and mixers for wireless LAN application. In: IEEE Custom Integrated Circuits Conference (CICC), pp. 531–534 (2001)

Su, J., Meng, C., Li, Y., Tseng, S., Huang, G.: 2.4 GHz 0.35 µm CMOS single-ended LNA and mixer with gain enhancement techniques. In: Asia-Pacific Microwave Conference (APMC), pp. 1550–1553, Dec 2005

Fan, X., Zhang, H., Sanchez-Sinencio, E.: A noise reduction and linearity improvement technique for a differential cascode LNA. IEEE J. Solid-State Circuits 43(3), 588–599 (2008)

De Prasad, Bishnu, Kar, R., Mandal, D., Ghoshal, S.P.: Particle swarm optimization with aging leader and challengers for optimal design of analog active filters. Circuits Syst Signal Process. 34(3), 707–737 (2015)

Linten, D., Aspemyr, L., Jeamsaksiri, W., Ramos, J., Mercha, A., Jenei, S., Thijs, S., Garcia, R., Jacobsson, H., Wambacq, P., Donnay, S., Decoutere, S.: Low-power 5 GHz LNA and VCO in 90 nm RF CMOS. In: VLSI Symposium Technology Digest, pp. 372–375 (2004)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2019 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Mallick, S., Kar, R., Mandal, D., Dasgupta, T., Ghoshal, S.P. (2019). Optimal Design of 2.4 GHz CMOS LNA Using PSO with Aging Leader and Challenger. In: Bhatia, S., Tiwari, S., Mishra, K., Trivedi, M. (eds) Advances in Computer Communication and Computational Sciences. Advances in Intelligent Systems and Computing, vol 759. Springer, Singapore. https://doi.org/10.1007/978-981-13-0341-8_27

Download citation

DOI: https://doi.org/10.1007/978-981-13-0341-8_27

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-13-0340-1

Online ISBN: 978-981-13-0341-8

eBook Packages: Intelligent Technologies and RoboticsIntelligent Technologies and Robotics (R0)