Abstract

This study reports on the fabrication and characterization of thin-film transistors (TFTs) based on indium–gallium–zinc–oxide (IGZO) with various source- and drain-region metals (Pt, W and Ti). The performance of the IGZO transistors is compared to TFTs based on hydrogenated amorphous silicon (a-Si:H) with Pt source- and drain-regions. From the output characteristics maximum saturation mobilities of µ = 0.45 cm2/Vs for a-Si:H, and µ = 24 to 50 cm2/Vs for IGZO TFTs are extracted, which are competitive to high-performance thin-film transistors. The study reveals a general influence of the source- and drain-electrode material on the maximum saturation mobility and inverse sub-threshold slope.

Graphical abstract

Similar content being viewed by others

Avoid common mistakes on your manuscript.

Introduction

Thin-film transistors based on metal source- and drain-regions are easy and cheap to fabricate, and are used in many applications including display technology and bio-sensing [1]. A number of fabrication techniques (including pulsed laser deposition [2] and sputtering [3]) have been used to deposit amorphous TFT-semiconductor materials including hydrogenated silicon (a-Si:H) [4], and indium–gallium–zinc–oxide (IGZO) [5]. TFTs can be fabricated on conventional silicon wafers, silicon on insulator [6], and flexible substrates [7]. Since many thin-film semiconductor materials are transparent, even optically transparent transistors can be fabricated [8].

TFTs are similar to Schottky–Barrier transistors (SBMOS) [9], since in both devices Schottky junctions are formed between source and channel, and drain and channel, respectively. In TFTs these Schottky junctions are made of metal/semiconductor contacts, whereas for SBMOS these junctions are typically made of metal-silicides such as NiSi [10]. Since ion-implantation is not required for SBMOS fabrication, atomically abrupt junctions can be fabricated offering a high scalability and suppressed drain-induced barrier lowering [11]. Despite the similarity to the SBMOS, TFTs target different applications due to the significantly lower charge carrier mobility in amorphous semiconductors. For example, a-Si:H lacks of band conduction and conductivity is driven by hopping between localized tail-states. This results in significantly smaller charge carrier mobilities (µn ≈ 0.1–2 cm2/Vs of electrons and µp ≈ 10−4 cm2/Vs of holes [12]) in a-Si:H TFTs compared to CMOS-transistors (µn ≈ 103 cm2/Vs and µp = 102 cm2/Vs [13]). In contrast to a-Si:H, IGZO is naturally transparent and offers higher charge carrier mobilities (µ > 10 cm2/Vs [14]), which makes it attractive for fast-response TFTs used for LED displays. Further improvement of the performance of IGZO-based transistors is in focus of research to fabricate even larger high-resolution (8 K) and more energy-efficient displays, or even unlocking the device potential for new application fields such as cheap and flexible analogue or digital electronics.

This study reports on the fabrication of IGZO-based TFTs with various source/drain metals. The device performance is compared to a-Si:H TFTs. IGZO-devices are fabricated completely at room temperature without any post-thermal treatment, which is highly attractive for fabrication of TFTs for displays. Special attention is paid to the transistor characteristics, in particular the saturation mobility and sub-threshold behavior by finding the right choice of the source-/drain-electrode material.

Experimental details

Top-gated thin-film transistors based on IGZO have been fabricated with a channel width W = 10 µm and a channel length L = 2 µm. a-Si:H TFTs were fabricated in a previous study [15] and are used as reference transistors here. Oxidized silicon wafers (SiO2 thickness 650 µm) with an additional TiO2 adhesion layer (thickness 10 nm) were used as substrates. The source- and drain-regions (S/D-regions, thickness 30 nm) were prepared by direct-current (DC) sputtering. For substrative pattern transfer of source and drain UV lithography and reactive ion-etching (RIE) were used. For this step, AZ 5214E image reversal resist was diluted 6:5 in 1-methoxy-2-propanol acetate for patterning of S/D-regions. For a-Si:H TFTs only Pt is used as source- and drain-contacts. In case of IGZO TFTs the S/D regions were made of Pt, Ti and W, respectively. Afterwards, the amorphous semiconductor was deposited at room temperature (thickness 50 nm). IGZO was RF-sputtered (IGZO target, purity 5 N) using a mixture of Ar and O2 with a total constant flowrate Qtot = QOx + QAr = 30 sccm, where QOx is the flowrate of oxygen, yielding again a process pressure of 5.4 × 10−3 hPa. Best electrical characteristics were found for QOx = 0, which is used for device fabrication. X-ray reflectivity (XRR) was used for characterization of the thin-film density (see below). While no additional heat treatment was used for IGTO based TFTs, a-Si:H based TFTs were annealed in forming gas (4% H2 in N2) using rapid thermal annealing (800 °C for 5 min) after Si deposition. Further details on the fabrication of a-Si:H TFTs can be found in Ref. [15]. In a next step, 10 nm thick Al2O3 was electron-beam evaporated and is acting as gate-dielectric. The semiconductor + Al2O3 layers were microstructured using a single UV lithography step followed by RIE in Ar-plasma. Afterwards, 30 nm Pt was deposited as gate-electrode and patterned using a lift-off process. A schematic of the sample structure is shown in Fig. 1a (lateral view) and Fig. 1b (cross-sectional view). An optical microscopy image of a fabricated transistor is shown in Fig. 1c. For device characterization a HP 4155B Semiconductor Analyzer was used.

Results and discussion

For IGZO TFTs special attention was paid to the deposition process. The densities and thickness of thin-films fabricated by different oxygen flows were extracted from simulated fitting-curves of their XRR spectra (Fig. 2a). For readability in Fig. 2a, the XRR spectra are shifted by a fixed scale factor (between 1 and 104): e.g. the spectrum for QOx = 5 sccm is multiplied by a factor of 10. From the thickness the deposition rate can be calculated, which decreases by increase of QOx from 1.85 to ≈ 0.6 Å/s (Fig. 2b), as expected for reactive sputtering. Total reflection is present at the critical angle \({\Theta }_{\mathrm{C}}\) which is proportional to the square root of the density [16]. Based on the measurements, simulated fitting curves reveal a density of 5.4–6.15 g/cm3 (Fig. 2b) which is slightly lower than single-crystal IGZO (6.4 g/cm3) but similar to reports in literature [17]. For larger oxygen flows one finds a density of up to 6.15 g/cm3. For QOx = 0 the density is 6 g/cm3. The smallest density of 5.4 g/cm3 is found for QOx = 0.4. Formation of a mesoporous morphology could be a reason for such a drop of the density.

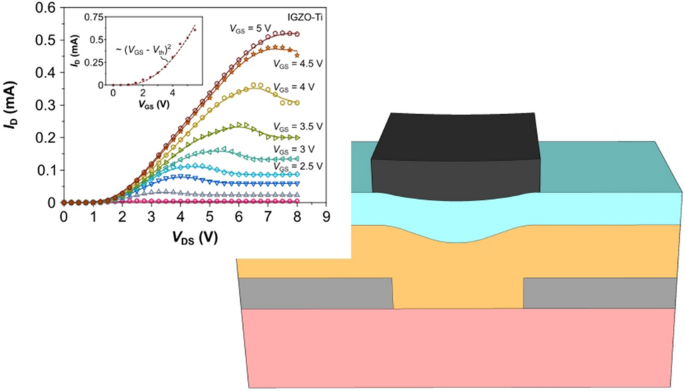

The output characteristics (i.e. drain current ID vs. drain-source-voltage VDS) of IGZO and a-Si:H TFTs are depicted in Fig. 3a to d for variable gate-source-voltage VGS. a-Si:H based TFTs [15] are used as reference devices. The drain current in the saturation regime is:

where \({g}_{m}\) is the transconductance parameter, and Vth is the threshold voltage. Using the transconductance parameter \( g_{{\text{m}}} \sim \left. {{\text{d}}I_{{\text{D}}} /{\text{d}}V_{{{\text{GS}}}} } \right|_{{V_{{{\text{DS}}}} }} \sim \mu \cdot C_{{\text{G}}}^{\prime } \cdot W/L \) the charge carrier saturation mobility µ is found, which is an important performance parameter:

a–c Output characteristics of IGZO-based TFTs with S/D-regions made of Ti, Pt, and W, respectively, for variable VGS. d Output characteristics of an a-Si:H based TFT with S/D-regions made of Pt, for comparison for variable VGS. Redrawn from Ref. [15] with permission from IOP Publishing. The inset in a–d depict the transfer-characteristics (ID vs VGS) in linear scale of each device, respectively. e Transfer-characteristic in semi-log scale of a Ti-based IGZO TFT. f Comparison of the saturation mobility and inverse sub-threshold slope vs. work function of the source/drain metals for IGZO TFTs

Here, CG′ ≈ 0.8 × 10−6 F/cm2 is the specific gate capacity. For IGZO based transistors a mobility of µ ≈ 24 cm2/Vs for S/D = Pt, µ ≈ 45 cm2/Vs for S/D = W, and µ ≈ 50 cm2/Vs for S/D = Ti is found, respectively. These are competitive values compared to µ ≈ 70 cm2/Vs for high mobility IGZO TFTs [14]. For a-Si:H one finds µ ≈ 0.45 cm2/Vs [15], which is in the range of values reported in the literature (µ ≈ 0.1–2 cm2/Vs [12]). In contrast to a-Si:H TFTs, the slope for IGZO TFTs for VDS < 2 V is relatively flat which could be attributed to a parasitic diode-behavior of one of the metal/semiconductor junctions. This behavior has been observed for all metals studied here, including inert Pt. Therefore, this effect cannot be explained by formation of oxide interfaces during processing. Since IGZO was sputtered without additional oxygen flow, a decrease of the defect density, and thus, a decrease of the electron concentration could lead to a drain-side diode-behavior, similar to what has been observed for Schottky-type drain-IGZO junctions [18].

In addition, a local maximum of ID between the linear and saturation regime is observed. This behavior has been observed mainly for W and Ti based S/D-regions. Since this signature tends to increase by increase of the gate-source-voltage (and thus drain-current) a reason for this effect could be drain-current induced local heating of the semiconductor. Several studies demonstrated a self-heating induced shift of the threshold-voltage [19,20,21], however, usually reported for relatively large channel-widths (i.e. W > 100 µm) [22]. Here, the channel-width is much smaller but the normalized drain-current (ID/W > µA/µm) is similar or even higher compared to studies reporting self-heating effects. It should be noted that this effect did not result in a device degradation in this study. Relatively low drain currents are measured for Pt-based devices (e.g. ID ≈ 10 µA for Pt-IGZO at VGS = 5 V and VDS = 7 V; compared to ID ≈ 550 µA for Ti-, and ID ≈ 380 µA for W-based transistors for VGS = 5 V and VDS = 7 V, respectively). Thus, the self-heating effect in IGZO may be here more dominant in W- and Ti-based devices than in Pt-IGZO TFTs due to the higher drain currents. In fact, this self-heating effect is also not observed for low-drain currents in Ti- and W-IGZO (e.g. VGS < 2 V).

An example of a transfer-characteristic, i.e. ID (in semi-log-scale) vs. VGS, of an IGZO-based TFT with Ti S/D-regions for a fixed VDS = 7 V is shown in Fig. 3e. From Fig. 3e, the inverse sub-threshold slope (SS) can be calculated:

The inverse sub-threshold slope is an important transistor property determining the switching behavior of the transistor. Here, three regimes can be identified: A deep-sub-threshold regime (A) is present for VGS approx. < 1 V with a SS of 0.2 V/dec, (B) a weak ON-state sub-threshold regime [18] for approx. 1 V < VGS < 2.5 V with a swing of SS = 0.5 V/dec, and an ON-state (C) for VGS > 2.5 V.

A relation between the S/D material, and saturation charge carrier mobility and the inverse sub-threshold slope is depicted in Fig. 3f. The largest mobility and smallest SS is found for Ti (work function 4.33 eV). In contrast, Pt (work function 5.65 eV) S/D regions resulted in a mobility almost twice as low compared to Ti and a SS of 0.82 V/dec.

Only little has been reported on the impact of the S/D material on the TFT properties. Choi et al. reported higher saturation mobilities for Ti compared to Ag [23]. Barquinha et al. investigated the impact of Mo, Ti and Ti/Au as S/D materials on the TFT performance. The authors reported higher saturation mobilities for Au and Mo compared to Ti. The inverse sub-threshold slope (≈ 1 V/dec. for all Mo, Ti and Ti/Au) were not specifically mentioned in the study but can be approximated from the transfer characteristics. Yim et al. [24] investigated Mo-, Cu- and Al-based IGZO-TFTs with and without air-annealed thermal treatment, respectively. Without thermal treatment, Mo- and Cu-based devices showed inverse sub-threshold slopes of 0.5 V/dec. A transistor behavior was not observed for Al-based devices at first, but the device behavior changed after thermal treatment. With Time-of-Flight Secondary Mass Spectroscopy the authors found that Cu diffused into IGZO after annealing, whereas Al forms an oxide interface between S/D regions and channel. The Al-based devices showed conventional transistor characteristics after thermal treatment. The authors contributed this to the formation of an interface resulting in a higher electron concentration in IGZO and therefore a negative threshold voltage. In case of Cu, inter-diffusion leads to an increase of Vth and an increase of SS. For Mo, SS kept constant, but Vth decreased due to a reduction of the oxygen vacancy concentration.

Table 1 summarizes important thin-film transistor characteristics reported in this study and literature. The devices are based on either bottom-gate, top-gate or even source-gated transistor structures [28] with different geometries. These differences result in different threshold-voltages, maximum saturation mobilities, inverse sub-threshold slopes, drain-side diode phenomena, and potential inter-diffusion or interface reactions. Thus, device comparison is difficult. In this study, one finds higher saturation mobilities for relatively low work function metals (e.g. Ti and W compared to Pt). However, this trend is not observed in all cases. For example, Lin et al. reported of µ = 26 cm2/Vs for Ti [30] compared to µ = 10 cm2/Vs for Ni as reported by Sporea et al. [28], Barquinha et al. reported of higher mobilities in case of Ti/Au (µ = 18.7 cm2/Vs) and Mo (µ = 17.4 cm2/Vs) compared to Ti (µ = 16.9 cm2/Vs) [29]. Nevertheless, there is qualitative evidence that the work function of the S/D material has a general impact on the transistor performance. In this study, where transistors with the same geometry and fabrication methods are prepared, a higher work function results in a smaller saturation mobility and a larger inverse sub-threshold slope. This could be attributed to the drain-channel contact: by increase of VDS the electron concentration at the drain-side is lowered, which leads to the formation of a space-charge layer in the saturation regime. The electron concentration at the source-channel junction keeps relatively constant and the junction is in forward bias. Thus, the drain-channel junction could play a dominant role for both the mobility and the inverse sub-threshold slope, presumably due to the formation of an additional material-depended diode-behavior.

Conclusions

This study reports on the fabrication of thin-film transistors based on a-Si:H and IGZO with different source/drain metals (Pt, W and Ti). From the output-characteristics one finds saturation mobilities of 0.45 cm2/Vs of Pt/a-Si:H, and µ ≈ 24 cm2/Vs for Pt/IGZO, µ ≈ 45 cm2/Vs for W/IGZO, and µ ≈ 50 cm2/Vs for Ti/IGZO. These values are competitive to high-performance IGZO-transistors. From the transfer-characteristics two slopes (0.2 V/dec and 0.5 V/dec) in the deep-sub-threshold and weak ON-state regime are found, which are similar to literature values. As a rough estimate, the study finds that high saturation mobilities and small inverse sub-threshold slopes are found for S/D metals with relatively low work functions, which could be caused by a diode-behavior of the drain-channel junction.

Data availability

The data that support the findings of this study are available on request from the corresponding author.

References

A. Kumar, A.K. Goyal, N. Gupta, Review—thin-film transistors (TFTs) for highly sensitive biosensing applications: a review. ECS J. Solid State Sci. Technol. 9, 115022 (2020)

J. Chen, L. Wang, X. Su, L. Kong, G. Liu, X. Zhang, InGaZnO semiconductor thin film fabricated using pulsed laser deposition. Opt. Express 18, 1398 (2010)

M.C. Yu, D.B. Ruan, P.T. Liu, T.C. Chien, Y.C. Chiu, K.J. Gan, S.M. Sze, High performance transparent a-IGZO thin film transistors with ALD-HfO2Gate insulator on colorless polyimide substrate. IEEE Trans. Nanotechnol. 19, 481–485 (2020)

L. Han, P. Mandlik, K.H. Cherenack, S. Wagner, Amorphous silicon thin-film transistors with field-effect mobilities of 2 cm2/V s for electrons and 0.1 cm2/V s for holes. Appl. Phys. Lett. 94, 1–4 (2009)

K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, H. Hosono, Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 432, 488 (2004)

R.P. Singh, M. Khosla, I. Saini, N. Kumar, Design and analysis of IGZO based junctionless thin film transistor using SOI technology. Silicon 13, 2309 (2020)

L. Wang, W. Liao, S.L. Wong, Z.G. Yu, S. Li, Y.F. Lim, X. Feng, W.C. Tan, X. Huang, L. Chen, L. Liu, J. Chen, X. Gong, C. Zhu, X. Liu, Y.W. Zhang, D. Chi, K.W. Ang, Artificial synapses based on multiterminal memtransistors for neuromorphic application. Adv. Funct. Mater. 29, 1–10 (2019)

G.J. Lee, J. Kim, J.H. Kim, S.M. Jeong, J.E. Jang, J. Jeong, High performance, transparent a-IGZO TFTs on a flexible thin glass substrate. Semicond. Sci. Technol. 29, 035003 (2014)

J.M. Larson, J.P. Snyder, Overview and status of metal S/D Schottky–barrier MOSFET technology. IEEE Trans. Electron Devices 53, 1048–1058 (2006)

J.L. Padilla, L. Knoll, F. Gamiz, Q.T. Zhao, A. Godoy, S. Mantl, Simulation of fabricated 20-nm schottky barrier MOSFETs on SOI: impact of barrier lowering. IEEE Trans. Electron Devices 59, 1320–1327 (2012)

M. Jang, Scalability of schottky barrier metal-oxide-semiconductor transistors. Nano Converg. (2016). https://doi.org/10.1186/s40580-016-0071-0

H. Gleskova, S. Wagner, Electron mobility in amorphous silicon thin-film transistors under compressive strain. Appl. Phys. Lett. 79, 3347–3349 (2001)

G.W. Ludwig, R.L. Watters, Mobility in silicon. Phys. Rev. 101, 1699–1701 (1955)

J. Sheng, T.H. Hong, H.M. Lee, K.R. Kim, M. Sasase, J. Kim, H. Hosono, J.S. Park, Amorphous IGZO TFT with high mobility of 70 cm2/(V s) via vertical dimension control using PEALD. ACS Appl. Mater. Interfaces 11, 40300–40309 (2019)

S. Tappertzhofen, L. Nielen, I. Valov, R. Waser, Memristively programmable transistors. Nanotechnology 33, 045203 (2022)

W.C. Johnson, B. Rebat, L. Koppel, S. Gopinath, Semiconductor Material Applications of Rapid X-ray Reflectometry (XRR) Thickness Measurement of Thin-Metal Films by Optical Metrology Semiconductor Material Applications of Rapid X-ray (American Institute of Physics, College Park, 2018)

K. Ide, M. Kikuchi, M. Sasase, H. Hiramatsu, H. Kumomi, H. Hosono, T. Kamiya, Why high-pressure sputtering must be avoided to deposit a-In-Ga-Zn-O films, in Proceedings of AM-FPD 2016—23rd International Workshop on Active-Matrix Flatpanel Displays and Devices: TFT Technologies and FPD Materials (2016), pp. 298–301

S. Lee, A. Nathan, Subthreshold Schottky–Barrier thin-film transistors with ultralow power and high intrinsic gain. Science 354, 302–304 (2016)

S.H. Choi, M.K. Han, Effect of channel widths on negative shift of threshold voltage, including stress-induced hump phenomenon in InGaZnO thin-film transistors under high-gate and drain bias stress. Appl. Phys. Lett. 100, 10–13 (2012)

K.H. Liu, T.C. Chang, M.S. Wu, Y.S. Hung, P.H. Hung, T.Y. Hsieh, W.C. Chou, A.K. Chu, S.M. Sze, B.L. Yeh, Investigation of channel width-dependent threshold voltage variation in a-InGaZnO thin-film transistors. Appl. Phys. Lett. 104, 1–5 (2014)

E.B. Secor, J. Smith, T.J. Marks, M.C. Hersam, High-performance inkjet-printed indium–gallium–zinc–oxide transistors enabled by embedded, chemically stable graphene electrodes. ACS Appl. Mater. Interfaces 8, 17428–17434 (2016)

K.H. Liu, T.C. Chang, W.C. Chou, H.M. Chen, M.Y. Tsai, M.S. Wu, Y.S. Hung, P.H. Hung, T.Y. Hsieh, Y.H. Tai, A.K. Chu, B.L. Yeh, Influence of an anomalous dimension effect on thermal instability in amorphous-InGaZnO thin-film transistors. J. Appl. Phys. 116, 154508 (2014)

K.H. Choi, H.K. Kim, Correlation between Ti source/drain contact and performance of InGaZnO-based thin film transistors. Appl. Phys. Lett. 102, 052103 (2013)

J.R. Yim, S.Y. Jung, H.W. Yeon, J.Y. Kwon, Y.J. Lee, J.H. Lee, Y.C. Joo, Effects of metal electrode on the electrical performance of amorphous In–Ga–Zn–O thin film transistor. Jpn. J. Appl. Phys. 51, 011401 (2012)

E. Lee, T.H. Kim, S.W. Lee, J.H. Kim, J. Kim, T.G. Jeong, J.H. Ahn, B. Cho, Improved electrical performance of a sol–gel IGZO transistor with high-k Al2O3 gate dielectric achieved by post annealing. Nano Converg. 6, 1–8 (2019)

C.Y. Chen, J. Kanicki, High field-effect-mobility a-Si: H TFT based on high deposition-rate PECVD materials. IEEE Electron Device Lett. 17, 437–439 (1996)

J. Chen, H. Ning, Z. Fang, R. Tao, C. Yang, Y. Zhou, R. Yao, M. Xu, L. Wang, J. Peng, Reduced contact resistance of a-IGZO thin film transistors with inkjet-printed silver electrodes. J. Phys. D Appl. Phys. 51, 165103 (2018)

R.A. Sporea, K.M. Niang, A.J. Flewitt, S.R.P. Silva, Novel tunnel-contact-controlled IGZO thin-film transistors with high tolerance to geometrical variability. Adv. Mater. 31, 1902551 (2019)

P. Barquinha, A.M. Vilà, G. Gonçalves, L. Pereira, R. Martins, J.R. Morante, E. Fortunato, Gallium–indium–zinc-oxide-based thin-film transistors: influence of the source/drain material. IEEE Trans. Electron Devices 55, 954–960 (2008)

C.Y. Lin, K. Tang, C.M. Leu, Y.H. Yeh, Flexible IGZO thin-film transistors and inverter circuits with diode-connected transistors fabricated on transparent polyimide substrates. Microsyst. Technol. 6, 1–4 (2019)

Acknowledgments

The author would like to thank Dominik Merten and Alexander Gumprich (TU Dortmund) for proof-reading, Johannes Gallinger for measurement of the electrical characteristics of IGZO-based transistors, and Petra Grewe (IWE 2, RWTH Aachen University) for measurement the XRR-spectra of IGZO.

Funding

Open Access funding enabled and organized by Projekt DEAL.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The author has no conflict to disclose.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Tappertzhofen, S. Impact of electrode materials on the performance of amorphous IGZO thin-film transistors. MRS Advances 7, 723–728 (2022). https://doi.org/10.1557/s43580-022-00298-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1557/s43580-022-00298-z