Abstract

We establish that the phenomenon of transient negative capacitance, conventionally linked to the delay in the response of a domain switching, of a ferroelectric material, and modelled by a non-linear capacitor, can in fact be considered to be more generally applicable to any phenomenon that can be represented by an RC-equivalent circuit. We demonstrate the conditions for sub-60 mV/dec switching in an RC-FET, even if the R and C were constant along both forward and backward sweeps. For semiconductor charge Qch, we show that the necessary condition for sub-60 mV/dec switching (dQch)/(dΨs) = (q/(kBT))Qch, where Ψs is the surface potential, is possible only if Qch > 0 (i.e. when the transistor is ON) during the backward sweep. This insight contributes further understanding on the causes of hysteresis in commonly used SPICE models of FE-FETs.

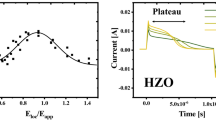

Graphic abstract

Similar content being viewed by others

Avoid common mistakes on your manuscript.

Introduction

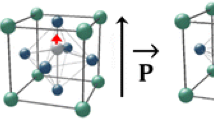

Current research in negative capacitance phenomena is focussed on attempts to eliminate hysteresis in negative capacitance FETs (NCFETs), whilst achieving Steep Subthreshold (SS) characteristics well below 60 mV/decade. Ferroelectric (FE) materials such as HfZrO are fully compatible with CMOS and their ease of integration makes them a promising technology to continue voltage scaling below the 5 nm technology node [1]. The sub-\(60 {\text{mV}}/{\text{dec}}\) behaviour observed in NCFETs can result from the following mechanisms: (1) Negative permittivity or the S shaped behaviour in a single-domain FE [2] under quasi-static conditions as governed by the Landau-Khalatnikov (LK) equation [3], (2) transient negative capacitance in a multi-domain FE or even a paraelectric [4] as represented historically by the Miller model [5,6,7] via a non-negative series \(R\)–\(C\) circuit. In fact, even organic or solid-electrolyte FETs, with a redox mechanism in the gate insulator [8] have been demonstrated with sub-60 mV/dec behaviour by us in [9]. Similar to FEFET, these devices can also be represented by an R–C circuit. 3) In practice transfer characteristics of FEFET are always measured in non-quasi-static conditions with a finite scan rate. In this case, the sub-threshold slope depends upon both intrinsic negative permittivity as well as transient negative capacitance as a consequence of the scan rate. Therefore, an FEFET is a combination of both cases (1) and (2). FETs utilising negative permittivity promise hysteresis-free sub-60 Mv/dec [10, 11], that is typically observed at smaller scan rate or frequency of gate bias sweep, only if the negative capacitance is stabilised. However, if the negative capacitance is not stabilised, these FETs can still exhibit sub-60 mV/dec in both directions of gate bias sweep, albeit with a hysteresis in the transfer characteristics [10, 12], irrespective of how slowly the gate bias is scanned. As the scan rate of gate bias is increased, the transient negative capacitance also starts to play a role because of the finite time it takes for the polarisation to switch that gives rise to a resistor in series with the capacitor of FE. This interplay of the two mechanisms typically results in improvement in SS during the backward sweep but a degradation during the forward sweep and eventually causes it to become greater than \(60 mV/dec\) at sufficiently high frequency of gate bias [9]. In case 2, the sub-\(60 mV/dec\) arising purely from transient negative capacitance is often accompanied by a counter-clockwise hysteresis in the transient transfer characteristics unless it has been offset by trap-induced hysteresis in the clockwise direction [6].

To achieve hysteresis-free operation, the steep switching behaviour arising from a purely negative permittivity in a ferroelectric material is required to be separated from the one that stems from transient negative capacitance as expressed by the Miller model. The phenomenon of transient negative capacitance, despite having completely disparate origins in the case of multi-domain as opposed to single-domain ferroelectric, remains closely interlinked with negative capacitance. The single-domain regime, which is governed by the LK equation, can be expressed by a series R–C circuit in parallel with an oxide capacitor Cox, where \(C\) is considered non-linear and can attain negative values for a certain range of polarisation or can even be positive to yield steep switching [13]. In contrast, the multi-domain approximation is modelled by the Kolmogorov–Avrami–Ishibashi (KAI) model, which utilises a time-dependent polarisation [14] or the Miller model [15], which akin to the LK framework, can be equivalently described as a series \(R\)–\(C\) circuit. In the Miller model, where the gate insulator can be expressed as an \(R\)–\(C\) circuit, the \(C\) remains strictly greater than 0. During the transient sweep, the delay introduced by the \(R\)–\(C\) circuit leads to scenarios where a change in the surface potential of the semiconductor channel becomes greater than that of the gate bias, thus resulting in a body factor of less than 1. Equivalently, the voltage across the gate insulator changes in a direction that is opposite to both the applied gate bias and the surface potential of the semiconductor channel to accommodate this amplification. Since the surface potential directly affects the charge density in the channel, we can also say that the voltage across the insulator changes in the direction opposite to the change in the charge density in the channel, thus producing a transient negative capacitance. This phenomenon emerges purely from a delay introduced within the gate insulator. In different variations of such models at least one of the elements between \(R\) and \(C\) is always considered non-linear (with respect to polarisation) [13] to help explain the steep switching behaviour.

Here we establish that the phenomenon of transient negative capacitance can be considered more general than reported earlier. We demonstrate the conditions for sub-60 mV/dec switching in an RC-FET, even if both the \(R\) and \(C\) are constant.

Methodology

A schematic of a typical RC-FET gate stack is shown in Fig. 1a. In addition to an oxide capacitor Cox, the equivalent circuit of a gate dielectric also contains another branch with a series \(R\)–\(C\) circuit. Similar to a conventional n-MOSFET, an application of gate voltage \(V_{{{\text{GS}}}}\) induces a sheet charge density Qch of mobile carriers in the channel. When a voltage VDS is applied across its drain and source terminals, we observe a current IDS, owing to the presence of these mobile carriers in the channel.

To calculate the current and the transfer characteristics, we solve the equation of the \(R\)–\(C\) circuit of the gate dielectric in conjunction with the Poisson solver in the semiconductor channel, in a self-consistent manner, as illustrated in Fig. 1b. \(Q_{ch}\) consists of two terms \(Q^{\prime}_{{{\text{ch}}}}\) and \(Q^{\prime}\) that are contributed by the two branches of the equivalent circuit in gate oxide, consisting of the elements \(R\)–\(C\) in series and \(C_{ox}\) (see Fig. 1 (a)). The gate voltage \(V_{GS}\) is dropped across the gate oxide \(V_{ox}\), work function between the gate metal and the semiconductor \(\Phi_{ms}\) and the surface potential \(\Psi_{s}\) at the semiconductor channel as

Poisson solver for the channel takes \(\Psi_{s}\) as input and produces \(Q_{ch}\) as output, given the energy band parameters of the semiconductor.

The simulations in this work are generated for fixed values of the oxide and semiconductor parameters,\({ }R\), \(C\), and \(C_{ox}\) as \(6.26{ }M\Omega \cdot cm^{2}\), \(3.19{ }\mu F/cm^{2}\), and \(67{ }nF/cm^{2}\), derived from a Solid Electrolyte FET that shows steep switching via a redox mechanism in the insulator [9]. Nevertheless, the results can be generalised to any other values, but would apply under a different range of scan rate of the gate voltage, as will be proven by deriving the conditions for the body factor (\(m\)) to become less than unity.

Results and discussion

The simulated transfer characteristics of the RC-FET from the self-consistent model for different sweep rates of the gate voltage are plotted in Fig. 2. At extremely low scan rate (quasi-static), any delay introduced by the series \(R\)–\(C\) branch becomes inconsequential and a large capacitor \(C \gg C_{ox}\) in this branch induces a very high charge in the channel, thereby producing the highest possible \(I_{DS}\) at any given \(V_{GS}\) in the forward sweep. During the backward sweep the \(I_{DS}\) simply retraces its value, owing to almost no delay in the discharging of \(C\), at this extremely slow scan rate.

As the scan rate of the gate voltage is increased, a delay in the \(R\)–\(C\) circuit results in a counter-clockwise hysteresis, with the subthreshold slopes during the forward and backward sweeps becoming gentler and steeper, respectively. This trend continues up to a scan rate of \(1.0 V/s\), where the counter-clockwise hysteresis becomes the widest, whilst the subthreshold slope in the backward sweep falls below sub-\(60 mV/dec\). For the scan rate beyond this point, the delay introduced by the \(R\)–\(C\) becomes so large that very little charging or discharging of \(C\) in this branch takes place, leading to a decline in the width of the hysteresis and the subthreshold slope in the backward sweep. At the maximum scan rate of \(460 V/s\), the delay in the \(R\)–\(C\) becomes so large that this branch almost becomes non-responsive to the changes in gate voltage, and most of the charge in the semiconductor is now induced by \(C_{ox}\). Thus, the coupling of the gate to the semiconductor reduces to that of a typical MOS capacitor, without any sub-\(60 mV/dec\) switching. Since these transfer characteristics correspond to a slow-switching SE-FET, the transfer characteristics reduce to that of a MOSFET at relatively smaller scan rate owing to a large \(R\) in the mega-ohm range. If, however, \(R\) is reduced to a few ohms for instance, the scan rate will also be boosted by 6 orders of magnitude.

To understand the behaviour of the subthreshold slope in the forward and backward sweeps, the gate dielectric of the RC-FET is first approximated at its limits of low and high scan rates. Following Fig. 1 (a), the mobile sheet charge density in the channel \(Q_{ch}\) can be described as the sum of the charge densities contributed by the two branches of the equivalent circuit in the gate oxide:

The voltage drop across the gate oxide \(V_{ox}\) can be described as:

At low scan rate, \(dV_{ox} /dt \to 0\), taking the derivative of Eq. (2) and substituting \(dV_{ox} /dt = 0\),

Substituting \(dQ_{ch}^{^{\prime}} /dt\) from Eq. (4) and \(Q_{ch}^{^{\prime}}\) from Eq. (2) into Eq. (3), yields

Since we assume \(C \gg C_{ox}\), the charge density contributed by the series \(R\)–\(C\) branch in the limit of a low scan rate is much larger than that in the branch containing \(C_{ox}\). Thus Eq. (5) can be further simplified to

Hence, at low scan rate, the gate oxide circuit behaves simply as a series \(R\)–\(C\) circuit, having a negligible influence from the parallel capacitor \({\text{C}}_{{{\text{ox}}}}\). Similarly, to derive an expression at a high scan rate (\(dV_{ox} /dt \to \infty\)), we first take the derivative of Eq. (2) with respect to \(V_{ox}\) to yield

Substituting \({\text{d}}Q^{\prime}_{{{\text{ch}}}} /{\text{d}}t\) from Eq. (3), and \(Q_{ch}^{^{\prime}}\) from Eq. (2) this results in

Finally, in the limit of \(dV_{ox} /dt \to \infty\), the above reduces to

Hence in the limit of a high scan rate, the behaviour of the gate oxide reduces to that of an oxide capacitor, thus confirming the behaviour observed in Fig. 2. at a scan rate of \(460 V/s\).

To understand the mechanism of steep subthreshold switching, we next investigate how the behaviour of the coupling between the gate and the semiconductor varies with scan rates, in the limit where the scan rate remains so low that \(V_{ox}\) can be described by Eq. (6). Differentiating this equation with respect to the surface potential of the semiconductor \(\Psi_{s}\) leads to

In the subthreshold regime, the dependence between \(Q_{ch}\) and \(\Psi_{s}\) that is governed by the Poisson equation (see Fig. 1 (b)), can be simplified to an exponential dependence as

where \(Q_{0}\) and \(k_{B}\) are the intrinsic charge density of the semiconductor and Boltzmann constant, respectively. Differentiating Eq. (11) with respect to \(\Psi_{s}\) and substituting the result for \(dQ_{ch} /d\Psi_{s}\) in Eq. (10) gives:

In the first term on the right-hand side, we have leveraged the chain rule to first write \(dQ_{ch} /dt\) as [\(\left( {dQ_{ch} /d\Psi_{s} } \right)\left( {d\Psi_{s} /dt} \right)\)] before applying the differentiation with respect to \(\Psi_{s}\). We have also ignored the contribution from the term \(d^{2} \Psi_{s} /d\Psi_{s} dt\) in the limit of a small scan rate. For the body factor \(m\), to become less than unity, we must have \(m = dV_{GS} /d\Psi_{s} < 1{\text{ or }}dV_{ox} /d\Psi_{s} < 0\), following Eq. (1). Substituting this into Eq. (12) results in

Again, for the body factor \(m = dV_{GS} /d\Psi_{s}\) to be less than unity we must also have:

If \(Q_{ch} > 0\), we can drop \(Q_{ch}\) from both the sides of Eq. (13) without changing the direction of inequality, and utilising Eq. (14), we arrive at

Equation (15) represents the condition for the body factor to be less than unity when \(Q_{ch} > 0\) i.e. when the device is in the ON state. In the above equation, since \(dV_{GS} /dt\) is negative, it signifies that Eq. (15) is only applicable during the backward sweep. Equation (13) also presents another condition when \(Q_{ch} < 0\), i.e. when the device is in OFF state. With \(Q_{ch} < 0\), dropping \(Q_{ch}\) from both the sides results in flipping of the inequality sign, thereby leading to the desired expression:

Since the device remains OFF during the above condition, the transfer characteristics show no steep switching, even though the body factor is less than unity [3].

Figures 3a and b show the behaviour of \(V_{ox}\) with respect to \(V_{GS}\) for different scan rates during forward and backward sweeps, respectively. At extremely small scan rate of \(0.001 V/s\), the slope \(dV_{ox} /dV_{GS}\) remains greater than 0, throughout in both forward and backward sweeps, hence no steep switching is observed, as confirmed in Fig. 3. As the scan rate is increased, the regions with negative slopes start to emerge in both forward and backward sweeps, as seen for the scan rate of \(0.2\) and \(1.0{\text{ V}}/{\text{s}}\), responsible for driving the body factor below unity.

The body factor and the minimum subthreshold swing \(SS_{min}\) as a function of scan rate are plotted in Figs. 4 (a) and (b), respectively. The body factor shows a decline as the scan rate increases. During the backward sweep, that is \(dV_{GS} /dt < 0\), as soon as the scan rate \(\left| {dV_{GS} /dt} \right|\) increases beyond \(0.0013 V/s\) the body factor becomes less than unity, consistent with the derived condition in Eq. (15). This directly translates to a drop in \(SS_{min}\), from \(100 mV/dec\) to less than \(60 mV/dec\) in the backward sweep. During the forward sweep, despite a body factor less than unity, \(SS_{min}\) shows no signs of decrease, in agreement with Eq. (16), which is only satisfied when the device remains in the OFF state (\(Q_{ch} < 0\)) and not in the subthreshold regime. A similar behaviour is noted in [6] of long channel FETs where they point out misalignment with the sub-threshold values of the surface potential as a cause of \(SS > 60 \;{\text{mV}}/{\text{dec}}\). Moreover, a wider hysteresis at higher scan rates causes a degradation in \(SS_{min}\) in the forward sweep.

Conclusion

The gate insulator of many steep switching devices, such as multi-domain FE-FETs, SE-FETs, and other organic FETs can often be reduced to an equivalent series \(R\)–\(C\) circuit. Here, we present a generic RC-FET device, with its gate insulator modelled as a series \(R\)–\(C\) circuit. We have shown that the transfer characteristics of such devices show sub-\(60 mV/dec\) behaviour in the backward sweep and derive the conditions to explain this behaviour. Our results and the derived conditions conclusively establish that despite a promise to achieve a body factor below unity in both forward and backward sweeps, such devices that are affected by transient phenomena can only show sub-\(60 mV/dec\) of SS during the backward sweep. We believe that our results will help distinguish the sub-\(60 mV/dec\) behaviour originating either from negative capacitance or other redox mechanisms, resembling a series \(R\)–\(C\) circuit. Hence for the continuation of the supply voltage scaling, future research should focus on sub-\(60 mV/dec\) behaviour in the forward sweep, as this cannot be facilitated by the undesirable transient negative capacitance.

References

S.S. Cheema et al., Enhanced ferroelectricity in ultrathin films grown directly on silicon. Nature 580(7804), 478–482 (2020)

A.I. Khan, Ferroelectrics, negative capacitance and depolarization field: what exactly is negative capacitance? Device Res. Conf. Conf. Dig. DRC 2019(2008), 57–58 (2019)

L.D. Landau, I.M. Khalatnikov, On the anomalous absorption of sound near a second order phase transition point. Dokl. Akad. Nauk SSSR 96, 469–472 (1954)

A. Kumar, M.M. De Souza, On the Dynamic characteristics of Ferroelectric and Paraelectric FETs. In 2018 IEEE 2nd Electron Devices Technology and Manufacturing Conference (EDTM) pp. 184–186 (2018)

A.K. Saha, S. Datta, S.K. Gupta, ‘Negative capacitance’ in resistor-ferroelectric and ferroelectric-dielectric networks: apparent or intrinsic? J. Appl. Phys. 123(10), 105102 (2018)

B. Obradovic, T. Rakshit, R. Hatcher, J.A. Kittl, M.S. Rodder, Modeling transient negative capacitance in steep-slope FeFETs. IEEE Trans. Electron. Devices 65(11), 5157–5164 (2018)

J. Gomez et al., Hysteresis-free negative capacitance in the multi-domain scenario for logic applications. Tech. Dig. - Int. Electron Devices Meet. IEDM, vol. 2019-Decem, no. i, pp. 138–141 (2019)

P. Balakrishna Pillai, A. Kumar, X. Song, M.M. De Souza, Diffusion-controlled faradaic charge storage in high-performance solid electrolyte-gated zinc oxide thin-film transistors. ACS Appl. Mater. Interfaces 10(11), 9782–9791 (2018)

A. Kumar, P. Balakrishna Pillai, X. Song, M.M. De Souza, Negative capacitance beyond ferroelectric switches. ACS Appl. Mater. Interfaces 10(23), 19812–19819 (2018)

W. Chung, M. Si, P.D. Ye, Hysteresis-free negative capacitance germanium CMOS FinFETs with Bi-directional Sub-60 mV/dec. In 2017 IEEE International Electron Devices Meeting (IEDM), 2017, pp. 15.3.1–15.3.4.

Z. Yu et al., Negative capacitance 2D MoS2 transistors with sub-60mV/dec subthreshold swing over 6 orders, 250 μA/μm current density, and nearly-hysteresis-free. In 2017 IEEE International Electron Devices Meeting (IEDM), pp. 23.6.1–23.6.4 (2017)

A.I. Khan et al., Negative capacitance in short-channel FinFETs externally connected to an epitaxial ferroelectric capacitor. IEEE Electron. Device Lett. 37(1), 111–114 (2016)

M.N.K. Alam, P. Roussel, M. Heyns, J. Van Houdt, Positive non-linear capacitance: the origin of the steep subthreshold-slope in ferroelectric FETs. Sci. Rep. 9(1), 1–9 (2019)

Y.J. Kim et al., Voltage drop in a ferroelectric single layer capacitor by retarded domain nucleation. Nano Lett. 17(12), 7796–7802 (2017)

S.L. Miller, J.R. Schwank, R.D. Nasby, M.S. Rodgers, Modeling ferroelectric capacitor switching with asymmetric nonperiodic input signals and arbitrary initial conditions. J. Appl. Phys. 70(5), 2849–2860 (1991)

Funding

This study was supported by UK-India Education and Research Initiative (GB) (Grant No. P436).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Kumar, A., Song, X. & De Souza, M.M. Necessary conditions for steep switching in a constant Resistor-Capacitor RCFET. MRS Advances 6, 540–545 (2021). https://doi.org/10.1557/s43580-021-00119-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1557/s43580-021-00119-9