Abstract

In this work, we demonstrated Ga2O3-based power MOSFETs grown on c-plane sapphire substrates using in-situ TEOS doping for the first time. The β-Ga2O3:Si epitaxial layers were formed by the metalorganic chemical vapor deposition (MOCVD) with a TEOS as a dopant source. The depletion-mode Ga2O3 power MOSFETs are fabricated and characterized, showing the increase of the current, transconductance, and breakdown voltage at 150 °C. In addition, the sample with the TEOS flow rate of 20 sccm exhibited a breakdown voltage of more than 400 V at RT and 150 °C, indicating that the in-situ Si doping by TEOS in MOCVD is a promising method for Ga2O3 power MOSFETs.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

Introduction

β-Ga2O3 is an emerging material as a potential candidate of high-power device application due to its ultra-wide bandgap of about 4.8 eV [1]. Furthermore, the critical electric field (Ec) of the β-Ga2O3 up to 8 MV/cm is much higher than those common high-power materials such as 4H-SiC (2.5 MV/cm) and GaN (3.3 MV/cm) [2]. It results in the Baliga figure of merit (BFOM) of the β-Ga2O3 being 3214 which is ten times of 4H-SiC (317) and four times of GaN (846) [3]. In addition, the critical problem for SiC and GaN-based devices is a high thermal budget for their crystal growth while the growth temperature of β-Ga2O3 is much lower than those materials and Ga2O3 could be grown epitaxy film using different of methods [4]. The method of metalorganic chemical vapor deposition (MOCVD) can be used to mass product and to grow the Ga2O3 on sapphire substrate [5]. The MOCVD-grown epitaxial layer of Ga2O3 could be doped during growth process by tetraethyl orthosilicate (TEOS) which was first demonstrated in one of the studies [6]. Ga2O3 is also known for the availability of high-quality, large-diameter single-crystal substrate which is grown directly from the melt, with much lower growth temperature and lower cost in process [7, 8].

Those amazing material characteristics mentioned above have been reported for many electrical devices like metal–oxide–semiconductor field-effect transistors (MOSFET) [9,10,11], metal–semiconductor field-effect transistors (MESFET) [12], and Schottky barrier diode [13]. However, most of the devices are grown homoepitaxially and doped by the Si-ion implantation as a shallow donor to increase the conductivity [1].

Here, we reported, for the first time, the depletion (D)-mode MOSFETs by grown heteroepitaxy β-Ga2O3 on sapphire with in-situ Si doped by MOCVD. The performance of D-mode MOSFETs with different in-situ Si-doped concentration will be studied. Moreover, the device performance operated at high temperature will also be discussed.

Device structure and fabrication

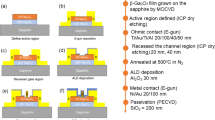

The n-type β-Ga2O3 epilayers with 200-nm thickness were grown on c-plane sapphire substrate at 875 °C by MOCVD. The growth pressure was 25 Torr. Triethylgallium (TEGa) and O2 with the flow rate of 100 sccm and 500 sccm were used as the precursors for Ga and O [14]. The current growth process has been optimized. Detailed crystallinity of the Ga2O3 has been studied in our previous publication [15]. The tetraethyl orthosilicate (TEOS) precursor used the n-type dopant source. To study the effect of different doped active layers on the performance of depletion (D)-mode MOSFET, the β-Ga2O3 epilayer was doped by TEOS with 10 and 20 sccm and denoted A and B samples, respectively. Before the device fabrication, the material characteristics of sample A and B have measured by secondary ion mass spectrum (SIMS) and Hall measurements.

Then, the active region was defined by the etching mesa by inductively coupled plasma reactive ion etching (ICPRIE) using Ar and Cl2. After, Ti/Al/Ni/Au (20/100/40/50 nm) was deposited by E-gun deposition system as the Source (S) and drain (D) Ohmic contact electrodes. The specific contact resistance (\({\uprho }_{{\text{C}}}\)) was measured to be 108 Ω-cm2 on the transfer length structure. After ohmic metal deposition, the 40 nm Al2O3 dielectric layer was deposited by atomic layer deposition (ALD) as the gate oxide. Regarding the pre-treatment before Al2O3 deposition, the acetone, IPA, and DI water were used to clean wafers. Noted that the traditional RCA clean for our device was not used because the HF contained in the RCA clean process may etch the Ga2O3 epilayer. The Picosun R-200 was used to grow the Al2O3 dielectric layer at 250 °C by thermal deposition. The H2O and TMA were used as the precursors. The first pulse time was 0.1 s to let the H2O have self-limiting reaction with Ga2O3 film and terminated when the surface ran out of reactant. The excess gas would be purged in 8 s by N2. Then the second reactant TMA will be introduced into chamber with same pulse time and purge time, again reacting with surface species, concluding one cycle. We processed 353 cycles to deposit our dielectric layer. Then, the ohmic contact region (Source/Drain) was opened by ICPRIE etching. Finally, the Ni/Au (30/150 nm) gate (G) metal was deposited by E-gun deposition system. The MOSFETs have a gate length 4 um (LG), a gate-to-source width (LGS) 7 um, and a gate-to-drain width (LGD) 9 um. Figure 1 shows the schematic structure of the D-mode Ga2O3-based MOSFETs fabricated on sapphire substrate. The key processes of TEOS parameters are summarized in Table 1.

Results and discussion

In this MOSFET structure, only one Si-doped Ga2O3 epilayer was used as an active layer. The Si concentration, carrier concentration and mobility shown in Table 1 for samples A and B were measured by SIMS and Hall effect system. The Si concentrations were 5.5 × 1019 and 1.1 × 1020/cm3 for the TEOS flow rate of 10 and 20 sccm, respectively. The corresponding carrier concentrations were 6.49 × 1017 and 3.2 × 1018/cm3 and mobility were 0.689 and 0.144 cm2/V s for the TEOS flow rate of 10 and 20 sccm. The low mobility could be resulted from the high Si concentration and thin epilayer. Even though, it is important to evaluate the performance of the device. Figure 2. shows the ID–VG and ID–VD characteristics in A and B samples, demonstrating the well-behaved performances with the increase of drain current as the TEOS flow rate increases. Meanwhile, the threshold voltage shifts to more negative in the case of sample B. Table 2 summarizes the key electrical characteristics in sample A and B recorded at VD = 20 V and VG = 4 V.

The high temperature characteristics of Ga2O3-based MOSFETs are also investigated. Figures 3 and 4. show the ID–VG characteristics with different temperature, showing an increase of the drain current as the temperature increases, which is consistent with the observation in some recent studies [16, 17].

The transconductances of both samples are extracted and shown in Fig. 5. The transconductance increases and shifts to more negative gate bias as temperature increases. The samples with lower TEOS flow rate show higher gm peaks, suggesting a high electron mobility in sample A.

The breakdown characteristics (Fig. 6) are performed with a Keysight B1505 device analyzer. Sample A shows the breakdown voltage of 143 V at 25 °C and 288 V at 150 °C and sample B shows the breakdown voltage of 474 V at 25 °C and 487 V at 150 °C, respectively, indicating that high TEOS flow during MOCVD process can enhance the breakdown voltage. Besides, a positive temperature dependency of the breakdown voltage is both observed in sample A and sample B, which is most probably due to the impact ionization [18]. Table 3 shows the benchmark of the breakdown voltage in this work compared to others, clearly indicating that growing Ga2O3 using MOCVD with the doping by TEOS is promising for power electronics application.

Conclusion

In conclusion, the Ga2O3 power MOSFETs with the MOCVD-grown epitaxial layer and in-situ Si doping on sapphire substrate are demonstrated for the first time. Firstly, the depletion-mode Ga2O3 power MOSFETs are fabricated and characterized in the different temperature, showing the high saturation current and high transconductance as temperature increases. Furthermore, the devices with TEOS of 20 sccm (sample B) can achieve more than 400 V breakdown voltage at RT and 150 °C. Lastly, the Ga2O3 power MOSFETs with in-situ Si doping using TEOS show promising breakdown voltage characteristics compared to the recent works. In sum, we demonstrate that TEOS doping is promising for high-performance Ga2O3 power MOSFETs.

Data availability

The datasets generated during and/or analysed during the current study are available from the corresponding author on reasonable request.

References

Dong H, et al. Progress of power field effect transistor based on ultra-wide bandgap Ga2O3 semiconductor material. J Semicond. 2019. https://doi.org/10.1088/1674-4926/40/1/011802.

Kuramata A, et al. High-quality β-Ga2O3 single crystals grown by edge-defined film-fed growth. Jpn J Appl Phys. 2016. https://doi.org/10.7567/JJAP.55.1202A2.

Mastro MA, et al. Perspective–opportunities and future directions for Ga2O3. ECS J Solid State Sci Technol. 2017;6(5):356–539. https://doi.org/10.1149/2.0031707jss.

Higashiwaki M, et al. Recent progress in Ga2O3 power devices. Semicond Sci Technol. 2016. https://doi.org/10.1088/0268-1242/31/3/034001.

Park J-H, et al. MOCVD grown β-Ga2O3 metal-oxide-semiconductor field effect transistors on sapphire. Appl Phys Express. 2019. https://doi.org/10.7567/1882-0786/ab3b2a.

Gogova D, et al. Structural properties of Si-doped β-Ga2O3 layers grown by MOVPE. J Cryst Growth. 2014;401:665–9. https://doi.org/10.1016/j.jcrysgro.2013.11.056.

Galazka Z, et al. Scaling-up of bulk β-Ga2O3 single-crystals by the Czochralski method. ECS J Solid State Sci Technol. 2017;6(2):Q3007. https://doi.org/10.1149/2.0021702jss.

Kuramata A, et al. High-quality β-Ga2O3 single crystals grown by edge-defined film-fed grown. Jpn J Appl Phys. 2016;55(12):1202A2. https://doi.org/10.7567/JJAP.55.1202A2.

Higashiwaki M, et al. Depletion-mode Ga2O3 metal-oxide-semiconductors on β-Ga2O3 (010) substrates and temperature dependence of their device characteristics. Appl Phys Lett. 2013. https://doi.org/10.1063/1.4821858.

Zeng K, et al. A field-plated Ga2O3 MOSFET with near 2-kV breakdown voltage and 520 mΩ cm2 on-resistance. Appl Phys Express. 2019. https://doi.org/10.7567/1882-0786/ab2e86.

Wong MH, et al. Enhancement-mode Ga2O3 MOSFETs with Si-ion-implanted source and drain. Appl Phys Express. 2017. https://doi.org/10.7567/APEX.10.041101.

Higashiwaki M, et al. Gallium oxide (Ga2O3) metal-semiconductor field-effect transitors on single-crystal β-Ga2O3 (010) substrates. Appl Phys Lett. 2012. https://doi.org/10.1063/1.3674287.

Sooyeoun Oh, et al. Electrical characteristics of vertical Ni/β-Ga2O3 Schottky barrier diodes at high temperatures. ECS J Solid State Sci Technol. 2016. https://doi.org/10.1149/2.0041702jss.

Tetzner K, et al. Challenges to overcome breakdown limitations in lateral β-Ga2O3 MOSFET devices. Microelectron Reliab. 2020. https://doi.org/10.1016/j.microrel.2020.113951.

Horng RH, Wuu DS, Liu PL, Sood A, Tarntair FG, Chen YH, Pratap SJ, Hsiao CL. Growth mechanism and characteristics of β-Ga2O3 heteroepitaxial grown on sapphire by metalorganic chemical vapor deposition. Mater Today Adv. 2022;16:100320.

Park J-H, et al. Ga2O3 metal-oxide-semiconductor field effect transistors on sapphire substrate by MOCVD. Semicond Sci Technol. 2019. https://doi.org/10.1088/1361-6641/ab2c17.

Sood A, Wuu D, Tarntair F, Sao NT, Wu T, Tumilty N, Kuo H, Pratap SJ, Horng R. Electrical performance study of Schottky barrier diodes using ion implanted β-Ga2O3 epilayers grown on sapphire substrates. Mater Today Adv. 2023. https://doi.org/10.1016/j.mtadv.2023.100346.

Dyakonova N, et al. Temperature dependence of impact ionization in AlGaN-GaN heterostructures. Appl Phys Lett. 1998. https://doi.org/10.1063/1.121418.

Krishnamoorthy S, et al. Delta-doped β-gallium oxide field-effect transistor. Appl Phys Express. 2017. https://doi.org/10.7567/APEX.10.051102.

Hu Z, et al. Breakdown mechanism in 1 kA/cm2 and 960 V E-mode β-Ga2O3 vertical transistors. Appl Phys Lett. 2018. https://doi.org/10.1063/1.5038105.

Acknowledgements

This work was financially supported by the “Center for the Semiconductor Technology Research” from The Featured Areas Research Center Program within the framework of the Higher Education Sprout Project by the Ministry of Education (MOE) in Taiwan. Also supported in part by the National Science and Technology Council (NSTC), Taiwan, under under Grant 111-2634-F-A49-008, 111-2622-8-A49-018-SB, 111‐2634‐F‐A49‐007, 111-2923-E-A49 -003 -MY3, and the Young Scholar Fellowship Program under Grant 112-2636-E-A49-005.

Author information

Authors and Affiliations

Contributions

NTS.: Data curation, Formal analysis, Writing original draft. C-HLu, F-GT, S-TC.: Data curation, Methodology. T-LW, R-HH: Conceptualization, supervision, project administration, funding acquisition, Writing review and editing.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Ngo, S.T., Lu, CH., Tarntair, FG. et al. Demonstration of MOCVD-grown Ga2O3 power MOSFETs on sapphire with in-situ Si-doped by tetraethyl orthosilicate (TEOS). Discover Nano 18, 79 (2023). https://doi.org/10.1186/s11671-023-03858-w

Received:

Accepted:

Published:

DOI: https://doi.org/10.1186/s11671-023-03858-w