Abstract

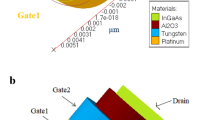

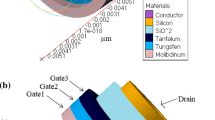

In this work, drain current ID for 5-nm gate length with dual-material (DM) double-surrounding gate (DSG) inversion mode (IM) and junctionless (JL) silicon nanotube (SiNT) MOSFET have been studied and simulation results are reported using Silvaco ATLAS 3D TCAD. For this work, we used the non-equilibrium Green’s function (NEGF) approach and self-consistent solution of Poisson’s equation with Schrödinger's equation. The conduction band splitting into multiple sub-bands has been considered and there is no doping in channel in case of IM SiNT MOSFET. The effect of DM gate engineering for SiNT channel radius 1.5 nm with 0.8-nm gate oxide (SiO2) thickness on ID has been studied. A comparison of results has been done between IM DM DSG and JL DM DSG SiNT. In case of JL, doping concentration is optimized for two concerns: (i) to get the same IOn current as IM device and (ii) to get the same threshold voltage VTh as IM. This has resulted in 102 and 103 times smaller IOff in matching IOn and VTh optimized device, respectively, as compared to IM. It is found that DM gate engineering reduces drain-induced barrier lowering (DIBL) for both IM and JL SiNT MOSFET. In this work, JL have much smaller DIBL ~15 mV/V, almost an ideal SS ~60 mV/dec, and higher IOn/IOff ratio ~2.18 × 108 as compared to available CGAA literature results.

Similar content being viewed by others

REFERENCES

U. K. Das, G. Eneman, R. S. R. Velampati, Y. S. Chauhan, K. B. Jinesh, and T. K. Bhattacharyya, J. Electron Dev. Soc. 6, 1129 (2018).

A. Baidya, S. Baishya, and T. R. Lenk, Mater. Sci. Semicond. Process. 71, 413 (2017).

F. Adamu-Lema, X. Wang, S. M. Amoroso, C. Riddet, B. Cheng, L. Shifren, R. Aitken, S. Sinha, G. Yeric, and A. Asenov, IEEE Trans. Electron Dev. 61, 3372 (2014).

U. K. Das, M. G. Bardon, D. Jang, G. Eneman, P. Schuddinck, D. Yakimets, P. Raghavan, and G. Groeseneken, IEEE Electron Dev. Lett. 38, 9 (2017).

F. Lime, O. Moldovan, and B. Iñiguez, IEEE Trans. Electron Dev. 61, 3036 (2014).

C. J. Su, T. Tsai, Y. L. Liou, Z. M. Lin, H. C. Lin, and T. S. Chao, IEEE Electron Dev. Lett. 32, 521 (2011).

S. Sahay and M. J. Kumar, IEEE Trans. Electron Dev. 63, 3790 (2016).

Y. Pratap, M. Kumar, S. Kabra, S. Haldar, R. S. Gupta, and M. Gupta, J. Comput. Electron. 17, 288 (2017).

O. Moldovan, F. Lime, and B. Iniguez, IEEE Trans. Electron Dev. 61, 3042 (2014).

S. Guin, M. Sil, and A. Malik, IEEE Trans. Electron Dev. 64, 953 (2017).

S. Tayal and A. Nandi, Mater. Sci. Semicond. Process. 80, 63 (2018).

D. Tekleab, IEEE Electron Dev. Lett. 35, 506 (2014).

D. Moon, S. J. Choi, J. P. Duarte, and Y. K. Choi, IEEE Trans. Electron Dev. 60, 1355 (2013).

S. Sahay and M. J. Kumar, IEEE Trans. Electron Dev. 64, 21 (2017).

S. Sahay and M. J. Kumar, IEEE Trans. Electron Dev. 64, 3007 (2017).

A. Kundu, A. Dasgupta, R. Das, S. Chakraborty, A. Dutta, and C. K. Sarkar, Superlatt. Microstruct. 94, 60 (2016).

B. Jena, K. P. Pradhan, P. K. Sahu, S. Dash, G. P. Mishra, and S. K. Mohapatra, Electron. Energet. 28, 637 (2015).

B. Jena, K. P. Pradhan, D. Dash, G. P. Mishra, P. K. Sahu, and S. K. Mohapatra, Adv. Nat. Sci.: Nanosci. Nanotechnol. 6, 035010 (2015).

H. Wong and H. Iwai, Microelectron. Eng. 83, 1867 (2006).

Silvaco T-CAD Version: ATLAS 5.19.20.R (2020).

K. Kita and A. Toriumi, Appl. Phys. Lett. 94, 132902 (2009).

H. Kai, W. Xiaolei, Y. Hong, and W. Wenwu, J. Semicond. 36, 036004 (2015).

J. Robertson and B. Falabretti, J. Appl. Phys. 100, 014111 (2006).

P. Kasturi, M. Saxena, M. Gupta, and R. S. Gupta, IEEE Trans. Electron Dev. 55, 372 (2008).

R. K. Sharma, R. Gupta, M. Gupta, and R. S. Gupta, IEEE Trans. Electron Dev. 56, 1284 (2009).

R. K. Baruah and R. P. Paily, IEEE Trans. Electron Dev. 61, 123 (2014).

S. Rewari, V. Nath, S. Haldar, S. S. Deswal, and R. S. Gupta, Springer Microsyst. Technol. 25, 1537 (2017).

N. Mohankumar, B. Syamal, and C. K. Sarkar, IEEE Trans. Electron Dev. 57, 820 (2010).

C. W. Lee, I. Ferain, A. Afzalian, R. Yan, N. D. Akhavan, P. Razavi, and J. P. Colinge, Solid-State Electron. 54, 97 (2010).

D. Nagy, G. Indalecio, A. J. G. Loureiro, M. A. Elmessary, K. Kalna, and N. Seoane, IEEE J. Electron Dev. Soc. 6, 332 (2018).

N. Boukortt, B. Hadri, S. Patane, A. Caddemi, and G. Crupi, Silicon 9, 885 (2017).

A. Pouydebasque, S. Denorme, N. Loubet, R. Wacquez, J. Bustos, F. Leverd, E. Deloffre, S. Barnola, D. Dutartre, P. Coronel, and T. Skotnicki, IEEE Trans. Nanotechnol. 7, 551 (2008).

P. Zheng, Y. B. Liao, N. Damrongplasit, M. H. Chiang, and T. J. K. Liu, IEEE Trans. Electron Dev. 61, 3949 (2014).

V. Pott, K. E. Moselund, D. Bouvet, L. D. Michielis, and A. M. Ionescu, IEEE Trans. Nanotechnol. 7, 733 (2008).

X. Zhang, D. Connelly, P. Zheng, H. Takeuchi, M. Hytha, R. J. Mears, and T. J. K. Liu, IEEE Trans. Electron Dev. 63, 1502 (2016).

Y. B. Liao, M. H. Chiang, N. Damrongplasit, W. C. Hsu, and T. J. K. Liu, IEEE Trans. Electron Dev. 61, 2371 (2014).

P. Razavi and G. Fagas, Appl. Phys. Lett. 103, 063506 (2013).

J. P. Colinge, A. Kranti, R. Yan, C. W. Lee, I. Ferain, R. Yu, N. D. Akhavan, and P. Razavi, Solid State Electron. 65, 33 (2011).

Sanjay, B. Prasad, and A. Vohra, Semiconductors 54, 1490 (2020).

Funding

One of the authors (Sanjay) acknowledges the financial support in the form of SRF from University Grants Commission (UGC), New Delhi, India during the course of this work.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

The authors declare that they have no conflict of interest.

Rights and permissions

About this article

Cite this article

Sanjay, Prasad, B. & Vohra, A. Performance Evaluation of Inversion Mode and Junctionless Dual-Material Double-Surrounding Gate Si Nanotube MOSFET for 5-nm Gate Length. Semiconductors 55, 936–942 (2021). https://doi.org/10.1134/S1063782621040151

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1134/S1063782621040151