The transition to Josephson digital circuits with the representation of information in the form of phase jumps of the superconducting order parameter on heterostructures promises a radical increase in the degree of integration while maintaining high speed and energy efficiency. However, it is not yet possible to manufacture reproducible bistable Josephson junctions, which are necessary for the functioning of the previously proposed basic units of the phase logic. To solve this problem, the concept of phase logic based on π junctions is proposed and analyzed within the resistive model of Josephson heterostructures. The potential energy of such junctions has a single minimum, with a difference in the order parameters of the electrodes equal to π. It is demonstrated that the use of π junctions allows one to implement the entire set of logic devices necessary for the operation of digital computing devices based on phase logic.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

INTRODUCTION

Digital superconducting electronics, using the features of the Josephson effect and macroscopic quantum interference in superconducting circuits, allows one to create advanced analog-to-digital and digital-to-analog converters, decimation filters, time measuring systems, correlators, and arithmetic logic devices with unique performance and energy efficiency [1–12]. At a typical clock frequency of 20 GHz, the dynamic dissipation power per Josephson junction can be increased to 13 nW [2]. Josephson devices can also help dealing with superconducting quantum computing systems [13–18].

For the wide application of digital circuits based on fast single-quantum (FSQ) logic with the representation of information in the form of the presence/absence of a magnetic flux quantum Ф0 in the superconducting circuit of a logic cell, it is critically important to reduce their characteristic dimensions. Existing estimates [19] for the maximum element density in circuits using geometric inductance for information storage and superconducting “strips” for connections provide about 107 Josephson junctions per square centimeter. Further reduction of the planar dimensions of cells and distances between them is problematic because of the almost exponential growth of mutual inductances and crosstalk. The problem of miniaturization is especially significant in Josephson circuits intended for operation at ultralow temperatures in hybrid quantum–classical computers, where it is necessary to reduce the critical current of heterostructures in order to avoid excessive heating of the cryogenic system.

A promising solution to this problem is the transition to the so-called phase logic, which is based on two basic principles:

—Information is stored in the phase of the bistable Josephson element rather than in the presence/absence of a magnetic flux quantum in the basic cell.

—Circuit solutions are free of connecting inductances; i.e., electrical circuits contain only Josephson junctions.

A pair of logic states 0 and 1 can be obtained even using a single bistable Josephson junction [20–24]. In this case, the information-storage element of logic devices is reduced to this single junction. Its state is determined by which of the two energy minima corresponding to the phase jump of the order parameter (element phase) \(\varphi = {{\varphi }_{0}}\) or \(\varphi = {{\varphi }_{1}}\) it is currently in. The information propagation corresponds to the wave of the phase change in the superconducting order parameter rather than to the propagation of the fluxon.

The proposed approach was used to develop compact, energy-efficient circuits for the practical implementation of phase logic and memory [25, 26]. It was demonstrated that the characteristic planar dimensions of digital devices can be an order of magnitude smaller than traditional FSQ implementations (the area on the chip for an 8-bit adder can be reduced from more than 200 to 22 µm2) [25]. Unfortunately, to date, the manufacture of bistable Josephson junctions with specified and reproducible parameters is only at the development stage.

In this work, we demonstrate that workable digital phase logic circuits can be designed on the basis of combinations of 0 and π junctions (with a current–phase dependence shifted by π), which provide the basic unit bistability necessary for this logic to work. It should be noted that the technology for manufacturing 0 and π junctions is well developed at present [27–31].

GENERAL PRINCIPLES OF THE OPERATION OF PHASE LOGIC CIRCUITS

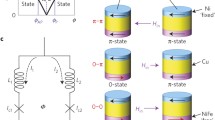

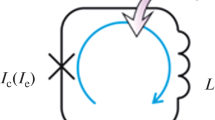

Figure 1 demonstrates the diagram of the basic unit of the phase logic on which elements with two stable physically distinguishable states are presented in the form of eight-pointed crosses, which correspond to phases of potential energy minima \({{\varphi }_{0}}\) and \({{\varphi }_{1}}\) (\(0 \leqslant {{\varphi }_{1}} < \pi \) and \(\pi \leqslant {{\varphi }_{2}} < 2\pi \)). Note the absence of inductances in the basic unit, which are intended to store magnetic flux quanta. In the supply Josephson transmission lines, all connecting geometric inductances are also replaced by Josephson ones.

Information in this basic unit is stored in the phase of the element Jm: its potential energy has two minima at \(\varphi = {{\varphi }_{1}}\) and \({{\varphi }_{2}}\), respectively. The Josephson junctions Jin and Jout are the input and output ports of the circuit, respectively. The element Jl connects the information-storage element Jm to the output of the circuit Jout. Its parameters primarily affect the state reading mechanism. The bistable element \({{J}_{v}}\) connects the input of the circuit to Jm, acting as a phase converter at the input of the unit.

Depending on the parameters of the phase converter (which can be either one bistable junction \({{J}_{v}}\) or a serial connection of a pair of Josephson heterostructures [32]), the basic unit can perform all the modes necessary to implement the most common digital devices. Let us further consider the dynamic processes in the basic unit for the limiter mode, transmission line mode, and digital frequency divider mode.

In the limiter mode (top panel of Fig. 1), the incoming phase jump of the superconducting order parameter generates currents in the input cell, which lead to a phase change at the junction Jin and the converter element \({{J}_{v}}\) by ~2π. However, the relation between the Josephson energies and the characteristic times of the processes for \({{J}_{v}}\) and Jm is such that the phase converter switches between stable states before the information storage unit. The element Jm and the output cell remain in this mode in their original equilibrium states. The phase difference jump at the output of the unit is not formed. Sequential switching of Josephson junctions (Jin) and bistable elements (\({{J}_{v}}\)) is demonstrated by arrows in the top panel of Fig. 1.

In the transmission line mode (middle panel of Fig. 1), the converter \({{J}_{v}}\) switches slowly, and the phase jump wave applied to the input creates a high current through it, changing the phases of the junction Jin, as well as the central element Jm and the output cell Jout by ~2π. In this case, the input pulse carrying the phase change by 2π passes through the basic unit without changing its state. Sequential switching of Josephson junctions (Jin, Jout) and bistable elements (Jm) is also demonstrated in the middle panel of Fig. 1 by arrows.

For intermediate values of the switching speed between stable states (\({{\varphi }_{{0v}}}\) and \({{\varphi }_{{1v}}}\)) of the converter \({{J}_{v}}\), under the action of information coming to the input, the information-storage element Jm has time to change its phase from \({{\varphi }_{0}}\) to \({{\varphi }_{1}}\). As a result, the status of the basic unit as a whole changes from 0 to 1; i.e., a write operation occurs. In the bottom panel of Fig. 1, this is indicated by half of the standard arrow. Note that the amplitude of the current pulse arising in the output cell (Jl − Jout) after one wave of phase jumps arriving at the input is not enough to switch the junction Jout. However, after switching the basic element Jm, the state of the output cell changed: the current began to circulate in it (what can be used to read information). When the circulating current is added to the current pulse caused by the next phase change wave applied to the input, Jout switches between its stable states (with phases 0 and 2π) and generates a phase change wave into the output line. In this case, the information-storage element Jm returns from the state 1 to the state 0. In the bottom panel of Fig. 1, this is indicated by the second half of the standard arrow. It can be concluded that the basic unit in this case operates as a digital frequency divider in half: every second pulse passes to the output of the circuit. It was shown [25] that on the basis of circuits with the described functionality, it is possible to implement logic elements, memory with destructive and nondestructive readout, RS and T flip-flops, half-adders, and more complex components of computing devices.

PHASE LOGIC CIRCUTS BASED ON π JUNCTIONS

In [21, 33–36], it was demonstrated how the coexistence of 0 and π junctions allows obtaining a bistable φ junction. The key idea of this work is that the required bistable elements of the phase logic unit can be created by combining relatively easy-to-make 0 and π Josephson junctions. Figure 2 demonstrates a version of the basic logic unit, in which the phase converter \({{J}_{v}}\) is made as a combination of 0 and π junctions (J0C and JπC). The π structure can also be used as the central element of the unit Jm.

The total Josephson energy of the input cell, consisting of the junctions Jin, J0C, JπC, and Jm, as a function of the phase difference at the junctions Jin and Jm, has two local minima (see Fig. 3). It can be seen that the phase in stable states is equal to π + 2πn at π junctions and to 2πn at 0 junctions, where n is an integer.

(Color online) Josephson energy of the input cell and the central element of the basic unit of phase logic on 0 and π junctions (in the frequency divider mode) versus the phases in Jm and Jin heterostructures. The stable logic states 0 and 1 for the system under consideration are highlighted. The critical currents of the J0C and JπC junctions are 1.2 and –0.35 of the critical current of the Jin junction, respectively. Normalized supply currents are \({{i}_{b}} = 0.77\) and \(i = 0.4\).

In this case, the input cell has an even number of π junctions, the total phase shift of the order parameter along the circuit is 2πn, and there is no circulating current. This excludes unwanted feedback on the other units and allows one to conveniently connect phase logic circuits to standard FSQ logic elements. Note that a bistable input cell could be obtained without the use of π junctions, by introducing instead of them a large number of series-connected 0 structures that provide the phase shift of the order parameter.

The output cell has an odd number of π junctions, so the difference between the phase Jm and the phase of 0 junctions creates a circulating current in it, which can flow in two directions, which allows one to read the state of the unit. This forces a drop in the phase of the order parameter π on the element Jl. It turns out that, for the stable operation of the circuit, it is optimal to implement such an element in the form of a stack consisting of three junctions Jl1–3 connected in series.

To demonstrate the operability of all the key information processing modes listed above, the dynamic processes in the basic unit demonstrated in Fig. 2 are considered. When modeling the control processes and reading the state of the basic unit, the transmission lines consisting only of Josephson junctions will be considered [25]. The system of differential equations, taking into account the balance of currents for each node, was written within the generalized resistive model and was solved using the fourth and fifth order Runge–Kutta methods, as well as the Gauss method for solving systems of linear equations. For the jth Josephson junction in the unit, the equation of motion has the form

where \({{i}_{{\Sigma j}}}\) is the total current flowing into the junction, iCj is the critical current, and \({{\alpha }_{j}}\) is the damping factor. All currents are represented in units of the critical current of the input junction; the dot denotes the differentiation with respect to the time τ measured in units of the characteristic time of the input junction τC.

Figure 4 demonstrates the time dependences of the phase on the junctions of the unit for the three modes, which occur after phase change waves sequentially reach the input.

(Color online) Phases on the junctions of the unit versus the time measured in units of \({{\tau }_{C}}\) for the modes of (a) limiter mode at \({{i}_{{\pi C}}} = - 0.05\) and \({{i}_{{0C}}} = 0.1\), (b) transmission line at \({{i}_{{\pi C}}} = - 0.2\) and \({{i}_{{0C}}} = 1.2\), and (c) digital frequency divider at \({{i}_{{\pi C}}} = - 0.35\) and \({{i}_{{0C}}} = 1.2\). Normalized supply currents are shown in Fig. 3; \({{\alpha }_{{0C}}} = 0.8\) and \({{\alpha }_{{\pi C}}} = 0.9\).

Thus, in the limiter mode (Fig. 4а), when the critical current of the junction JπC is slightly less than that of the junction J0C, the π structure is the “weak point” in the input cell, at which a phase jump of ~2π occurs. In this case, the phases of the junctions Jm and Jout hardly change. In the transmission line mode (Fig. 4b), each phase change wave at the input changes the phase of the junctions Jm and Jout by 2π and then propagates to the output transmission line. The pulses pass through the basic unit without changing its state: at the end of the calculation given for illustration, π + 8π. In the frequency-halving mode, each pulse at the input changes the phase of the junction Jm by ~π (i.e., in this case, \({{\varphi }_{1}} \approx \pi \) and \({{\varphi }_{2}} \approx 2\pi \)), but only every second pulse changes the phase of the junction Jout by 2π.

It is possible to select the operating mode of the unit (limiter, transmission line, digital frequency divider) by selecting the critical currents i0C and iπC of the 0 and π junctions, respectively (Fig. 5). It is clearly seen that the limiter mode is implemented when switching between neighboring stable states in the phase converter in the input cell occurs earlier than in Jm. It can be seen from the equation of motion (1) that the rate of phase change at the junction is determined by the parameter \({{\alpha }_{j}}\). However, if the slow junction has a relatively low critical current, it may start switching earlier. For the frequency-halving mode, intermediate values of the speed of this element in the proposed phase logic unit are needed.

(Color online) (Blue) limiter, (yellow) transmission line, and (cyan) frequency-halving operation modes of the basic unit of phase logic on 0 and π junctions on the plane of the junction parameters \({{i}_{{\pi C}}}\) and \({{i}_{{0C}}}\) of the phase converter in the input cell. Normalized supply currents and damping coefficients are the same as in Figs. 3 and 4.

PRACTICAL IMPLEMENTATION OF THE BASIC UNIT OF PHASE LOGIC ON π JUNCTIONS

In practice, 0 Josephson junctions are usually superconductor–insulator–superconductor (SIS) tunnel heterostructures of the “sandwich” type. Compatible with FSQ circuits and quantum registers, π junctions are created in the form of superconductor–ferromagnet–superconductor (SFS) heterostructures with a sufficiently large critical current and a low resistance in the normal state [27, 28, 37, 38]. As a consequence, such π Josephson junctions have a low characteristic voltage and a low characteristic frequency [39–42]. Taking into account a low speed of π junctions in comparison with 0 junctions, we found that the operation of the cell is slowed. Figure 6 demonstrates that the duration of one working cycle of the circuit increases by a factor of about 1.5. In addition, the frequency-halving region on the plane of the junction parameters, which is a part of the phase converter, is narrowed (Fig. 5). This problem can be solved by switching to stacks, starting from the concept of a superconductor–insulator–superconductor–ferromagnet–superconductor (SIsFS) heterostructure. For such composite junctions, the characteristic v-oltage and frequency are of the same order as for tunnel Josephson junctions used in FSQ logic circuits [39–42].

(Color online) Time dependences of the normalized voltage, \(d\varphi {\text{/}}d\tau \), at the (blue lines) input and (red lines) output of the basic π unit for (a) identical resistances of 0 and π junctions (\({{\alpha }_{{0C}}} = 0.8\), \({{\alpha }_{{\pi C}}} = 0.9\), and \({{\alpha }_{m}} = 1\)), and (b) low resistances of π junctions (\({{\alpha }_{{0C}}} = 0.8\), \({{\alpha }_{{\pi C}}} = 9\), and \({{\alpha }_{m}} = 10\)).

The use of nanoscale (with an area of 18 000–30 000 nm2) Josephson junctions with a weak bond region made of a normal metal, constructed in the form of a bridge of variable thickness, is also promising [43, 44]. Since the functional geometric inductance is replaced by the Josephson one in the proposed basic unit, such a solution will provide a particularly noticeable gain in the compactness of the developed digital devices. Using this approach, π junctions can be obtained by using additional magnetic insulating layers in the weak-coupling region.

CONCLUSIONS

To summarize, a circuit has been proposed to implement the entire functionality of phase logic circuits without using bistable Josephson junctions [45], which are difficult to manufacture. At the same time, one of the key advantages of the approach under consideration, i.e., small planar dimensions of the circuits and, as a result, the possibility of achieving a high degree of integration for Josephson digital devices, can be retained. To reduce the planar dimensions of the proposed block, Josephson junctions (e.g., junctions Jl1–3 in the output cell) can be made in the form of a compact stack [46].

The planar size of the proposed basic unit can be estimated as the sum of the areas of all Josephson junctions of the circuit and the sum of the areas of connections between them. Under the assumption that the areas of all junctions are equal to S, and the same area is occupied by the connections, then the area of the basic unit is 14S. In the case of the MIT LL technology for superconductor–insulator–superconductor tunnel structures, \(S \approx 0.4\) μm2 [47], and the area of the basic unit will be approximately 5.6 μm2. In the case of a nanoscale Josephson junction with a weak bond region made of a normal metal, constructed in the form of a bridge of variable thickness [43], the required area is \(S \approx 0.018\) μm2, and the area of the basic unit is 0.252 μm2. The indicated marks make the prospects for the practical implementation of the Josephson phase logic circuit based on π junctions very relevant.

Change history

19 January 2023

An Erratum to this paper has been published: https://doi.org/10.1134/S0021364022380039

REFERENCES

D. S. Holmes, A. L. Ripple, and M. A. Manheimer, IEEE Trans. Appl. Supercond. 23, 1701610 (2013).

O. A. Mukhanov, IEEE Trans. Appl. Supercond. 21, 760 (2011).

F. Kirichenko, I. V. Vernik, J. A. Vivalda, R. T. Hunt, and D. T. Yohannes, IEEE Trans. Appl. Supercond. 25, 1300505 (2015).

S. K. Tolpygo, Low Temp. Phys. 42, 361 (2016).

I. I. Soloviev, N. V. Klenov, S. V. Bakurskiy, M. Y. Kupriyanov, A. L. Gudkov, and A. S. Sidorenko, Beilstein J. Nanotechnol. 8, 2689 (2017).

S. K. Tolpygo, V. Bolkhovsky, R. Rastogi, S. Zarr, A. L. Day, E. Golden, T. J. Weir, A. Wynn, and L. M. Johnson, IEEE Trans. Appl. Supercond. 29, 1102513 (2019).

S. K. Tolpygo, V. Bolkhovsky, T. J. Weir, A. Wynn, D. E. Oates, L. M. Johnson, and M. A. Gouker, IEEE Trans. Appl. Supercond. 26, 1 (2016).

S. K. Tolpygo, V. Bolkhovsky, S. Zarr, T. J. Weir, A. Wynn, A. L. Day, L. M. Johnson, and M. A. Gouker, IEEE Trans. Appl. Supercond. 27, 1100815 (2017).

S. K. Tolpygo, V. Bolkhovsky, D. E. Oates, R. Rastogi, S. Zarr, A. L. Day, T. J. Weir, A. Wynn, and L. M. Johnson, IEEE Trans. Appl. Supercond. 28, 1100212 (2018).

V. K. Semenov, Y. A. Polyakov, and S. K. Tolpygo, IEEE Trans. Appl. Supercond. 29, 1302809 (2019).

A. Inamdar, J. Ravi, S. Miller, S. S. Meher, M. E. Celik, and D. Gupta, IEEE Trans. Appl. Supercond. 31, 1301307 (2021).

C. L. Ayala, T. Tanaka, R. Saito, M. Nozoe, N. Takeuchi, and N. Yoshikawa, IEEE J. Solid-State Circuits 56, 1152 (2020).

P. Krantz, M. Kjaergaard, F. Yan, T. P. Orlando, S. Gustavsson, and W. D. Oliver, Appl. Phys. Rev. 6, 021318 (2019).

I. I. Soloviev, N. V. Klenov, A. L. Pankratov, L. S. Revin, E. Il’ichev, and L. S. Kuzmin, Phys. Rev. B 92, 014516 (2015).

A. Opremcak, I. V. Pechenezhskiy, C. Howington, B. G. Christensen, M. A. Beck, E. Leonard, Jr., J. Suttle, C. Wilen, K. N. Nesterov, G. J. Ribeill, T. Thorbeck, F. Schlenker, M. G. Vavilov, B. L. T. Plourde, R. McDermott, Science (Washington, DC, U. S.) 361 (6408), 1239 (2018).

C. Howington, A. Opremcak, R. McDermott, A. Kirichenko, O. A. Mukhanov, and B. L. Plourde, EEE Trans. Appl. Supercond. 29 (5), 1 (2019).

L. Howe, M. Castellanos-Beltran, A. J. Sirois, D. Olaya, J. Biesecker, P. D. Dresselhaus, S. P. Benz, and P. F. Hopkins, arXiv: 2111.12778 (2021).

M. V. Bastrakova, N. V. Klenov, V. I. Ruzhickiy, I. I. Soloviev, and A. M. Satanin, Supercond. Sci. Technol. 35, 055003 (2022).

S. K. Tolpygo, V. Bolkhovsky, R. Rastogi, S. Zarr, A. L. Day, T. J. Weir, A. Wynn, and L. M. Johnson, arXiv: 1704.07683 (2017).

A. Buzdin and A. Koshelev, Phys. Rev. B 67, 220504 (2003).

S. V. Bakurskiy, N. V. Klenov, T. Yu. Karminskaya, M. Yu. Kupriyanov, and A. A. Golubov, Supercond. Sci. Technol. 26, 015005 (2013).

A. Pal, Z. H. Barber, J. W. A. Robinson, and M. G. Blamire, Nat. Commun. 5, 3340 (2014).

S. V. Bakurskiy, V. I. Filippov, V. I. Ruzhickiy, N. V. Klenov, I. I. Soloviev, M. Yu. Kupriyanov, and A. A. Golubov, Phys. Rev. B 95, 094522 (2017).

M. J. A. Stoutimore, A. N. Rossolenko, V. V. Bolginov, V. A. Oboznov, A. Y. Rusanov, D. S. Baranov, N. Pugach, S. M. Frolov, V. V. Ryazanov, and D. J. van Harlingen, Phys. Rev. Lett. 121, 177702 (2018).

I. I. Soloviev, V. I. Ruzhickiy, S. V. Bakurskiy, N. V. Klenov, M. Yu. Kupriyanov, A. A. Golubov, O. V. Skryabina, and V. S. Stolyarov, Phys. Rev. Appl. 16, 014052 (2021).

I. Salameh, E. G. Friedman, and S. Kvatinsky, IEEE Trans. Circuits Syst. II: Express Briefs 69, 2533.

V. V. Ryazanov, V. A. Oboznov, A. Y. Rusanov, A. V. Veretennikov, A. A. Golubov, and J. Aarts, Phys. Rev. Lett. 86, 2427 (2001).

T. Kontos, M. Aprili, J. Lesueur, F. Gent, B. Stephanidis, and R. Boursier, Phys. Rev. Lett. 89, 137007 (2002).

V. A. Oboznov, V. V. Bol’ginov, A. K. Feofanov, V. V. Ryazanov, and A. I. Buzdin, Phys. Rev. Lett. 96, 197003 (2006).

A. A. Bannykh, J. Pfeiffer, V. S. Stolyarov, I. E. Batov, V. V. Ryazanov, and M. Weides, Phys. Rev. B 79, 054501 (2009).

V. V. Bolginov, A. N. Rossolenko, A. B. Shkarin, V. A. Oboznov, and V. V. Ryazanov, J. Low Temp. Phys. 190, 302 (2018).

A. A. Golubov, M. Y. Kupriyanov, and E. Il’ichev, Rev. Mod. Phys. 76, 411 (2004).

R. G. Mints, Phys. Rev. B 57, R3222 (1998).

N. G. Pugach, E. B. Goldobin, R. Kleiner, and D. Koelle, Phys. Rev. B 81, 104513 (2010).

E. Goldobin, D. Koelle, and R. Kleiner, Phys. Rev. B 91, 214511 (2015).

D. M. Heim, N. G. Pugach, M. Yu. Kupriyanov, E. Goldobin, D. Koelle, R. Kleiner, N. Ruppelt, M. Weides, and H. Kohlstedt, New J. Phys. 17, 113022 (2015).

A. K. Feofanov, V. A. Oboznov, V. V. Bol’ginov, J. Lisenfeld, S. Poletto, V. V. Ryazanov, A. N. Rossolenko, M. Khabipov, D. Balashov, A. B. Zorin, P. N. Dmitriev, V. P. Koshelets, and A. V. Ustinov, Nat. Phys. 6, 593 (2010).

S. K. Tolpygo, V. Bolkhovsky, R. Rastogi, S. Zarr, A. L. Day, E. Golden, T. J. Weir, A. Wynn, and L. M. Johnson, IEEE Trans. Appl. Supercond. 29, 1101208 (2019).

T. I. Larkin, V. V. Bol’ginov, V. S. Stolyarov, V. V. Ryazanov, I. V. Vernik, S. K. Tolpygo, and O. A. Mukhanov, Appl. Phys. Lett. 100, 222601 (2012).

S. V. Bakurskiy, N. V. Klenov, I. I. Soloviev, V. V. Bol’ginov, V. V. Ryazanov, I. V. Vernik, O. A. Mukhanov, M. Yu. Kupriyanov, and A. A. Golubov, Appl. Phys. Lett. 102, 192603 (2013).

S. V. Bakurskiy, N. V. Klenov, I. I. Soloviev, M. Yu. Kupriyanov, and A. A. Golubov, Phys. Rev. B 88, 144519 (2013).

L. N. Karelina, R. A. Hovhannisyan, I. A. Golovchanskiy, V. I. Chichkov, A. Ben Hamida, V. S. Stolyarov, L. S. Uspenskaya, Sh. A. Erkenov, V. V. Bolginov, and V. V. Ryazanov, J. Appl. Phys. 130, 173901 (2021).

I. I. Soloviev, S. V. Bakurskiy, V. I. Ruzhickiy, N. V. Klenov, M. Yu. Kupriyanov, A. A. Golubov, O. V. Skryabina, and V. S. Stolyarov, Phys. Rev. Appl. 16, 044060 (2021).

L. N. Karelina, V. V. Bolginov, Sh. A. Erkenov, S. V. Egorov, I. A. Golovchanskiy, V. I. Chichkov, A. Ben Hamida, and V. V. Ryazanov, JETP Lett. 112, 705 (2020).

V. I. Ruzhickiy, A. A. Maksimovskaya, I. I. Soloviev, S. V. Bakurskiy, and N. V. Klenov, J. Exp. Theor. Phys. 132, 800 (2021).

M. A. Castellanos-Beltran, D. I. Olaya, A. J. Sirois, P. D. Dresselhaus, S. P. Benz, and P. F. Hopkins, IEEE Trans. Appl. Supercond. 29, 1300705 (2019).

S. K. Tolpygo, V. Bolkhovsky, R. Rastogi, S. Zarr, E. Golden, T. J. Weir, L. M. Johnson, V. K. Semenov, and M. A. Gouker, in Proceedings of the Applied Superconductivity Conference, ASC 2020, IEEE Supercond. News Forum 15 (49), STP669 Wk1EOr3B-01 (2021). https://snf.ieeecsc.org/issues/snfissue-no49-march-2021.

Funding

This work was supported by the Russian Science Foundation, project no. 20-12-00130 (simulation of dynamic processes in phase logic units), and by the Interdisciplinary Scientific and Educational School “Photonic and Quantum Technologies. Digital Medicine” at Moscow State University (access to the necessary scientific and technical literature).

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

The authors declare that they have no conflicts of interest.

Additional information

Translated by R. Bando

Rights and permissions

Open Access. This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Maksimovskaya, A.A., Ruzhickiy, V.I., Klenov, N.V. et al. Phase Logic Based on π Josephson Junctions. Jetp Lett. 115, 735–741 (2022). https://doi.org/10.1134/S0021364022600884

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1134/S0021364022600884