Abstract

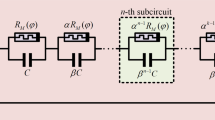

Consideration was given to a controllable architecture enabling easy, simple and prompt self-testing in the programmable logic matrix. An approach was proposed to reduce the amount of self-testing hardware by compacting the test response by mod 2 convolution schemes through reconfiguration of the subject of diagnosis programmed in the matrix and using its standard connections.

Similar content being viewed by others

References

Li, L., Chakrabarty, K., Kajihara, S., and Swaminathan, S., Three-stage Compression Approach to Reduce Test Data Volume and Testing Time for IP Cores in SOCs, IEE Proc., online no. 20045150.

Lee, L.-J., Tseng, W.-D., Lin, R.-B., and Chang, C.-H., 2n-pattern Run-length for Test Data Compression, IEEE Trans. Comput. Aided Design Integr. Circ. Syst., 2012, vol. 31, no. 4, pp. 644–648.

Mukherjee, N., Rajski, J., and Tyszer, J., High Volume Diagnosis in Memory BIST-based on Compressed Failure Data, IEEE Trans. Comput. Aided Design Integr. Circ. Syst., 2010, vol. 29, no. 3, pp. 441–453.

Sinanoglu, O., All-Mulla, M., and Taha, M., Utilization of Inverse Compatibility for Test Cost Reduction, IET Comput. Digit. Tech., 2009, vol. 3, no. 2, pp. 195–204.

Tenentes, V., Kavousianos, X., and Kalligeros, E., Single and Variable-state-skip LFSRs: Bridging the Gap between Test Data Compression and Test Set Embedding for IP Cores, IEEE Trans. Comput. Aided Design Integr. Circ. Syst., 2010, vol. 29, no. 10, pp. 1640–1644.

Mitra, S. and Kim, K.S., X-compact: An Efficient Response Compaction Technique, IEEE Trans. Comput. Aided Design Integr. Circ. Syst., 2004, vol. 23, no. 3, pp. 421–432.

Lee, K.-J., Lien, W.-C., and Hsieh, T.-Y., Test Response Compaction via Output Bit Selection, IEEE Trans. Comput. Aided Design Integr. Circ. Syst., 2011, vol. 30, no. 10, pp. 1634–1544.

Lee, D. and Roy, K., Viterbi-based Efficient Test Data Compression, IEEE Trans. Comput. Aided Design Integr. Circ. Syst., 2012, vol. 31, no. 4, pp. 610–619.

Aksenova, G.P., Control-ready Architecture for Self-Testing in Programmable Logical Matrix Structures, Autom. Remote Control, 2010, vol. 71, no. 12, pp. 2633–2643.

Aksenova, G.P. and Khalchev, V.F., The Method of Parallel-Sequential Built-in Self-testing in Integrated Circuits of the type SFPGAS, Autom. Remote Control, 2007, vol. 68, no. 1, pp. 149–159.

Author information

Authors and Affiliations

Additional information

Original Russian Text © G.P. Aksenova, 2013, published in Avtomatika i Telemekhanika, 2013, No. 2, pp. 124–138.

Rights and permissions

About this article

Cite this article

Aksenova, G.P. Compaction of test response at self-testing in the programmable logic matrices. Autom Remote Control 74, 264–274 (2013). https://doi.org/10.1134/S0005117913020082

Received:

Published:

Issue Date:

DOI: https://doi.org/10.1134/S0005117913020082