Abstract

Solution processed organic field effect transistors can become ubiquitous in flexible optoelectronics. While progress in material and device design has been astonishing, low environmental and operational stabilities remain longstanding problems obstructing their immediate deployment in real world applications. Here, we introduce a strategy to identify the most probable and severe degradation pathways in organic transistors and then implement a method to eliminate the main sources of instabilities. Real time monitoring of the energetic distribution and transformation of electronic trap states during device operation, in conjunction with simulations, revealed the nature of traps responsible for performance degradation. With this information, we designed the most efficient encapsulation strategy for each device type, which resulted in fabrication of high performance, environmentally and operationally stable small molecule and polymeric transistors with consistent mobility and unparalleled threshold voltage shifts as low as 0.1 V under the application of high bias stress in air.

Similar content being viewed by others

Introduction

Organic semiconductors (OSCs) are emerging as versatile materials that can serve industries ranging from renewable energy to communication, healthcare, security, and space applications. Indeed, molecular and polymeric OSCs will soon become ubiquitous in most sectors of our lives due to their low cost, light weight, and ease of molding into any shape1,2,3. Organic field-effect transistors (OFETs) form the basic building blocks for many of these applications and provide excellent platforms for fundamental studies on charge transport in OSCs4,5,6,7,8. Innovations in material and device design have led to OFET performance that is on par with, and even exceeds that, of amorphous silicon transistors, and are sufficient to enable applications like displays, radio frequency identification tags, conformable sensors, health monitoring systems, and memory devices9,10,11,12,13,14. In addition to the performance requirements, the spatial uniformity and stability upon aging, under mechanical, electrical, chemical, and thermal stress, are essential requirements for their commercialization. The uniformity challenge has been tackled through careful processing, and the success has been remarkable15,16,17. OFET stability, however, is a problem that still requires scrutiny1,18,19,20. Electrical instabilities during operation are manifested as a decrease in the drain current, shift in threshold voltage, reduction in charge-carrier mobility, and increase in subthreshold slope, all of which are preventing the deployment of OFETs in technologically relevant applications. The development of environmentally stable materials has led to robust performance when incorporated in devices21,22. Addressing the operational stability, however, has proven to be a more difficult task1,18,19,20. Charge trapping has been recognized as the main source of device degradation, a phenomenon that is caused by both external factors (oxidation, moisture, impurities), and intrinsic features (semiconductor molecular structure, structural defects, grain boundaries, voids)23,24,25. The demonstration of bias-stress-free operation in single-crystal devices represents a proof-of-concept that stable OFETs can be achieved in highly ordered OSC layers26,27. Subsequent efforts focused on thin-film devices have resulted in remarkable progress through material design, optimization of device architectures, and processing routes28,29. For example, Takimiya and collaborators synthesized defect-resilient materials that enabled the fabrication of OFETs with negligible changes in the ON and OFF state currents during 1000 operation cycles30. By incorporating molecular additives into the OSC films, Sirringhaus and coworkers displaced the water trapped within the nanometer-sized voids and achieved threshold voltage shifts below 1 V after a day of constant current stress24. Kippelen and coworkers fabricated OFETs with gate dielectrics consisting of bilayers of the fluoropolymer Cytop and Al2O3:HfO2 and obtained threshold voltage shifts as low as 0.2 V for over 160 h of operation31.

While these achievements mark milestones in OFET research, they are limited to a narrow material space and address only certain device architectures. Engineering stable devices is challenging since charge-carrier trapping leading to instabilities originates from several competing sources and proceeds via complex mechanisms spanning multiple timescales23. Practical requirements for OFET stability range from a few minutes for disposable electronics to years for OFET-enabled large-area, flexible displays. Different external factors can accelerate the degradation in application-specific settings, i.e., environment (light, moisture, and temperature), bias or current stress level (current, voltage, and time of continuous operation). Device encapsulation or incorporation of solvent additives during film processing indeed provide good solutions for a subset of materials24,32,33, but often fail when transferred to other systems. Clearly, there are no universal strategies that can be adopted, as each system, which consists of a particular material integrated in a specific device structure, is unique and responds differently to external stimuli. Screening for potential degradation pathways is necessary for each case in order to engineer robust devices, but it can be resource and time consuming. Having access to information about the most probable factors and mechanisms triggering device degradation could lead to a fast, rational selection and implementation of the most effective strategy to circumvent the degradation process, and that is unique for each device architecture, composition, and details of operation.

Here, we introduce a method that provides a reliable diagnostic tool for identifying with high accuracy the environmental and operational degradation pathways in several different types of OFETs, and subsequently employ it to eliminate the main sources of instabilities and develop highly stable devices. By monitoring the energetic distribution and time evolution of trap states during OFET operation, and with guidance from density functional theory (DFT) calculations, we gained access to the origins of device degradation, clarified the nature of the traps generated during operation, and the parameter space that gives rise to these traps. This information guided the development of efficient encapsulation pathways that offer selective transparency to some species while blocking the species responsible for degradation. As a result, we delivered robust OFETs with unparalleled operational stability regardless of the composition (small molecule and polymeric OSCs) and configuration (staggered and coplanar), as confirmed by the constant mobility and exceptionally low threshold voltage shift of ΔVth = 0.1 eV achieved under aggressive bias stress conditions for 500 min in ambient air.

Results

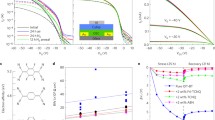

Operational stability measurements on small molecule OFETs

Operational stability tests were first performed on bottom-contact, bottom-gate OFETs with the semiconducting layer consisting of the small molecule tri(n-hexyl)silylethynyl benzodithiophene (TnHS BDT) trimer and SiO2 gate dielectric (Fig. 1)34. The measurements were performed in ambient air (typical humidity ~40%) and in dark, both by acquiring repeated transfer characteristics (drain current ID as a function of gate-source voltage VGS at fixed drain-source voltage VDS)35,36, and by recording the transfer curves before and after the application of a prolonged bias stress22,37,38. Figure 1a shows the transfer characteristics in the saturation regime of a device during repetitive measurements for 500 min. The red curve corresponds to a fresh device. A drastic change in the slope of the curve and a large negative shift in Vth is evident within the first 20 min of operation, and then the changes become less prominent. To examine these changes, in Fig. 1b, we plot the evolution of the charge-carrier mobility, μ, the subthreshold slope S, and the threshold voltage shift, as a function of time. While no statistically relevant changes in the subthreshold slope are observed, a drastic decrease in the mobility (~25%) and large shifts in the threshold voltage (ΔVth ~ –8 V) are evident after the first 20 min of operation, subsequently, both parameters remain constant. The reduction in mobility is indicative of charge-carrier trapping in electronic states generated in the bandgap of the OSC23. The constant S suggests that no significant change occurred in the deep trap distribution, while the shift in Vth together with the decrease in mobility points to the generation of shallow or intermediate electronic states.

a Time evolution of the saturation regime transfer characteristics (ID vs VGS at VDS = −60 V). The left and right axes show the square root and the logarithm of ID, respectively. The channel length and width of the device are 40 μm and 200 μm, respectively. b Time evolution of the mobility μ normalized to the value at t = 0 min (red), subthreshold slope S (blue), and magnitude of threshold voltage shifts |ΔVth| (black). Insets in the top and bottom panels show the device geometry and the molecular structure of the OSC under study. c A subset of the trap DOS spectra evaluated at various times during device operation, offset for clarity in the inset. The curves are plotted as a function of energy from the valence band edge. d The generated trap densities during repeated transistor operation evaluated using threshold voltage shifts (black) and the area under the peak in the DOS spectrum (red), as illustrated in the inset.

Trap DOS analysis

In order to access and monitor the time evolution of the energetic distribution of traps, i.e., the trap density of states (DOS) spectrum, we performed the spectral analysis of the density of trap states23. Figure 1c shows the trap DOS spectra plotted as a function of energy with respect to the valence band edge for a device measured in air. Each curve was evaluated at different times during transistor operation (a subset of the spectra is shown here for clarity and a complete set, as well as the functions used in the analysis, are provided in Supplementary Fig. 1). At t = 0 min (red curve) and t = 5 min (orange curve), the DOS resembles an exponential function, with the majority of electronic states distributed in the vicinity of the band edge. This type of trap distribution is typical for polycrystalline OSCs and the electronic states tailing into the bandgap arise from disorder within the crystal due to thermal molecular motions and/or structural defects23. At t = 15 min (yellow curve), the formation of a peak at 0.31 eV is evident, which is then followed by an increase in the peak amplitude starting at t = 20 min (green curve). This peak is the result of the generation of discrete electronic states in the bandgap of the OSC during operation and its location (i.e., several kT from the band edge, where k is the Boltzmann constant and T is the temperature) suggests that the traps that forms lie at intermediate energies, between shallow and deep. The DOS spectra remain unchanged after 20 min, indicating that no additional electronic states are generated during the remaining period of transistor operation, which explains why the device parameters remain constant. We modeled the DOS curves in Fig. 1c using two exponential functions to describe the distribution of shallow and deep states, respectively, with the addition of a Gaussian distribution to account for the presence of the peak. A 50% increase in the shallow trap density between the first and last measurement, and an order of magnitude increase in the deep trap density, respectively, is evident, along with a 30% and 24% decrease in the characteristic width of the shallow and deep states, respectively (Supplementary Table 1, Supplementary Fig. 2). This narrowing of the DOS occurs to accommodate the additional electronic states generated during operation that causes the peak in the DOS spectrum that is accounted for by the Gaussian centered at 0.31 eV. To quantify the increase in the density of traps as a function of time (Ntrap (t)), and hence determine the number of traps generated during operation, and that are responsible for the device degradation, the difference between the area under the peak of the DOS spectrum and the baseline spectrum (at t = 0 min) was evaluated for each curve; the results are shown in Fig. 1d, along with the value of the generated trap densities determined from the shifts in Vth. After a subsequent rest period, the mobility and the threshold voltage were recovered (Supplementary Fig. 3a) and the trap DOS spectrum became identical to that of the fresh device (Supplementary Fig. 3b), suggesting that the generated electronic states are metastable and persist only during operation.

The above experimental observations and analysis clarified that the source of device instabilities is charge trapping in intermediate bandgap states occurring under operation in air. To establish the precise nature of the predominant traps and the factors that lead to their formation, we performed several experiments and computational analyses. First, we repeated the measurements under vacuum (∼10−6 Torr) to decouple the environmental and operational degradation processes and investigate the sole effect of bias stress on the device performance and trap dynamics. The evolution of the DOS spectrum is included in Fig. 2. Clearly, a peak does not form, confirming that bias stress alone is not responsible for the generation of electronic traps around 0.31 eV observed for the device tested in air. A 50% decrease in the density of deep traps with a narrowing of the DOS by ~10%, and a two orders of magnitude reduction in shallow trap densities, with a 50% decrease in the characteristic width, occur after 500 min of operation (Supplementary Table 2 and Supplementary Fig. 4). The reduction in the trap density is a consequence of the de-gassing step that removes air from the film. The likely candidate for doping is residual oxygen (O2), which can cause p-type doping as observed in many small molecules and conjugated polymers39. Oxygen doping is also supported by the changes in the current–voltage characteristics of the device in ambient compared to vacuum (Supplementary Fig. 5), i.e. the increase in OFF current by two orders of magnitude and a large positive shift in the threshold voltage (ΔVth = 26 V). In Supplementary Fig. 6 we include a comparison of the evolution of device properties during operational stability tests performed under vacuum, and ambient, respectively. While the mobilities decay at similar rates, larger shifts in Vth are observed in vacuum. P-dopants create acceptor-like states in the bandgap, increasing the hole concentration in the transistor channel and in their absence, a higher gate-voltage is required to accumulate mobile charges. With time, the shifts in Vth become larger as more dopant molecules are gradually evacuated, until all dopants are removed, and the shifts saturate. This observation highlights that the presence of O2 molecules, i.e., oxygen doping, is necessary in generating the required charge concentration to yield high performance in these devices.

We then examined the effect of environmental contaminants on the DOS spectrum and device stability by eliminating bias stress. Freshly made devices were measured in air, then stored under ambient air, in dark, and the transfer characteristics were recorded daily over a period of 40 days. The device parameters remain constant (Supplementary Fig. 7a), the DOS spectra did not show any statistically relevant change, and the peak observed under continuous operation in ambient is absent (Supplementary Fig. 7b). These cumulative measurements suggest that the electronic states leading to device degradation are generated only when bias stress and environmental effects are simultaneously present and are not caused by intrinsic structural and energetic disorder in the OSC. This is an important result because it confirms that the OSC itself can have a good shelf-life in the absence of bias stress, and thus can yield stable devices provided the device degradation mechanisms are clearly identified and eliminated.

DFT calculations to predict defect formation

The questions that arise are the following: (1) What is the nature of the environmental species and the process by which they cause electronic traps that lead to device degradation under operation? (2) How can this process be inhibited through device design in order to achieve stable devices? Before answering these questions, it is informative to review the studies on operational instabilities. Chemical reactions between the OSC and chemical species present in ambient air can generate trap states and the effect is more severe in the presence of bias stress40,41. Tsetseris et al. investigated the interaction of O2 and H2O with pentacene crystals using first-principle calculations and found that O2 dissociation and formation of oxygen complexes generate bandgap states at 0.33–0.40 eV above the valence band edge, while H2O remains intact between molecular layers in the crystal42. Lang et al. experimentally detected bias-induced hole trap states at 0.38 eV using space charge limited current measurements43. Knipp and Northrup reported on gap states in pentacene at 0.29 eV as a result of an electrochemical process facilitated by the presence of O2 and the applied field40. In the presence of water, several mechanisms for electrical instabilities have been postulated. For example, polaron formation in the outermost layer due to the polarization of surrounding water molecules results in the stabilization of holes leading to the creation of polaron traps states44. In OFETs with SiO2 dielectric, charge trapping due to absorbed water increases the severity of the bias stress degradation, and surface passivation with self-assembled monolayers has been adopted to reduce this effect20,37,45. In the case of the donor–acceptor copolymer indacenodithiophene-co-benzothiadiazole (IDT-BT), the interaction of water molecules with the polymer backbone broadens the distribution of torsion angle of the bond between the IDT and BT sub units and increases the energetic disorder by over 200 meV, creating shallow trap states for holes24. Weitz and coworkers showed that the self-ionization of liquid water under bias stress creates a dominant trap that causes threshold shifts in OFETs based on diketopyrrolopyrrole46. Another mechanism for threshold voltage instabilities in the presence of water is proton migration47.

While we do not rule out the above-proposed mechanisms, we evaluated three chemical defects that are hypothesized as being the most probable to form and hence may be responsible for the trap states in the TnHS BDT trimer, as shown in Fig. 3a. The radical formed by oxygen substitution is denoted as OH, and those with hydrogen/hydroxyl addition are represented by Hi and OHi, respectively, and the neutral molecule is also shown as reference. Molecular DFT calculations indicate that both Hi and OHi defect structures have lower (adiabatic) ionization energies with respect to TnHS BDT trimer (see table in Fig. 3b), while a significant positive ionization potential shift (~ 0.71 eV) is found for the OH defect structure, which makes it less likely to be responsible for trap states above the valence band23. To evaluate the relative thermodynamic stabilities of these defects, their formation energies (\({E}^{{\rm{f}}}\)) were calculated as a function of oxygen, hydrogen, and water partial pressures; the results are shown in Fig. 3c. We note that we spanned a wide range of partial pressures necessary due to the difficulty in providing reliable estimates for gas compositions in organic solids, especially considering the relatively large “empty” space in TnHS BDT trimer crystal (~71.6% space fill based on van der Waals molecular volume). Further, to avoid the assumption of thermodynamic equilibrium in organic solids between hydrogen, oxygen, and water, the normalization scheme for the chemical potential calculation from Herrmann et al. was adopted48. The formation energy of the OH defect, \({E}^{{\rm{f}}}\left({\mathrm{{O}}}_{{\mathrm{H}}}\right)\), remains negative for all (\({P}_{{{\rm{O}}}_{2}},{P}_{{{\rm{H}}}_{2}},{P}_{{{\rm{H}}}_{2}{\rm{O}}}\)) considered, corroborating the argument that OH defects are not responsible for the traps observed, otherwise the peak in DOS spectra would have appeared even in the absence of bias stress. In general, for neutral defects, the formation energies follow \({E}^{{\rm{f}}}\left({{\rm{O}}}_{{\rm{H}}}\right) < {E}^{{\rm{f}}}\left({{\rm{H}}}_{{\rm{i}}}\right) < {E}^{{\rm{f}}}\left({{{\rm{OH}}}}_{{\rm{i}}}\right)\). \({E}^{f}\) is linearly dependent on \({{\log }}\left(P\right)\) (Supplementary Fig. 8, SI), which indicates that \({E}^{f}\) for Hi and OHi defects can be raised simultaneously by lowering the water composition of the environment. The thermodynamic (\(0/+\)) transition level is calculated to be 0.341 eV and 0.136 eV above the valence band edge for the charged Hi and OHi defects, respectively (Supplementary Fig. 9a), which suggests Hi defects are more likely to be responsible for the observed hole traps. The (\(0/-\)) transition levels reside at 0.94 eV and 0.72 eV above the valence band edge for Hi and OHi, respectively. Such levels are too deep in the bandgap to act as effective donors.

a Chemical structures of the neutral molecule and potential chemical defects via addition reactions of the TnHS BDT trimer. b Ionization energies of the TnHS BDT trimer and the respective chemical defect structures, c Chemical defect formation energy (in eV) as a function of \({P}_{{{\rm{O}}}_{2}},{P}_{{{\rm{H}}}_{2}},{P}_{{{\rm{H}}}_{2}{\rm{O}}}\) in Pa for, from top to bottom, OH, Hi, and OHi.

Encapsulant selection for trap elimination

Having identified the nature and microscopic origins of the trap states pertaining to device degradation, we used the insights gained from this study to implement a strategy to enhance the operational stability of the device. Since moisture generated the electronic traps and is thus, the culprit for device degradation, but oxygen is needed to enhance the performance through doping, a device encapsulation strategy that shields water molecules from diffusing into the OSC, but is permeable to oxygen, is necessary. One compound that facilitates these requirements is the polymer poly-para-xylene, known as parylene (molecular structure in Fig. 4a)49. Parylene can form conformal, pinhole-free coatings and can be deposited by vapor deposition onto surfaces maintained at room temperature, and thus, it is not restricted in terms of the nature of the OSC or substrate. Several types of parylene derivatives exist; the table in Fig. 4a summarizes the permeability to O2 as well as the water vapor transmission rate (WVTR) of parylene N and parylene C. Following the insights gained from our DOS and DFT analyses, we chose parylene N as an encapsulant layer for our device because of its higher permeability to O2 gas (Fig. 4b). The DOS spectra of the encapsulated devices showed no evidence of a peak during the entire 500 min of operation, and the curves coincide remarkably well, confirming the fact that no change in the trap states occurs (Fig. 4c). The stability of the device can also be witnessed in the transfer characteristics acquired during prolonged transistor operation (Fig. 4d). The time evolution of the threshold voltage shift shown in Fig. 4e depicts a shift of less than 1 V (\({\triangle V}_{{\rm{th}}} \sim 0.9\) V), a value significantly lower than that measured in an unencapsulated device (\({\triangle V}_{{\rm{th}}} \sim 8.0\) V), or when the less efficient encapsulant parylene C was used (\({\triangle V}_{{\rm{th}}} \sim 2.5\) V) (see Supplementary Fig. 10). The other device parameters were very stable as well, with a constant mobility and subthreshold slope being recorded during 500 min of continuous operation in ambient conditions for the OFETs encapsulated in parylene N (see Fig. 4f). Supplementary Fig. 11 shows the hysteresis in the current–voltage characteristics of an encapsulated device in comparison to an unencapsulated device, with the former exhibiting negligible hysteresis in both the transfer and output characteristics.

a Molecular structure of parylene N (top) and barrier properties of different types of parylene (bottom)49. b Schematic of a device encapsulated with parylene N, which selectively allows some O2 molecules to pass through, while effectively preventing the permeation of H2O molecules. c Trap DOS spectrum of an encapsulated device evaluated at various times during repeated operation in ambient air. d Time evolution of the magnitude of threshold voltage shifts |ΔVth| of an encapsulated device (solid circles) in comparison to an unencapsulated device (open circles). e Time evolution of the mobility μ normalized to the value at t = 0 min (red), and subthreshold slope S (blue), of an encapsulated device (solid circles) in comparison to an unencapsulated device (open circles). f Time evolution of the saturation regime transfer characteristics (ID vs VGS at VDS = −60 V) during repeated transistor operation. The left and right axes show the square root and the logarithm of ID, respectively.

Bias stress measurements on optimized devices

The stability studies reported thus far were performed via repeated transfer scans, with the main objective of elucidating the causes and mechanism of device degradation. Many applications based on OFETs, however, require constant biasing, with the details depending on the specific circuit that they serve. For example, active matrix OLED displays are current-driven and require the application of a constant current stress1,24. On the other hand, voltage-driven display technologies such as liquid crystal or electrophoretic displays require the devices to operate in a pulsed mode with bias voltages applied alternatingly between ON and OFF states1,31. To assess the reliability of our devices in an application-specific setting, we further performed operational stability tests by replicating the biasing conditions in voltage-driven display technologies. Figure 5a shows the output characteristics of a device encapsulated in Parylene N prior to electrical stressing. A continuous drain bias and a dynamic gate bias pulsed at 10 s interval was applied for a period of 500 min under high bias conditions in the saturation regime (VGS = VDS = −35 V). The transfer characteristics confirm the excellent operational stability of the device under these biasing conditions, with a threshold voltage shift of ΔVth = −0.2 V and a decrease in the mobility of less than 6%, while the other parameters remain unchanged (Fig. 5b). The transfer characteristics of a device encapsulated with parylene C and stressed under identical bias conditions are displayed in Supplementary Fig. 12a in SI. The threshold voltage stability of this device (i.e., ΔVth = −1.3 V) is superior to an unencapsulated device (Supplementary Fig. 12b, ΔVth = +4.9 V) but is greatly inferior to the device encapsulated with paralyne N (Fig. 5b, ΔVth = −0.2 V) due to the lower O2 permeability characteristic to parylene C compared to parylene N (see Table in Fig. 4a). Since we found that traces of O2 are necessary for TnHS BDT to operate efficiently, these results highlight the importance of a holistic choice of encapsulant for achieving stable devices.

a Output characteristics of a small molecule OSC device at various fixed gate-voltages. The molecular structure of the molecule, namely TnHS BDT trimer, is also included. b Transfer characteristics of the same device acquired at VDS = −35 V prior to stressing (black) and after 500 min of stressing (red) under the application of a continuous drain voltage and a dynamic gate bias pulsed at 10 s interval at VDS = VGS = −35 V. c Output characteristics of a polymer device at various fixed gate-voltage. The molecular structure of the polymer, namely IDT-BT, is also included. d Transfer characteristics of the same IDT-BT device acquired at VDS = −35 V prior to stressing (black) and after 500 min of stressing (red) under the application of a continuous drain voltage and a dynamic gate bias pulsed at 10 s interval at VDS = VGS = −35 V.

Expanding the method to polymer OFETs

We further explored the universality of our strategy by expanding our study to polymer semiconductor OFETs. We focused on IDT-BT, which, in the presence of environmental species behaves similarly to the TnHS BDT trimer24. IDT-BT OFETs are typically fabricated in the bottom-contact, top-gate architecture with Cytop dielectric (Supplementary Fig. 13a, SI)24,50, which is also the geometry adopted here. While Cytop makes a good interface with IDT-BT copolymer in OFETs, yielding charge carriers mobilities in excess of 1 cm2 V−1 s−1 50,51, its encapsulation properties are inferior to that of parylene52, making the devices susceptible to environmental contaminants and thereby unstable24. In order to maintain the good performance facilitated by the Cytop dielectric and simultaneously prevent degradation, we fabricated devices with a double layer dielectric consisting of a thin film of parylene evaporated over Cytop (Supplementary Fig. 13b). The output characteristics are shown in Fig. 5c. The device stressed for 500 min in ambient air under VGS = VDS = −35 V shows very little change in the transfer characteristics (Fig. 5d); the mobility and subthreshold slope remained constant at 2.2 cm2 V−1 s−1 and 1.2 V dec−1, respectively, and an exceptionally small shift is recorded in the threshold voltage (ΔVth = +0.1 V). In addition, this device shows very low hysteresis in both transfer and output characteristics (Supplementary Fig. 14 in SI). The threshold voltage under repeated measurements was also stable, with shifts remaining below 0.1 V (Fig. 6a), as opposed to the Cytop-only devices, where shifts as large as −40 V were recorded. The subthreshold slope and mobility also remained constant upon repetitive measurements, at ~4.0 cm2 V−1 s−1 and ~1 V dec−1, respectively (Supplementary Fig. 15a, SI), with the mobility values being independent of the applied gate-voltage (Supplementary Fig. 15b). In devices with only Cytop as dielectric/encapsulant, the trap DOS spectra indicate that discrete bandgap states are gradually being generated, as confirmed by the overall increase in DOS and the formation of a peak at ca. 0.28 eV from the valence band edge during operation (Fig. 6b). On the other hand, the use of Cytop/Parylene N bilayer dielectric/encapsulant yield devices with a lower trap density that remains constant under operation and hence exhibit remarkable operational stability (Fig. 6c).

a Time evolution of the shift in threshold voltage of a Cytop-only device (open circles) compared to the bilayer Cytop/parylene dielectric device (solid circles). b Trap DOS spectra of a Cytop-only device evaluated at different times during transistor operation shows the generation of discrete bandgap states at ca. 0.28 eV after 10 min of transistor operation. c Trap DOS spectra of a bilayer dielectric device evaluated at different times during transistor operation indicates no change in the DOS.

Discussion

By monitoring the trap DOS in real time and with guidance from DFT calculations, we have identified the processes causing OFET environmental and operational device degradation. These insights allowed us to rationally design solutions for eliminating/reducing the degradation and consistently achieve stable OFETs regardless of the device structure and the nature of the OSC. Device encapsulation layers were selectively chosen for each system to provide a barrier for the most probable and detrimental source of electronic traps, which completely suppressed the formation of trap states in the OSC bandgap, and yielded stable devices with near-ideal current–voltage characteristics, constant mobilities and unprecedented threshold voltage shifts of less than 0.1 V achieved under the application of high bias stress for 500 min in ambient air. This study provides unparalleled insights into the physical processes taking place during prolonged device operation and the results are consistent for both small molecule and polymeric solution-processed OSCs incorporated in devices with a top or bottom-gate geometry. Our results demonstrate a pathway to overcome one of the grand challenges in organic electronics and enable the establishment of practical guidelines for the design of materials and device architectures that yield stable, high-performance OFETs.

Methods

Sample and device fabrication

Bottom-gate, bottom-contact OFETs were fabricated on a heavily doped n-type Si wafer with a 200 nm layer of thermally grown SiO2 serving as the gate and the gate dielectric, respectively. A 3 nm adhesion layer of Ti followed by 40 nm of Au were then deposited via e-beam and thermal evaporation, respectively, through a shadow mask to define the source and the drain electrodes. Prior to depositing the OSC layer, the substrates with predefined contacts were cleaned thoroughly by immersing in a hot acetone bath followed by a hot isopropanol bath, both maintained at 85 °C for 10 min, and then subjected to a UV-ozone treatment for 10 min. The substrates were rinsed with deionized water and dried under N2 gas to remove any remaining residue after the UV-ozone treatment. A self-assembled monolayer, pentafluorobenzenethiol (PFBT, Millipore Sigma) was applied to the contacts by immersing the cleaned test pads in a 30 mM solution of PFBT in ethanol for 30 min. After the treatment, the test pads were thoroughly rinsed with ethanol and dried with a stream of N2 gas. TnHS BDT trimer films were spin coated from a 1.5 wt % solution in chlorobenzene at 1000 r.p.m for 80 s. The completed device was placed in a vacuum desiccator for 2 h to remove any residual solvents. Encapsulated TnHS BDT trimer devices were made by evaporating a layer of parylene N or parylene C (~1500 nm) over the device. For top-gate, bottom-contact OFETs, the source and drain contacts were deposited following the same procedures. Then, IDT-BT films were spin coated from a 5 mg/mL solution in chlorobenzene at 2000 r.p.m for 60 s. The resulting films were annealed on a hot plate at 100 °C for 15 min to remove residual solvents. To complete the top-gate devices, a 940 nm layer of Cytop from AGC Inc. (CTL-809-M) was spin coated over the IDT-BT films at 2000 r.p.m. for 60 s. The films were then annealed on a hot plate at 100 °C for 20 min and placed in a vacuum desiccator overnight at room temperature. A 50 nm layer of Au was then thermally evaporated through a shadow mask to form the top gate. The bilayer dielectric devices were fabricated by evaporating a 650 nm layer of parylene N over Cytop prior to the top-gate electrode evaporation.

Parylene N or parylene C evaporation was carried out in a bespoke reactor consisting of an evacuated quartz tube (pressure ~1 mTorr) maintained at three different temperature zones. First, the dimer di-para-xylene (Acros Organics) was heated at 120 °C to sublime into a dimeric gas which passed through a hot furnace maintained at 700 °C. The dimer then dissociated into its gaseous monomers inside the furnace. Finally, the monomeric gases polymerized onto the device placed in the third region of the tube maintained at room temperature forming a uniform conformal coating.

Electrical characterization

OFETs were electrically characterized using an Agilent 4155C Semiconductor Parameter Analyzer. All measurements were performed in dark, at room temperature and in ambient air, except for the measurements under vacuum, which were performed in a vacuum probe station. The charge-carrier mobility was determined from the slope of the √ID vs. VGS plot using the following equation7,

where L and W are the length and width of the transistor channel. The threshold voltage was evaluated by extrapolating the linear fit of √ID vs VGS to ID = 0. Only devices with ideal or near-ideal current–voltage characteristics have been considered in the analysis, which was the majority of our devices.

Stability tests

Operational stability measurements in ambient air were performed in dark and at room temperature. The relative humidity varied from 32 to 35%. Operational stability tests in vacuum were performed by placing the device in a vacuum probe station which was pumped down for 24 h to a pressure of 10−6 Torr prior to acquiring measurements. The tests were performed using two methods. In the first method, the saturation regime transfer characteristics (ID vs. VGS at VDS = −60 V) were recorded repeatedly for a period of 500 min. The gate-source voltage was swept from 20 V to −40/−60 V in incremental steps of −0.5 V. In the second method, a continuous drain bias and a dynamic gate bias pulsed at 10 s interval were applied to the device for a period of 500 min at VGS = VDS = −35 V and the saturation regime transfer characteristics were acquired both before and after the stressing. The tests were performed on over 15 devices of each sample type and the results were consistent.

For the environmental stability tests, the device was stored in a container covered with aluminum foil in order to shield light. The sample was placed in ambient for a period of 40 days and each day the transfer characteristics were acquired in ambient air and in dark.

Trap DOS analysis

The underlying principle behind the extraction of the trap DOS as a function of energy in the bandgap of the OSC is the gate-voltage-dependent energy level bending occurring at the OSC/dielectric interface. This energy level bending induces a gate-voltage-dependent potential difference called the interface potential V0(UGS). The linear regime transfer characteristics were recorded, from which the gate-voltage-dependent channel conductivity was evaluated using,

Here UGS is the gate-source voltage above the flat-band voltage VFB. i.e., UGS = |VGS−VFB|. VFB is assumed to be the turn-on voltage (VON) of the device. The interface potential function V0 (UGS) was then obtained by numerically solving the following equation (see ref. 53. for a complete derivation):

where εi and l are the relative permittivity and the thickness of the dielectric, respectively, εs and d are the relative permittivity and the thickness of the semiconductor, respectively and σ0 is the conductivity at flat band voltage. The function V0 (UGS) was used to determine the total hole density from,

The trap DOS was then obtained by numerically differentiating the total hole density with respect to V0. i.e.,

where E = eV0 is the energy of the trapping state with respect to the Fermi level. The trap DOS was then plotted as a function of energy from the valence band edge, i.e., E−EV = (EV−EF)−(E−EF) The assumption that at maximum UGS, the quasi-Fermi level coincides with the valence band edge allowed the estimation of EV−EF to be 0.64 eV. We note that the above assumption introduces uncertainty in the trap depth. However, since our hypotheses are based not on the absolute DOS but on the changes in the DOS of a device under external stimuli (electrical stress and environmental contaminants), the uncertainty in the trap depth does not impact our conclusions.

The density of traps generated during transistor operation was calculated from the threshold voltage shift using,

where Ci is the areal capacitance of the dielectric (17.3 nF for 200 nm of SiO2) and e is the electronic charge. The volume density of trap states (in units of cm−3) was evaluated using the thickness of the TnHS BDT trimer films (58.6 nm).

The experimental DOS curves were modeled using two exponential functions to describe the distribution of shallow and deep states, respectively, with the addition of a Gaussian distribution to account for the presence of the peak, according to the following equation:

where E1, E2 are the characteristic decay energies, N1, N2 are the amplitudes of the respective exponential distributions, Epeak defines the position of the Gaussian distribution with an amplitude A and standard deviation σ.

Defect formation energy and transition level

The formation energy of a defect D with charge q,\({E}^{{\rm{f}}}\left(D,q\right)\), is defined as:

where \({E}_{{tot}}\left(P\right)\) and \({E}_{{tot}}\left(D,q\right)\) are the total energy of pure TnHS BDT trimer bulk structure and that with defect D, respectively. Total energies were obtained via DFT calculations as implemented in Gaussian 1654, and Vienna Ab-initio Simulation Package55 (Supplementary Discussion 4). \({E}_{{\rm{F}}}\) is the Fermi energy, \({n}_{i}\) is the stoichiometry coefficient of species i in the defect formation reaction, and \({\mu }_{i}\) is its chemical potential. \({E}_{\text{corr}}\) is a correction term due to the finite size effect in charged defect calculations. While this term can be accurately evaluated for localized charged state, in Supplementary Fig. 9a the correction term is set to zero as in the case of TnHS BDT trimer charged defects are not well-localized at an atomic site, and the dielectric tensor is not isotropic. We note that the correction term calculated from a localized charge model should not alter the argument qualitatively, as shown in Supplementary Fig. 9b (see its caption for detailed implementations), where the (\(+/0\)) transition level of Hi is still closer to the experimentally observed trap DOS peak than that of OHi. All thermodynamic quantities are calculated at 298.15 K.

For neutral defects, \({q}=0\), thus, \({E}^{{\rm{f}}}\) is not dependent on \({E}_{{\rm{F}}}\). As the equilibrium between environmental gases cannot be assumed, chemical potentials of oxygen, hydrogen and water enter the \({\Sigma }_{{\rm{i}}}{n}_{{\rm{i}}}{\mu }_{{\rm{i}}}\) term independently, as shown in Eq. 9.

The complication arising from Eq. 9 is there are more environmental species than stoichiometric relations, i.e., there are infinite choices of \(\left({n}_{{{\rm{H}}}_{2}},{n}_{{{\rm{O}}}_{2}},{n}_{{{\rm{H}}}_{2}{\rm{O}}}\right)\) such that the defect formation reaction is balanced, leading to arbitrary dependence on \({{\rm{\mu }}}_{{H}_{2}}\) for \({E}^{{\rm{f}}}\left(D,q\right)\). This problem is solved by using the normalization scheme proposed by Herrmann et al. which adds another constraint such that the species counts in defect formation reaction is orthogonal to that in water formation reaction, yielding unique choice for \(\left({n}_{{{\rm{H}}}_{2}},{n}_{{{\rm{O}}}_{2}},{n}_{{{\rm{H}}}_{2}{\rm{O}}}\right)\)48. For charged defects, \({E}^{{\rm{f}}}\left(D,q\right)\) becomes a function of \({E}_{{\rm{F}}}\), and their relative stability at a certain \({E}_{{\rm{F}}}\) can be evaluated based on the thermodynamic transition level \(\left(q/{q}^{{\prime} }\right)\):

which is the Fermi-level position at which the defect formation energies of charge \(q\) and \({q}^{{\prime} }\) are equal.

Data availability

All data supporting the conclusions in the paper are present in the paper and/or in Supplementary Information. The data sets generated during and/or analyzed during the current study are available from the corresponding author upon reasonable requests.

References

Sirringhaus, H. 25th Anniversary article: Organic field-effect transistors: the path beyond amorphous silicon. Adv. Mater. 26, 1319–1335 (2014).

Klauk, H. Organic thin-film transistors. Chem. Soc. Rev. 39, 2643 (2010).

Cho, J. H. et al. Printable ion-gel gate dielectrics for low-voltage polymer thin-film transistors on plastic. Nat. Mater. 7, 900–906 (2008).

Fratini, S., Nikolka, M., Salleo, A., Schweicher, G. & Sirringhaus, H. Charge transport in high-mobility conjugated polymers and molecular semiconductors. Nat. Mater. 19, 491–502 (2020).

Choi, H. H., Cho, K., Frisbie, C. D., Sirringhaus, H. & Podzorov, V. Critical assessment of charge mobility extraction in FETs. Nat. Mater. 17, 2–7 (2018).

Anthopoulos, T. D., Noh, Y. & Jurchescu, O. D. Emerging thin‐film transistor technologies and applications. Adv. Funct. Mater. 30, 2001678 (2020).

Lamport, Z. A., Haneef, H. F., Anand, S., Waldrip, M. & Jurchescu, O. D. Tutorial: organic field-effect transistors: materials, structure and operation. J. Appl. Phys. 124, 071101 (2018).

Iqbal, H. F., Holland, E. K., Anthony, J. E. & Jurchescu, O. D. Real-time monitoring of trap dynamics reveals the electronic states that limit charge transport in crystalline organic semiconductors. Mater. Horiz. 7, 2390–2398 (2020).

van de Burgt, Y., Melianas, A., Keene, S. T., Malliaras, G. & Salleo, A. Organic electronics for neuromorphic computing. Nat. Electron. 1, 386–397 (2018).

Kaltenbrunner, M. et al. An ultra-lightweight design for imperceptible plastic electronics. Nature 499, 458–463 (2013).

Yokota, T. et al. Ultraflexible organic photonic skin. Sci. Adv. 2, e1501856 (2016).

Wu, X. et al. A potentiometric mechanotransduction mechanism for novel electronic skins. Sci. Adv. 6, eaba1062 (2020).

Ji, X. et al. Smart surgical catheter for C-reactive protein sensing based on an imperceptible organic transistor. Adv. Sci. 5, 1701053 (2018).

Zeidell, A. M. et al. Organic field‐effect transistors as flexible, tissue‐equivalent radiation dosimeters in medical applications. Adv. Sci. 2001522, 2001522 (2020).

Wu, D. et al. Blade coating aligned, high-performance, semiconducting-polymer transistors. Chem. Mater. 30, 1924–1936 (2018).

Niazi, M. R. et al. Solution-printed organic semiconductor blends exhibiting transport properties on par with single crystals. Nat. Commun. 6, 8598 (2015).

Zeidell, A. M. et al. Large‐area uniform polymer transistor arrays on flexible substrates: towards high‐throughput sensor fabrication. Adv. Mater. Technol. 5, 2000390 (2020).

Sirringhaus, H. Reliability of organic field-effect transistors. Adv. Mater. 21, 3859–3873 (2009).

Park, S., Kim, S. H., Choi, H. H., Kang, B. & Cho, K. Recent advances in the bias stress stability of organic transistors. Adv. Funct. Mater. 30, 1904590 (2020).

Bobbert, P. A., Sharma, A., Mathijssen, S. G. J., Kemerink, M. & De Leeuw, D. M. Operational stability of organic field-effect transistors. Adv. Mater. 24, 1146–1158 (2012).

Okamoto, T. et al. Robust, high-performance n-type organic semiconductors. Sci. Adv. 6, eaaz0632 (2020).

Zschieschang, U. et al. Flexible low-voltage organic transistors and circuits based on a high-mobility organic semiconductor with good air stability. Adv. Mater. 22, 982–985 (2010).

Haneef, H. F., Zeidell, A. M. & Jurchescu, O. D. Charge carrier traps in organic semiconductors: a review on the underlying physics and impact on electronic devices. J. Mater. Chem. C. 8, 759–787 (2020).

Nikolka, M. et al. High operational and environmental stability of high-mobility conjugated polymer field-effect transistors through the use of molecular additives. Nat. Mater. 16, 356–362 (2017).

Kotadiya, N. B., Mondal, A., Blom, P. W. M., Andrienko, D. & Wetzelaer, G. A. H. A window to trap-free charge transport in organic semiconducting thin films. Nat. Mater. 18, 1182–1186 (2019).

Kalb, W. L., Mathis, T., Haas, S., Stassen, A. F. & Batlogg, B. Organic small molecule field-effect transistors with CytopTM gate dielectric: Eliminating gate bias stress effects. Appl. Phys. Lett. 90, 2005–2008 (2007).

Barra, M. et al. Very low bias stress in n -type organic single-crystal transistors. Appl. Phys. Lett. 100, 133301 (2012).

Kettner, M. et al. Solution‐processed organic transistors with excellent electrical stability under ambient conditions. Adv. Electron. Mater. 5, 1900295 (2019).

Kwon, J. et al. Three-dimensional, inkjet-printed organic transistors and integrated circuits with 100% Yield, high uniformity, and long-term stability. ACS Nano 10, 10324–10330 (2016).

Abe, M., Mori, T., Osaka, I., Sugimoto, K. & Takimiya, K. Thermally, operationally, and environmentally stable organic thin-film transistors based on bis[1]benzothieno[2,3-d:2′,3′-d′]naphtho[2,3-b:6,7-b′]dithiophene derivatives: effective synthesis, electronic structures, and structure–property relations. Chem. Mater. 27, 5049–5057 (2015).

Jia, X., Fuentes-Hernandez, C., Wang, C.-Y., Park, Y. & Kippelen, B. Stable organic thin-film transistors. Sci. Adv. 4, eaao1705 (2018).

Nair, S., Kathiresan, M., Mukundan, T. & Natarajan, V. Passivation of organic field effect transistor with photopatterned Parylene to improve environmental stability. Microelectron. Eng. 163, 36–42 (2016).

Park, B., Kim, Y. J., Graham, S. & Reichmanis, E. Change in electronic states in the accumulation layer at interfaces in a poly(3-hexylthiophene) field-effect transistor and the impact of encapsulation. ACS Appl. Mater. Interfaces 3, 3545–3551 (2011).

Petty, A. J. et al. Computationally aided design of a high-performance organic semiconductor: the development of a universal crystal engineering core. Chem. Sci. 10, 10543–10549 (2019).

Sirringhaus, H. et al. High-resolution inkjet printing of all-polymer transistor circuits. Science 290, 2123–2126 (2000).

Sirringhaus, H. et al. Mobility enhancement in conjugated polymer field-effect transistors through chain alignment in a liquid-crystalline phase. Appl. Phys. Lett. 77, 406–408 (2000).

Ng, T. N., Chabinyc, M. L., Street, R. A. & Salleo, A. Bias Stress Effects in Organic Thin Film Transistors. in 2007 IEEE International Reliability Physics Symposium Proceedings. 45th Annual 243–247, https://doi.org/10.1109/RELPHY.2007.369899 (IEEE, 2007).

Salleo, A. & Street, R. A. Light-induced bias stress reversal in polyfluorene thin-film transistors. J. Appl. Phys. 94, 471–479 (2003).

Lu, C.-K. & Meng, H.-F. Hole doping by molecular oxygen in organic semiconductors: band-structure calculations. Phys. Rev. B 75, 235206 (2007).

Knipp, D. & Northrup, J. E. Electric-field-induced gap states in pentacene. Adv. Mater. 21, 2511–2515 (2009).

Northrup, J. E. & Chabinyc, M. L. Gap states in organic semiconductors: hydrogen- and oxygen-induced states in pentacene. Phys. Rev. B 68, 041202 (2003).

Tsetseris, L. & Pantelides, S. T. Intercalation of oxygen and water molecules in pentacene crystals: first-principles calculations. Phys. Rev. B 75, 153202 (2007).

Lang, D. V., Chi, X., Siegrist, T., Sergent, A. M. & Ramirez, A. P. Bias-dependent generation and quenching of defects in pentacene. Phys. Rev. Lett. 93, 5–8 (2004).

Cramer, T. et al. Water-induced polaron formation at the pentacene surface: quantum mechanical molecular mechanics simulations. Phys. Rev. B 79, 155316 (2009).

Häusermann, R. & Batlogg, B. Gate bias stress in pentacene field-effect-transistors: charge trapping in the dielectric or semiconductor. Appl. Phys. Lett. 99, 083303 (2011).

Kettner, M., Zhou, M., Brill, J., Blom, P. W. M. & Weitz, R. T. Complete suppression of bias-induced threshold voltage shift below 273 K in solution-processed high-performance organic transistors. ACS Appl. Mater. Interfaces 10, 35449–35454 (2018).

Sharma, A., Mathijssen, S. G. J., Kemerink, M., de Leeuw, D. M. & Bobbert, P. A. Proton migration mechanism for the instability of organic field-effect transistors. Appl. Phys. Lett. 95, 253305 (2009).

Herrmann, P. & Heimel, G. Structure and stoichiometry prediction of surfaces reacting with multicomponent gases. Adv. Mater. 27, 255–260 (2015).

McKeen, L. W. Permeability Properties of Plastics and Elastomers: 4th edn (Elsevier Science, 2016).

Lamport, Z. A. et al. A simple and robust approach to reducing contact resistance in organic transistors. Nat. Commun. 9, 5130 (2018).

Venkateshvaran, D. et al. Approaching disorder-free transport in high-mobility conjugated polymers. Nature 515, 384–388 (2014).

Wang, L. et al. Enhanced moisture barrier performance for ALD-encapsulated OLEDs by introducing an organic protective layer. J. Mater. Chem. C. 5, 4017–4024 (2017).

Grünewald, M., Thomas, P. & Würtz, D. A simple scheme for evaluating field effect data. Phys. status solidi 100, K139–K143 (1980).

Frisch, M. J. et al. G16_C01. Gaussian 16, Revision C.01, Gaussian, Inc., Wallin (2016).

Kresse, G. & Furthmüller, J. Efficient iterative schemes for ab initio total-energy calculations using a plane-wave basis set. Phys. Rev. B 54, 11169–11186 (1996).

Acknowledgements

The work at Wake Forest University was supported by the National Science Foundation through Grant No. DMR-1627925, while the work at the University of Kentucky was supported through Grant No. DMR-1627428. Computing resources on the Lipscomb High Performance Computing Cluster were provided by the University of Kentucky Information Technology Department and the Center for Computational Sciences (CCS). I.M. acknowledges funding from KAUST Office of Sponsored Research (OSR) under awards no. OSR-2018-CARF/CCF-3079, no. OSR-2015-CRG4-2572 and OSR-4106 CPF2019, as well as EC FP7 Project SC2 (610115), EC H2020 (643791), and EPSRC EP/M005143/1.

Author information

Authors and Affiliations

Contributions

H.F.I. performed device fabrication, characterization, data analysis, and wrote the manuscript along with O.D.J. K.J.T., H.C., I.M., and J.E.A. performed material synthesis. Q.A. and C.R. performed DFT calculations and analysis. All authors reviewed and approved of the final manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Peer review information Nature Communications thanks the anonymous reviewers for their contribution to the peer review of this work.

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Iqbal, H.F., Ai, Q., Thorley, K.J. et al. Suppressing bias stress degradation in high performance solution processed organic transistors operating in air. Nat Commun 12, 2352 (2021). https://doi.org/10.1038/s41467-021-22683-2

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-021-22683-2

- Springer Nature Limited

This article is cited by

-

Stabilizing Schottky junction in conjugated polymer diodes enables long-term reliable radio-frequency energy harvesting on plastic

npj Flexible Electronics (2024)

-

Organic thin-film transistors and related devices in life and health monitoring

Nano Research (2024)

-

Environmentally stable and stretchable polymer electronics enabled by surface-tethered nanostructured molecular-level protection

Nature Nanotechnology (2023)

-

Effect of Temperature on Performance Characteristics with Varying Defect States Parameters in TIPS-pentacene Based OTFTs on n++ Silicon Substrate

Silicon (2023)

-

Performance Evaluation and Analysis of Hybrid Bilayer Dielectrics Based OTFTs for Temperature Sensing Application

Transactions on Electrical and Electronic Materials (2023)