Abstract

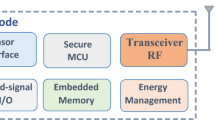

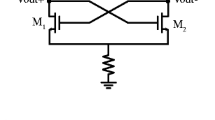

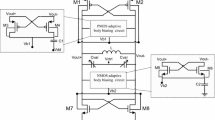

In this paper, a new Design for Testability (DFT) scheme is proposed, for the testing of LC-tank CMOS Voltage Controlled Oscillators (VCOs). The proposed test-circuit is capable of detecting hard (catastrophic) and soft (parametric) faults, injected in the VCO. The test result is provided by a digital Fail/Pass signal. Simulation results reveal the effectiveness of the proposed circuit. The overall silicon area requirement of the proposed DFT scheme is negligible.

Similar content being viewed by others

References

K. Arabi and B. Kaminska, “Oscillation-Test Strategy for Analog and Mixed-Signal Integrated Circuits,” in Proc. of VLSI Test Symposium (VTS), 1996, pp. 476-482.

F. Azais, A. Ivanov, M. Renovell, and Y. Bertrand, “A Methodology and Design for Effective Testing of Voltage-Controlled Oscillators (VCOs),” in Proc. of IEEE 7th Asian Test Symposium (ATS), 1998, pp. 383-387.

J. Craninckx and M. Steyaert, “A Fully Integrated CMOS DCS-1800 Frequency Synthesizer,” in Proc. of IEEE Dig. Tech. Papers, Feb. 1998, pp. 372-373.

L. Dauphinee, M. Copeland, and P. Schvan, “A Balanced 1.5 GHz Voltage Controlled Oscillator with an Integrated LC Resonator,” in Proc. of IEEE Int. Solid-State Circuits Conference (ISSCC), Feb. 1997, pp. 390-391.

L. Dermentzoglou, G. Kamoulakos, and A. Arapoyanni, “A0.35 µm BiCMOS Front End for GSM Low IF Cellular Receiver Applications,” in Proc. of ICECS, Sept. 2001, pp. 1607-1610.

S. Kim, M. Soma, and D. Risbud, “An Effective Defect-Oriented BIST Architecture for High-Speed Phase-Locked Loops,” in Proc. of 18th VLSI Test Symposium (VTS), 2000, pp. 231-236.

I. Rayane, J. Velasco-Medina, and M. Nikolaidis, “A Digital BIST for Operational Amlifiers Embedded in Mixed-Signal Circuits,” in Proc. of VLSI Test Symposium (VTS), 1999, pp. 304-310.

A. Rofougaran, J. Rael, M. Rofougaran, and A. Abidi, “A 900 MHzCMOSLC-oscillator with Quadrature Outputs,” in Proc. of IEEE Int. Solid-State Circuits Conference (ISSCC), Feb. 1996, pp. 392-393.

A. Rusznyak, “Testing of Oscillators,” Journal of Electronic Testing: Theory and Applications, issue 14, pp. 301-304, 1999.

M. Santo-Zarnik, F. Novak, and S. Macek, “Design for Test of Crystal Oscillators: A Case Study,” Journal of Electronic Testing: Theory and Applications, issue 11, pp. 109-117, 1997.

J.J. Tang, K.J. Lee, and B.D. Liu, “A Practical Current Sensing Technique for IDDQ Testing,” IEEE Transactions on VLSI Systems, vol. 3, no. 2, pp. 302-310, 1995.

P. N. Variyam and A. Chatterjee, “Digital-Compatible BIST for Analog Circuits UsingTransient Response Sampling,” IEEE Design & Test of Computers, July-Sept. 2000, pp. 106-115.

D. Vasquez, A. Rueda, and J.L. Huertas, “A New Strategy for Testing Analog Filters,” in Proc. of VLSI Test Symposium (VTS), 1994, pp. 36-41.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Dermentzoglou, L., Tsiatouhas, Y. & Arapoyanni, A. A Design for Testability Scheme for CMOS LC-Tank Voltage Controlled Oscillators. Journal of Electronic Testing 20, 133–142 (2004). https://doi.org/10.1023/B:JETT.0000023677.58861.81

Issue Date:

DOI: https://doi.org/10.1023/B:JETT.0000023677.58861.81