Abstract

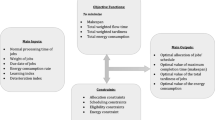

This paper presents a system level approach for the synthesis of hard real-time multitask application specific systems. The algorithm takes into account task precedence constraints among multiple hard real-time tasks and targets a multiprocessor system consisting of a set of heterogeneous off-the-shelf processors. The optimization goal is to select a minimal cost multi-subset of processors while satisfying all the required timing and precedence constraints. There are three design phases: resource allocation, assignment, and scheduling. Since the resource allocation is a search for a minimal cost multi-subset of processors, we adopted an A* search based technique for the first synthesis phase. A variation of the force-directed optimization technique is used to assign a task to an allocated processor. The final scheduling of a hard-real time task is done by the task level scheduler which is based on Earliest Deadline First (EDF) scheduling policy. Our task level scheduler incorporates force-directed scheduling methodology to address the situations where EDF is not optimal. The experimental results on a variety of examples show that the approach is highly effective and efficient.

Similar content being viewed by others

References

J. A. Bannister and K. S. Trivedi. Task allocation in fault-tolerant distributed systems. Acta Informatica 20(3): 261-281, 1983.

E. Barros, W. Rosenstiel, and X. Xiong. A method for partitioning UNITY language in hardware and software. In Proceedings of Euro-DAC '94, pp. 220-225, IEEE Computer Society Press, 1994.

J. Borel. Technologies for multimedia systems on a chip. In 1997 IEEE International Solid-State Circuits Conference, pp. 18-21, 1997.

R. W. Brodersen. The network computer and its future. In 1997 IEEE International Solid-State Circuits Conference, pp. 32-36, 1997.

A. P. Chandrakasan et al. Hyper-LP: A design system for power minimization using architectural transformations. In Proceedings of ICCAD '92, pp. 300-303, Intl. Conf. Computer-Aided Design, Santa Clara, CA, November 1992.

S. Chaudhuri and R. A. Walker. Computing lower bounds on functional units before scheduling. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 4(2): 273-279, June 1996.

R. F. Cmelik and D. Keppel. Shade: A fast instruction-set simulator for execution profiling. Technical Report SMLI93-12, UWCSE 93-06-06, Computer Science and Engineering, University of Washington, 1993.

H. S. Dana. Adding fast interrupts to superscalar processors. Technical Report CSG Memo 366, MIT Laboratory for Computer Science, 545 Technology Square, Cambridge, MA 02139, USA, December 1994.

R. Dechter and J. Pearl. Generalized best-first strategies and the optimality of A*. Journal of the ACM 32(3): 505-536, 1985.

ETSI. European digital cellular telecommunications system (phase 1): Work programme reference: Gsm 06.10, 1992.

D. D. Gajski et al. High-level Synthesis: Introduction to Chip and System Design. Kluwer Academic, Boston, 1992.

D. D. Gajski, S. Narayan, L. Ramachandran, F. Vahid, et al. System design methodologies: Aiming at the 100 h design cycle. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 4(1): 70-82, March 1996.

D. D. Gajski, F. Vahid, and S. Narayan. A system-design methodology: Executable specification refinement. In Proceedings of Euro-DAC '94, pp. 458-463, IEEE Computer Society Press, 1994.

M. R. Garey and D. S. Johnson. Computers and Intractability: A Guide to the Theory of NP-Completeness. W. H. Freeman and Company, New York, NY, 1979.

L. Guerra. Personal communication, June 1997.

L. Guerra, M. Potkonjak, and J. Rabaey. High-level synthesis for reconfigurable datapath structures. In Proceedings of ICCAD '93, Intl. Conf. Computer-Aided Design, Santa Clara, CA, 1993.

R. K. Gupta and G. De Micheli. Hardware-software cosynthesis for digital systems. IEEE Design & Test of Computers 10(3): 29-41, 1993.

C-H. Huang, J-Y. Yen, and M. Ouhyoung. The design of a low cost motion chair for video games and mpeg video playback. IEEE Transactions on Consumer Electronics 42(4): 991-997, 1996.

IEEE. Real-Time Extensions to POSIX. IEEE, New York, NY, 1991.

IEEE. Futurebus+ Recommended Practice. IEEE, New York, NY, 1993.

T. B. Ismail, K. O'Brien, and A. Jerraya. Interactive system-level partitioning with PARTIF. In Proceedings, Euro-DAC '94, pp. 464-468, 1994.

R. Karri and A. Orailoglu. Transformation-based high-level synthesis of fault-tolerant ASICS. In Proc. 29th ACM/IEEE Design Automation Conference, pp. 662-665, 1992.

E. L. Lawler. Optimal sequencing of a single machine subject to precedence constraints. Management Science 19, 1973.

J. P. Lehoczky, L. Sha, and Y. Ding. The rate monotonic scheduling algorithms—exact characterization and average case behavior. In IEEE Real-Time System Symp., pp. 181-191, 1986.

C. L. Liu and J.W. Layland. Scheduling algorithms for multiprogramming in a hard real-time environment. Journal of ACM 20(1): 46-61, 1973.

J. Liu, M. Lajolo, and A. Sangiovanni-Vincentelli. Software timing analysis using HW/SW cosimulation and instruction set simulator. In Proceedings of the Sixth International Workshop on Hardware/Software Codesign (CODES/CASHE '98), pp. 65-69, 1998.

M. C. McFarland, A. C. Parker, and R. Camposano. The high-level synthesis of digital systems. Proceedings of the IEEE 78(2): 301-317, 1990.

R. Nagarajan and C. Vogt. Guaranteed performance of multimedia traffic over the token ring. Technical Report 439210, IBM-ENC, Heidelberg, Germany, 1992.

V. Nirkhe and W. Pugh. Partial evaluation of high-level imperative programming languages, with applications in hard real-time systems. In Conference Record of the Nineteenth Annual ACM SIGPLAN-SIGACT Symposium on Principles of Programming Languages, pp. 269-280, 1992.

D. A. Patterson and J. L. Hennessy. Computer Architecture: A Quantitative Approach. Morgan Kaufmann Publishers, San Mateo, CA, 1990.

P. G. Paulin and J. P. Knight. Force-directed scheduling for the behavioral synthesis of ASICS. IEEE Transactions on CAD 8(6): 661-679, June 1989.

M. Potkonjak and J. Rabaey. Maximally fast and arbitrarily fast implementation of linear computations. In Proc. ICCAD '92, pp. 304-308, IEEE Intl. Conf. Computer-Aided Design, Santa Clara, CA, 1992.

M. Potkonjak and J. Rabaey. Optimizing resource utilization using transformations. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 13(3): 277-292, March 1994.

M. Potkonjak and W. H. Wolf. Cost optimization in ASIC implementation of periodic hard real-time systems using behavioral synthesis techniques. In ICCAD95, pp. 446-451, International Conference on Computer-Aided Design, 1995.

S. Prakash and A. C. Parker. Synthesis of application-specific multiprocessor systems including memory components. Journal of VLSI Signal Processing 8(2): 97-116, October 1994.

J. M. Rabaey and M. Potkonjak. Estimating implementation bounds for real time DSP application specific circuits. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 13(6): 669-683, June 1994.

K. Ramamritham and J. A. Stankovic. Scheduling algorithms and operating system support for real-time systems. Proc. of the IEEE 82(1): 55-67, January 1994.

R. S. Ratner, E. B. Shapiro, H. M. Zeidler, S. E. Wahlstrom, C. B. Clark, and J. Goldberg. Design of a fault tolerant airborne digital computer. In Computational Requirements and Technology, volume 2. SRI Final Report, NASA Contract NASI-10920, 1973.

M. Rim, A. Mujumdar, R. Jain, and R. de Leone. Optimal and heuristic algorithms for solving the binding problem. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 2(2): 211-225, June 1994.

S. Russel and P. Norvig. Artificial Intelligence: A Modern Approach. Prentice-Hall, Englewood Cliffs, NJ, 1995.

B. Schneier. Lecture notes in computer science 809: Fast software encryption. In R. Anderson, editor, CAMBRIDGE SECURITY WORKSHOP, Springer-Verlag, 1994, pp. 191-204.

D. B. Schwartz. ATM scheduling with queuing delay predictions. Computer Communication Review 23(4): 205-211, October 1993.

L. Sha and J. B. Goodenough. Real-time scheduling theory and Ada. IEEE Computer 23(4): 53-62, April 1990.

L. Sha, R. Rajkumar, and J. Lehoczky. Real-time scheduling support in Futurebus+. In IEEE 11th Real-Time Systems Symposium, pp. 331-340, 1990.

L. Sha, R. Rajkumar, and S. S. Sathaye. Generalized rate-monotonic scheduling theory: A framework for developing real-time systems. Proc. of the IEEE 82(1): 68-82, January 1994.

J. Soukup. Circuits layout. Proc. of the IEEE 69(10): 1281-1304, October 1981.

J. A. Stankovic, M. Spuri, M. Di Natale, and G. C. Buttazzo. Implications of classical scheduling results for real-time systems. IEEE Computer 28(6): 16-25, June 1995.

R. Steinmetz. Analyzing the multimedia operating systems. IEEE Multimedia 2(1): 68-84, 1995.

R. A. Walker and R. Camposano. A Survey of High-level Synthesis Systems. Kluwer Academic, Norwell, MA, 1991.

W. H. Wolf. Hardware-software co-design of embedded systems. Proc. of the IEEE 82(7): 967-989, 1994.

H. Yasuda. Multimedia impact on devices in the 21st century. In 1997 IEEE International Solid-State Circuits Conference, pp. 28-31, 1997.

T.-Y. Yen and W. H. Wolf. Communication synthesis for distributed embedded systems. In ICCAD95, pp. 288-294, International Conference on Computer-Aided Design, 1995.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Lee, C., Potkonjak, M. & Wolf, W. Synthesis of Hard Real-Time Application Specific Systems. Design Automation for Embedded Systems 4, 215–242 (1999). https://doi.org/10.1023/A:1008965304567

Issue Date:

DOI: https://doi.org/10.1023/A:1008965304567