Abstract

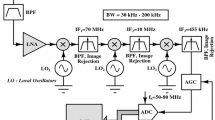

This paper describes an 8-bit 40 MS/s pipeline A/D converter suitable for WCDMA receiver applications. Small power consumption is achieved by using 1.5 bit/stage pipeline architecture and by scaling the capacitor values along the converter. Digital correction allows also to use very low power dynamic comparators. The multiplying D/A converters (MDACs) utilize a modified folded cascode amplifier. The circuit is designed and fabricated in a 0.5 μm CMOS technology. The measured DNL is 0.85 LSB and INL 1.91 LSB. The converter achieves over 48 dBc SFDR and more than 41 dBc SNDR dissipating 61 mW from a 2.7 V supply.

Similar content being viewed by others

References

A. Pä rssinen, J. Jussila, J. Ryynänen, L. Sumanen, and K. Halonen, “A wide-band direct conversion receiver for WCDMA applications,” in ISSCC Digest of Technical Papers, San Francisco, USA, pp. 220–221, 1999.

K. Bult and A. Buchwald, “An embedded 240-mW 10-b 50-MS/s CMOS ADC in 1-mm2.” IEEE J. of Solid-State Circuits SC-32, pp. 1887–1895, 1997.

M. Flynn and B. Sheahan, “A 400M Sample/s 6 b CMOS folding and interpolating ADC,” in ISSCC Digest of Technical Papers, San Francisco, USA, pp. 150–151, 1998.

T. B. Cho and P. R. Gray, “A 10 b, 20 Msample/s, 35mW pipeline A/D converter.” IEEE J. Solid-State Circuits SC-30, pp. 166–172, 1995.

K. Nakamura, M. Hotta, L. R. Carley, and D. J. Allstot, “An 85mW, 10 b, 40 Msample/s CMOS parallel-pipelined ADC.” IEEE J. Solid-State Circuits SC-30, pp. 173–183, 1995.

G. S. Èstrem, È. Moldsvor, and O. Aaserud, “A compact 3V, 70mW, 12-bit video speed CMOS ADC.” Analog Integrated Circuits and Signal Processing 15, pp. 27–36, 1998.

W. Bright, “8 b 75M Sample/s 70mW parallel pipelined ADC incorporating double sampling,” in ISSCC Digest of Technical Papers, San Francisco, USA, pp. 146–147, 1998.

A. Abo and P. Gray, “A 1.5V, 10-bit, 14 MS/s CMOS pipeline analog-to-digital converter,” in Proceedings of 1998 Symposium on VLSI Circuits, Honolulu, 1998.

S. H. Lewis and P. R. Gray, “A pipelined 5-M sample/s 9-bit analog-to-digital converter.” IEEE J. of Solid-State Circuits SC-22, pp. 954–961, 1998.

B. E. Peetz, “Dynamic testing of waveform recorders.” IEEE T. Instrumentation and Measurement IM-32, pp. 12–17, 1983.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Sumanen, L., Waltari, M. & Halonen, K. An 8-bit 40 MS/s Pipeline A/D Converter for WCDMA Testbed. Analog Integrated Circuits and Signal Processing 22, 41–49 (2000). https://doi.org/10.1023/A:1008320026490

Issue Date:

DOI: https://doi.org/10.1023/A:1008320026490