Abstract

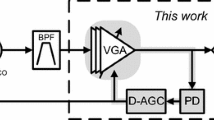

This paper presents the design and implementation of a pipeline Analog-to-Digital Converter (ADC) for superheterodyne receiver application. Several enhancement techniques have been applied in implementing the ADC, in order to relax the target specifications of its building blocks. The concepts of time interleaving and double sampling have been used simultaneously to enhance the sampling speed and to reduce the number of amplifiers used in the ADC. Removal of a front end sample-and-hold amplifier is possible by employing dynamic comparators with switched capacitor based comparison of input signal and reference voltage. Each module of the ADC comprises two 2.5-bit stages followed by two 1.5-bit stages and a 3-bit flash stage. Four such pipeline ADC modules are time interleaved using two pairs of non-overlapping clock signals. These two pairs of clock signals are in phase quadrature with each other. Hence the term quadrature parallel pipeline ADC has been used. These configurations ensure that the entire ADC contains only eight operational-trans-conductance amplifiers. The ADC is implemented in a 0.18-μm CMOS process and supply voltage of 1.8 V. The proto-type is tested at sampling frequencies of 50 and 75 MSPS producing an Effective Number of Bits (ENOB) of 6.86- and 6.11-bits respectively. At peak sampling speed, the core ADC consumes only 65 mW of power.

Similar content being viewed by others

References

W. Kester (ed.), The Data Conversion Handbook, (Analog Devices Inc, Newnes, 2005)

M.Waltari, in Circuit Techniques for Low-Voltage and High-Speed A/D Converters, Dissertation of Doctor of Science, Helsinki University of Technology (2002)

L. Sumanen, M. Waltari, K. Halonen, A 10-bit 200 MS/s CMOS parallel pipeline A/D converter. IEEE J. Solid State Circuits 36, 10481055 (2001)

S.M. Kang, Y. Leblebici, CMOS Digital Integrated Circuits, Analysis and design, 3rd edn. (TATA-McGrawhill, New York, 2003)

K. Nagaraj, H.S. Fetterman, J. Anidjar, S.H. Lewis, R.G. Renninger, A 250-mW, 8-b, 52-Msamples/s parallel-pipelined A/D converter with reduced number of amplifiers. IEEE J. Solid State Circuits 32(3), 312–320 (1997)

B.D. Sahoo, B. Razavi, A 12-Bit 200-MHz CMOS ADC. IEEE J. Solid State Circuits 44(9), 23662380 (2009)

M. Gustavsson, J.J. Wikner, N.N. Tan, CMOS Data Converters for Communications (Kluwer Academic Publishers, Dordrecht, 2000)

R. Gray, P.J. Hurst, S.H. Lewis, R.G. Meyer, in Analysis and Design of Analog Integrated Circuits, 4th Edition (Wiley, 2001)

B. Razavi, Design of Analog CMOS Integrated Circuits (McGrawhill Education, New York, 2000)

D.W. Cline, P.R. Gray, Power Optimized 13-b 5 Msamples/s pipelined analog-to-digital converter in 1.2 μm CMOS. IEEE J. Solid State Circuits 31, 294–303 (1996)

D.-Y. Chang, Design techniques for a pipelined ADC without using a front-end sample-and-hold amplifier. IEEE Trans. Circuits Syst. I 51(11), 2123–2132 (2004)

Q. Yang, X. Wu, Power optimization for pipeline ADC via systematic automation design. Proc. Int. Multiconf. Eng. Comput. Sci. II, 1–6 (2010)

D.G. Haigh, B. Singh, A switching scheme for switched capacitor filters which reduces the effect of parasitic capacitances associated with switch control terminals, in Proceedings IEEE International Symposium on Circuits and Systems (1983), pp. 586–589

S. Nakaigawa, Thermometric-binary code conversion method, conversion circuit there for and encoder element circuits used therefor, US Patent No. US 6346906 B1 (2002)

S.H. Lewis, Optimizing the stage resolution in pipelined, multistage, analog-to-digital converters for video-rate applications. IEEE Trans. Circuits Syst. II 39, 516–523 (1992)

L. Sumanen, M. Waltari, V. Hakkarainen, K. Halonen, CMOS dynamic comparators for pipeline A/D converters. IEEE Int. Symp. Circuits Syst. 5, V (2002)

A. Hastings, Art of Analog Layout (Prentice Hall, Upper Saddle River, 2005)

J. Doernberg, H.-S. Lee, D. Hodges, Speed testing of A/D converters. IEEE J. Solid State Circuits 19(6), 820–827 (1984)

S. Mathur, M. Das, P. Tadeparthy, S. Ray, S. Mukherjee, B.L. Dinakaran, A 115 mW 12 bit 50 MSPS Pipeline ADC, in IEEE International Symposium on Circuits and Systems (2002)

Y.I. Park, S. Karthikeyan, F. Tsay, E. Bartolome, A low power 10 bit, 80 MS/s CMOS pipelined ADC at 1.8 V power supply, in IEEE International Symposium on Circuits and Systems (2001)

J. Park, H.J. Park, J W Kim, S. Seo, P. Chung, A 1 mW 10-bit 500KSPS SAR A/D converter, in IEEE International Symposium on Circuits and Systems (2000)

K. Uyttenhove, M.S.J. Steyaert, A 1.8-V 6-bit 1.3-GHz flash ADC in 0.25 µm CMOS. IEEE J. Solid State Circuits 38(7), 1115 (2003)

S. Paton, A. Di Giandomenico, L. Giandomenico, A. Hernandez, T. Potscher, M. Clara, A 70-mW 300-MHz CMOS continuous-time ΣΔ ADC with 15-MHz bandwidth and 11 bits of resolution. IEEE J. Solid State Circuits 39(7), 1056 (2003)

Acknowledgements

The author would like to acknowledge Advanced VLSI Design Lab, IIT Kharagpur and National Semiconductor Inc., for providing the requisite software and fabrication support.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Roy, S., Banerjee, S. A 9-Bit 50 MSPS Quadrature Parallel Pipeline ADC for Communication Receiver Application. J. Inst. Eng. India Ser. B 99, 221–234 (2018). https://doi.org/10.1007/s40031-018-0315-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40031-018-0315-y