Abstract

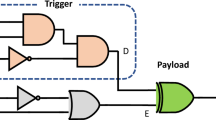

Signature-based techniques are well known for the Built-in Self-test of integrated systems. We propose a novel test architecture which uses a judicious combination of mutual testing and signature testing to achieve low test area overhead, low aliasing probability and low test application time. The proposed architecture is powerful for testing highly concurrent systems in applications such as iterative logic arrays, real-time systems, systolic arrays, and low-latency pipelines which tend to have a large number of functional modules of a similar nature. The use of mutual testing helps in testing “self-loop” modules which cannot be tested using simple signature-based schemes. We provide graph-theoretic optimization algorithms to optimize the test area and test application time of the resulting test architecture.

Similar content being viewed by others

References

M.F. Abdulla, C.P. Ravikumar, and Anshul Kumar, “BIST with Multiple On-Chip Signature Comparisons,” Proc. of IEEE European Test Workshop, Montpellier, France, June 1996, pp. 27–31.

M.F. Abdulla, C.P. Ravikumar, and Anshul Kumar, “Efficient Implementation of Multiple On-Chip Signature Checking,” Proc. of Int. Conference on VLSI Design, India, Jan. 1997.

M. Abromovici, M.A. Breuer, and A.D. Friedman, Digital Systems Testing and Testable Design, Freeman, New York, 1990.

S.-P. Lin, C.A. Njinda, and M.A. Breuer, “Generating a Family of Testable Designs Using the BILBO Methodology,” Journal of Electronic Testing: Theory and Applications, Vol. 4, pp. 71–89, April 1993.

G.L. Craig, C.R. Kime, and K.K. Saluja, “Test Scheduling and Control for VLSI Built-in Self-Test,” IEEE Trans. Comput., Vol. 37, No. 9, pp. 1099–1109, Sept. 1988.

C.H. Chen, “Graph Partitioning for Concurrent Test Scheduling In VLSI Circuit,” Proc. of the 28th ACM/IEEE Design Automation Conference, 1991, pp. 287–290.

C.H. Chen and J.T. Yeun, “Concurrent Test Scheduling In Builtin Self-Test Environment,” Proceeding International Conference on Computer Design (ICCD), 1992, pp. 256–259.

J.H.P. Zurawski and J.B. Gosling, “Design of a High-Speed Square Root Multiply and Divide Unit,” IEEE Trans. on Comput., Vol. C-36, No. 1, pp. 13–23, Jan. 1987.

S. Chiu and C.A. Papachristou, “A Design for Testability Scheme with Applications to Data Path Synthesis,” Proc. of the 28th ACM/IEEE Design Automation Conference, June 1991, pp. 271–277.

L.G. Harris and A. Orailoglu, “Microarchitectural Synthesis of VLSI Designs with High Test Concurrency,” Proc. of the 31st ACM/IEEE Design Automation Conference, 1994, pp. 206–211.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Abdulla, M., Ravikumar, C. & Kumar, A. Optimization of Mutual and Signature Testing Schemes for Highly Concurrent Systems. Journal of Electronic Testing 12, 199–216 (1998). https://doi.org/10.1023/A:1008272532719

Issue Date:

DOI: https://doi.org/10.1023/A:1008272532719