Abstract

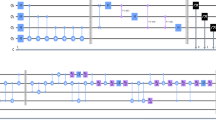

This paper explores the design of efficient test sets and test-pattern generators for on-line BIST. The target applications are high-performance, scalable datapath circuits for which fast and complete fault coverage is required. Because of the presence of carry-lookahead, most existing BIST methods are unsuitable for these applications. High-level models are used to identify potential test sets for a small version of the circuit to be tested. Then a regular test set is extracted and a test generator TG is designed to meet the following goals: scalability, small test set size, full fault coverage, and very low hardware overhead. TG takes the form of a twisted ring counter with a small decoder array. We apply our technique to various datapath circuits including a carry-lookahead adder, an arithmetic-logic unit, and a multiplier-adder.

Similar content being viewed by others

References

B.T. Murray and J.P. Hayes, “Testing ICs: Getting to the Core of the Problem,” IEEE Computer, Vol. 29, pp. 32–45, Nov. 1996.

M.C. Hansen and J.P. Hayes, “High-Level Test Generation Using Physically-Induced Faults,” Proc. VLSI Test Symposium, 1995, pp. 20–28.

D. Gizopoulos, A. Paschalis, and Y. Zorian, “An Effective BIST Scheme for Booth Multipliers,” Proc. International Test Conference, 1995, pp. 824–833.

B. Vasudevan et al., “LFSR-Based Deterministic Hardware for At-Speed BIST,” Proc. VLSI Test Symposium, 1996, pp. 201–207.

B. Nadeau-Dostie, A. Silburt, and V.K. Agarwal, “Serial Interfacing for Embedded Memory Testing,” IEEE Design and Test, Vol. 7, No. 2, pp. 52–63, April 1990.

M. Nicolaidis, “Test Pattern Generators for Arithmetic Units and Arithmetic and Logic Units,” Proc. European Test Conference, 1991, pp. 61–71.

K. Chakrabarty, B.T. Murray, J. Liu, and M. Zhu, “Test Width Compression for Built-in Self Testing,” Proc. International Test Conference, 1997, pp. 328–337.

P.H. Bardell, W.H. McAnney, and J. Savir, Built-In Self-Test for VLSI: Pseudorandom Techniques, Wiley, New York, 1987.

S. Boubezari and B. Kaminska, “A Deterministic Built-In Self-Test Generator Based on Cellular Automata Structures,” IEEE Transactions on Computers, Vol. 44, pp. 805–816, June 1995.

W. Daehn and J. Mucha, “Hardware Test Pattern Generation for Built-In Testing,” IEEE Test Conference, 1981, pp. 110–113.

C. Dufaza and G. Cambon, “LFSR Based Deterministic and Pseudo-Random Test Pattern Generator Structures,” Proc. European Test Conference, 1991, pp. 27–34.

S. Hellebrand et al., “Pattern Generation for Deterministic BIST Scheme,” Proc. International Conference on Computer-Aided Design, 1995, pp. 88–94.

S. Hellebrand, S. Tarnick, and J. Rajski, “Generation of Vector Patterns Through Reseeding of Multiple-Polynomial Linear Feedback Shift Registers,” Proc. International Test Conference, 1992, pp. 120–128.

N.A. Touba and E.J. McCluskey, “Synthesis of Mapped Logic for Generating Pseudorandom Patterns for BIST,” Proc. International Test Conference, 1995, pp. 674–682.

S.B. Akers and W. Jansz, “Test Set Embedding in a Built-In Self-Test Environment,” Proc. International Test Conference, 1989, pp. 257–263.

R. Dandapani, J.H. Patel, and J.A. Abraham, “Design of Test Pattern Generator for Built-In Self-Test,” Proc. International Test Conference, 1984, pp. 315–319.

C.-A. Chen and S.K. Gupta, “A Methodology to Design Efficient BIST Test Pattern Generators,” Proc. International Test Conference, 1995, pp. 814–823.

V.K. Agarwal and E. Cerny, “Store and Generate Built-In Testing Approach,” Proc. International Symposium on Fault-Tolerant Computing, 1981, pp. 35–40.

E.J. McCluskey, Logic Design Principles, Prentice-Hall, Englewood Cliffs, N.J., 1986.

Texas Instruments, The TTL Logic Data Book, Dallas, 1988.

S.B. Akers, “Universal Test Sets for Logic Networks,” IEEE Transactions on Computers, Vol. C-22, pp. 835–839, Sept. 1973.

M. Annaratone, Digital CMOS Circuit Design, Kluwer Academic Publishers, Boston, 1986.

I. Koren, Computer Arithmetic Algorithms, Prentice-Hall, Englewood Cliffs, N.J., 1993.

F. Muradali, V.K. Agarwal, and B. Nadeau-Dostie, “A New Procedure for Weighted Random Built-In Self-Test,” Proc. International Test Conference, 1990, pp. 660–669.

K.K. Saluja, R. Sharma, and C.R. Kime, “A Concurrent Testing Technique for Digital Circuits,” IEEE Transactions on Computer-Aided Design, Vol. 7, pp. 1250–1259, Dec. 1988.

N.R. Saxena and J.P. Robinson, “Accumulator Compression Testing,” IEEE Transactions on Computers, Vol. C-35, pp. 317– 321, April 1986.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Al-Asaad, H., Hayes, J.P. & Murray, B.T. Scalable Test Generators for High-Speed Datapath Circuits. Journal of Electronic Testing 12, 111–125 (1998). https://doi.org/10.1023/A:1008242108853

Issue Date:

DOI: https://doi.org/10.1023/A:1008242108853