Abstract

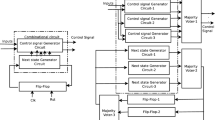

With the rapid development of semiconductor technology and the increasing proliferation of emission sources, digital circuits are frequently used in harsh and hostile electromagnetic environments. Electrostatic Discharge (ESD) interferences are gradually gaining prominence, resulting in performance degradations, malfunctions and disturbances in component and/or system level applications. Conventional solutions to such problems are shielding, filtering and grounding. This paper proposes a novel Evolvable Digital Circuit (EDC) for intrinsic immunity. The key idea is motivated by the noise-robustness and fault-tolerance of the biological system. First, the architecture of the EDC is designed based on the cell structure. Then, ESD immunity tests are carried out on the most fragile element of the EDC in operation. Based on the results, fault models are also presented to simulate different functional disturbances. Finally, the immunity of the EDC is evaluated while it is exposed to a variety of simulated environments. The results which demonstrate a graceful immunity to ESD interference are presented.

Similar content being viewed by others

References

Koo J, G, Pommerenke D. Finding the root cause of an ESD upset event. Proceedings of the 2006 DesignCon, Santa Clara, USA, 2006, 12–36.

Sarbishaei H. Eletrostatic Discharge Protection Circuits for High-Speed Mixed-Signal Circuits, Waterloo University Press, Toronto, Canada, 2007.

Koo J. System and IC Level Analysis of Electrostatic Discharge (ESD) and Eletrical Fast Transient Immunity and Associated Coupling Mechanisms, Missouri-Rolla University Press, Rolla, USA, 2008.

Hartmann M, Haddow P. Evolution of fault-tolerant and noise-robust digital designs. IEE Proceedings Computers & Digital Techniques, 2004, 151, 287–294.

Haddow P C, Typrell A M. Challenges of evolvable hardware: Past, present and the path to a promising future. Genetic Programming and Evolvable Machines, 2011, 12, 183–215.

Greenwood G W. Is it time to stop evolving digital systems? Proceedings of 2009 IEEE Workshop on Evolvable and Adaptive Hardware, Nashville, USA,, 54–58.

Raman K, Wagner A. The evolvability of programmable hardware. Journal of the Royal Society Interface, 2011,, 269–281.

Stoica A, Keymeulen D, Arslan T, Duong V, Zebulum R, Ferguson I. Circuit self-recovery experiments in extreme environments. Proceedings of 2004 NASA/DOD Conference on Evolvable Hardware, Seattle, USA, 2004, 142–145.

Greensted A, Tyrrell A. RISA: A hardware platform for evolutionary design. Proceedings of 2007 IEEE Workshop on Evolvable and Adaptive Hardware, Honolulu, USA, 2007, 1–7.

Sekanina L, Ruzicka R, Vasicek Z, Prokop R, Fujcik L. Repomo32 - New reconfigurable polymorphic integrated circuit for adaptive hardware. Proceedings of 2009 IEEE Workshop on Evolvable and Adaptive Hardware, Nashville, USA, 2009, 39–46.

Xu J, Dou Y, Lv Q, Zhang J. eTissue: A bio-inspired match-based reconfigurable hardware architecture supporting hierarchical self-healing and self-evolution. Proceedings of 2011 NASA/ESA Conference on Adaptive Hardware Systems, San Diego, USA, 2011, 311–318.

Boesen M, Madsen J. eDNA: A bio-inspired reconfigurable hardware cell architecture supporting self-organization and self-healing. Proceedings of 2009 NASA/ESA Conference on Adaptive Hardware Systems, San Francisco, USA, 2009, 147–154.

Miller J. Cartesian Genetic Programming, Springer-Verlag Press, Berlin, Germany, 2011.

Wang J, Lee C. Evolutionary design of combinational logic circuits using VRA processor. IEICE Electronics Express, 2009, 6, 141–147.

Gajda Z, Sekanina L. Gate-level optimization of polymorphic circuits using Cartesian genetic programming. Proceedings of 2009 IEEE Congress on Evolutionary Computation, Trondheim, Norway, 2009, 1599–1604.

Sekanina L, Friedl S. An evolvable combinational unit for FPGAs. Computing and Informatics, 2004, 23, 461–486.

Wagner A. Niutralism and selectionism: A network-based reconciliation. Nature Reviews Genetics, 2008, 9, 965–974.

Vassilev V K, Miller J F. The advantages of landscape neutrality in digital circuit evolution. Proceedings of 3rd International Conference Evolvable Systems: From Biology to Hardware, Scotland, UK, 2000, 252–263.

MIL-STD-883. Department of Defense Test Methods Standard: Microcircuits, Defense Supply Center Columbus, Columbus, OH, USA, 2004.

Electromagnetic Compatibility (EMC). Testing And Measurement Techniques. Electrostatic Discharge Immunity Test, IEC International Standard 61000-4-2, 2008.

McCluskey E, Tseng C. Stuck-fault tests vs. actual defects. Proceedings of International Test Conference, Atlantic City, USA, 2000, 336–342.

Yang S. Logic Synthesis and Optimization Benchmarks User Guide Version 3.0, Microelectronics Center of North Carolina, Research Triangle Park, North Carolina, USA, 1991.

Stomeo E, Kalganova T, Lambert C. Analysis of genotype size for an evolvable hardware system. Proceedings of the 5th International Conference on Computational Intelligence, Progue, Czech Republic, 2005, 74–79.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Liu, S., Man, M., Ju, Z. et al. The immunity of evolvable digital circuits to ESD interference. J Bionic Eng 9, 358–366 (2012). https://doi.org/10.1016/S1672-6529(11)60124-8

Published:

Issue Date:

DOI: https://doi.org/10.1016/S1672-6529(11)60124-8