Abstract

This paper proposes a nine-level switched-capacitor step-up inverter (9LSUI) which can achieve a quadruple voltage gain with single dc source. Differing from other switched-capacitor inverters, the voltage stress of switches is effectively reduced due to the elimination of H-bridge, and the peak inverse voltage of all switches is kept within 2Vdc. In addition, the proposed inverter is able to integrate inductive load, and the capacitor voltage self-balancing can be achieved without any auxiliary circuits. Moreover, the topology structure can be flexibly extended to raise the output levels, and the peak inverse voltage of switches can remain constant with the increase of sub-modules in the extended structure. Comprehensive comparisons are performed to verify the outstanding advantages of the proposed inverter. Finally, the steady-state and dynamic performance of the proposed inverter is validated through an experimental prototype, and the experimental results are provided to prove the theoretical analysis.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Nowadays, multilevel inverters (MLIs) have been widely applied in many areas, such as electric vehicles (EVs), flexible ac transmission systems and motor drives [1,2,3]. Comparing with the conventional two-level inverter, MLIs work better in: reducing the dv/dt on switches; improving output power quality; reducing electromagnetic interference; requiring smaller filters [4].

In general, traditional MLIs are classified into three categories: neutral-point-clamped (NPC) [5, 6]; flying capacitor (FC) [7, 8]; cascaded H-bridge (CHB) [9, 10]. NPC and FC inverters can obtain the desired output voltage by using clamping diodes and floating capacitors. However, the challenge of balancing the capacitor voltage complicates the control strategy along with the increase of the output levels. The CHB inverters consist of H-bridge units, which have the advantages of modular, scalable design and simple control. However, these topologies require multiple dc sources and have no voltage gain, which can limit the applications [11].

Furthermore, the dc sources such as photovoltaic panels, fuel cells and batteries of electric vehicles have low voltage [12], and conventional multilevel inverters suffer from the lack of voltage gain and the unbalance of capacitor voltage. In order to overcome these problems, a dc-dc boost converter is inserted into the front end of the inverter [13]. However, the cascade device will raise power losses and reduce the efficiency of the inverter [14]. To improve the boosting capability, the Z-source techniques have been used in MLIs. However, the extra inductors can increase the volume and cost of inverters. Moreover, the number of output levels has been limited [15,16,17].

Another solution is the switched-capacitor multilevel inverters (SCMLIs) which have no requirement for magnetic components such as inductors and transformers. SCMLIs are able to achieve multilevel output and boost voltage through a switched-capacitor circuit. In addition, the capacitor voltage can be self-balanced without any auxiliary circuits. The step-up switched-capacitor inverter proposed in [18] can output five-level voltage with single dc source. The other single input SC inverter proposed in [19] for high-frequency application employs two capacitors to generate nine-level output voltage. However, the maximum output voltage is only twice the input voltage. The nine-level SC inverter proposed in [20] also has a twice voltage gain.

In order to promote the voltage gain, a generalized inverter has been proposed in [21] to obtain a higher output voltage. Similarly, to increase the flexibility of SCMLIs regarding the output levels and voltage gain, two extendable SCMLIs have been proposed in [22] and [23]. The step-up inverter in [22] reduces the number of power switches, but the ability to integrate inductive loads is lost. For the SC inverter proposed in [23], the capacitors can be charged by a binary asymmetrical pattern, which can significantly raise the number of output levels. However, one of the common shortcomings of the above inverters is that the use of a back-end H-bridge increases the total voltage stress of devices.

The high peak inverse voltage (PIV) of switches can limit the applications of inverters. The accumulation of voltage stress can be avoided by cascading multiple SC inverters [24]. However, multiple isolated dc sources and numerous power components are needed. In addition, the SCMLIs proposed in [25] and [26] eliminate the back-end H-bridge to reduce the PIV. However, both inverters employ numerous switches, which is not conducive to simplify the control strategy, and will lead to an increase of power losses. In [27], a nine-level quadruple-boost inverter with an inherent ability to reverse the polarity of the output voltage has been presented. However, there are two switches that need to withstand the peak value of the output voltage. The step-up SC inverter proposed in [28] reduces the total standing voltage (TSV) of switches. However, numerous capacitors will lead to an increase of system volume and weight.

Considering the aforementioned challenges, this paper proposes a nine-level switched-capacitor inverter (9LSUI) with low voltage stress. The eminent characteristics of the proposed 9LSUI are as follows:

-

(1)

Nine-level output voltage can be achieved with only two capacitors and single dc source.

-

(2)

The proposed inverter has a quadruple voltage gain with low voltage stress.

-

(3)

The PIV of each switch is kept within 2Vdc, which can significantly reduce the TSV of inverter.

-

(4)

An extendable structure in which the PIV of all switches can be kept within 3Vdc.

-

(5)

Capacitor voltage can be self-balanced without involving additional controls.

Next section introduces the circuit design and modulation strategy of the proposed inverter. Section 3 presents the comparison between the proposed topology and other inverters. Section 4 demonstrates the steady-state and dynamic experimental results, and conclusion is obtained in Sect. 5.

2 Proposed 9LSUI

2.1 Circuit Design

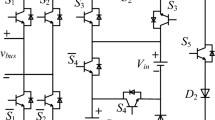

Figure 1 depicts the proposed 9LSUI, in which ten power switches S1 ~ S10 and two capacitors C1 and C2 constitute the SC unit to achieve a multilevel output and voltage boost. Additionally, the complementary switch pairs (SL, \(\overline{S} _{{\text{L}}}\)) and (SR, \(\overline{S} _{{\text{R}}}\)) constitute two half-bridges to reverse the polarity of the output voltage. The proposed inverter employs single dc source which is set as Vdc. All switches are equipped with an anti-parallel diode except for S10. Capacitors C1 and C2 can be charged to Vdc and 2Vdc, respectively. The inverter can output nine levels: 0, ± Vdc, ± 2Vdc, ± 3Vdc, ± 4Vdc. Hence, the proposed topology achieves a quadruple voltage gain.

The proposed inverter has an excellent characteristic of low voltage stress. As shown in Fig. 1, X is the ratio of PIV to Vdc, which can visually indicate the maximum stress of each switch. It can be seen that the PIV of most switches is Vdc, only switches S8 ~ S10, SR and \(\overline{S} _{{\text{R}}}\) withstand the voltage 2Vdc which is half of the peak output voltage. Therefore, it is worth noting that the features of high boosting factor and low voltage stress make the topology fit for medium and high-power applications with low input voltage.

2.2 Operating Principle

The operating principle of switches and capacitors are shown in Table 1. Where “0” and “1” indicate the off and on states of switches, “C”, “D” and “–” denote the charging, discharging and idle states of capacitors.

Detailed nine operating states and current paths of the proposed inverter are demonstrated in Fig. 2, where the blue highlight and purple highlight lines are the charging current paths of capacitors and the reverse current paths. It can be seen that capacitor C1 can be charged to Vdc in parallel with dc source when the output voltages are 0, Vdc and ± 3Vdc. Capacitor C2 can be charged to 2Vdc in parallel with dc source and capacitor C1 when the output voltages are 2Vdc and –Vdc. The connections of the dc source and capacitors can be changed through the ON/OFF states of switches, so as to achieve nine-level output voltage and quadruple voltage gain.

2.3 Modulation Strategy

Various modulation techniques have been applied to multilevel inverters. In this paper, the phase disposition pulse width modulation (PD-PWM) is selected for the proposed 9LSUI due to its simplicity and low total harmonic distortion (THD) [28].

As shown in Fig. 3, eight carrier signals e1 ~ e8 are compared with a sinusoidal reference signal es to generate eight pulse signals u1 ~ u8. The gate drive signals vGS1 ~ vGSR of the switches can be obtained through the logical combination of u1 ~ u8. The logical combination can be expressed as

The modulation index M for the 9LSUI is defined as

where As and Ac are the amplitudes of the reference signal and carrier signals. The range of M is 0 < M ≤ 1. The inverter can output different levels with the change of M between 0 and 1.

3 Capacitance and Power Losses

3.1 Design of Capacitor

The voltage fluctuation range of capacitors should be maintained within an acceptable range to improve voltage quality. The capacitor voltage ripple is related to the maximum continuous discharge of the capacitor. Therefore, the effect of the capacitor voltage ripple on the output voltage can be reduced effectively when the proper value of the capacitance is selected.

It can be seen from Fig. 2 and Table 1, C1 will be in discharging state when output voltages are -Vdc and -2Vdc in the negative half cycle, and C2 will be in discharging state when the proposed 9LSUI outputs -3Vdc and -4Vdc. As shown in Fig. 3, the maximum continuous discharging intervals of C1 and C2 are [t7, t10] and [t9, t12]. In fact, C1 and C2 are in alternate charging and discharging for part of the time in these two intervals, such as C1 in the interval [t7, t8]. The most extreme case that ignores the charging time of capacitors is considered in the following analysis. The time t7, t9, t10 and t12 in Fig. 3 are calculated as follows

where fs is the frequency of the sinusoidal reference wave. Assuming the load is pure resistive. Therefore, the maximum continuous discharging amount ΔQC1 of C1 within [t7, t10] can be calculated as

The maximum continuous discharging amount ΔQC2 of C2 within [t9, t12] is calculated as

where Iload is the amplitude of the load current. Assuming k% is the constant describes the maximum acceptable voltage ripple, the capacitances of C1 and C2 can be determined as

3.2 Calculation of Losses

3.2.1 Switching Losses

The switching losses of MLIs occur during the turn-on and turn-off period of power switches due to the inherent switching delay [23]. It is known that the voltage and current of switches exhibit a linear approximation during the switching period. Therefore, the turn-on losses (Psw,on,i) and the turn-off losses (Psw,off,i) of the i-th involved power switch can be calculated by

where fsw is the switching frequency, vs and is present the voltage and current of switch when the switching state changes, Von,i and Voff,i are the on-state and off-state voltage of the i-th switch, Ion,i and Ioff,i are the on-state and off-state current that across the i-th switch, ton and toff are the time of turn-on and turn-off. Therefore, the total switching losses Psw of the proposed inverter can be obtained as

3.2.2 Conduction Losses

The conduction losses are related to the parasitic resistance of power devices in current paths, including the conduction resistance Ron of switches, the internal resistance RD of anti-parallel diodes and the equivalent series resistance RESR of the capacitors.

The equivalent resistance for each level is listed in Table 2. According to Fig. 3 and Table 2, in the interval [0, t1], the load current flows through three switches and three diodes (four switches and two diodes) when the output voltage is 0 (Vdc). Therefore, the energy loss Eloss1 during the interval [0, t1] can be calculated as

where iload is the load current, Ron is the conduction resistance of switches and RD is the internal resistance of anti-parallel diodes.

Similarly, the conduction losses in other inverters ([t1, t2]-[t13, t14]) are also can be calculated according to Eq. (21). The total conduction losses Pcond as the proposed 9LSUI can be calculated as

where fs is the frequency of the sinusoidal reference wave.

3.2.3 Capacitor Ripple Losses

The ripple loss Prip is caused by the voltage fluctuation of capacitor. The voltage ripple ΔVrip,Ci of the capacitor Ci is obtained by

where iCi(t) is the current across capacitor, the interval [t-, t +] is the discharging period of Ci. For the proposed 9LSUI, [t8, t9] and [t9, t12] are the maximum discharging intervals of C1 and C2. The ripple losses Prip can be calculated as

Therefore, the total losses Ploss of the proposed 9LSUI can be calculated as

Finally, the efficiency of the nine-level inverter can be expressed as

where η and Po are the efficiency and output power of the proposed inverter.

4 Topology Extension and Comparisons

The proposed 9LSUI can be extended with multiple SC units, which can generate more output levels and achieve higher voltage gain. In order to further evaluate the superiority of the proposed topology, a comprehensive analysis and comparison with other recently SCMLIs have been implemented.

4.1 Extended Structure

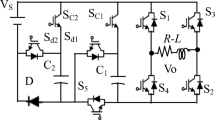

The extended structure of the proposed 9LSUI is shown in Fig. 4. It can be seen that each two SC units are in a back-to-back connection through a power switch pairs Pi1 and Pi2 (i = 1, 2, …, n-1). Notice that these switch pairs have a complementary operation with each other to avoid the short-circuit problem. In the extended topology, n dc sources are used and the voltage is Vdc. Therefore, the number of capacitors (NCap) and switches (NSW) can be expressed as

In this configuration, the voltage of the capacitor Ci1 remains as Vdc and the capacitor Ci2 is charged to 2Vdc. The PIV of Pi1 and Pi2 is kept within 3Vdc in the extended structure. Therefore, the number of output levels (NL), the peak value of the output voltage (Vo, max) and the TSV for the switches can be obtained as:

4.2 Comparison of Nine-level Inverters

In this section, to evaluate the performance of the proposed 9LSUI, a comprehensive comparison with other topologies is made in Table 3. The comparison focuses on the numbers of dc sources (NSource), capacitors (NCapacitor), switches (NSwitches) and diodes (NDiodes). Furthermore, the PIV of semiconductors (switches and diodes), the TSVpu of semiconductors, the voltage gain and the use of H-bridge are also considered. The terms related to TSVpu and voltage gain are defined as

where Vo_max and Vdc are the maximum output peak voltage and the dc input voltage.

According to Table 3, the proposed inverter requires minimum capacitors, which helps to reduce the volume and weight of the inverter. Moreover, compared with other inverters, the proposed topology employs single dc source and two capacitors to achieve quadruple voltage gain, while the boosting factor in [19] and [20] is 2. Although the inverters in [22] and [23] use fewer switches, they all require H-bridge to shift output voltage polarity. Moreover, the large number of diodes used in [22] may limit its capacity of integrating inductive loads.

The PIV of the switches is important role to evaluate the performance of MLIs. The comparison shows that the PIV of the switches is only 2Vdc. Although the inverter in [25] has lower PIV, the use of numerous switches will lead to a high cost. A significant feature of the proposed inverter is low TSVpu, which also credits to the low PIV of switches. The inverter in [28] has the lowest TSV, but the use of four capacitors increases the volume and cost.

The comparison between the suggested extended structure and other inverters is performed at the output levels of (2 m + 1) or m. Table 4 and Fig. 5. show the comparison results, the proposed extended structure employs less components (capacitors, switches and diodes). Moreover, the proposed structure does not need extra diodes and has the minimum TSVpu. In a word, the proposed topology has obvious advantages in promoting voltage gain, reducing the number of components and voltage stress of the switches.

5 Simulation and Experiment Analysis

5.1 Simulation Results

In order to examine the performance of the proposed inverter, a simulation model of nine-level switched-capacitor inverter is established in MATLAB/Simulink. The simulation parameters are shown in Table 5.

The simulation results are shown in Fig. 6. It can be seen that the proposed inverter can output nine-level voltage and achieve a quadruple voltage gain. The capacitor voltages are self-balanced with low voltage ripple.

When the modulation index is 0.9, the Fast Fourier Transform (FFT) of the output voltage is shown in Fig. 7. It can be seen that the THD is 15.18%, and the 40th harmonic component is larger than the others because the carrier frequency is 2 kHz. The low THD can also simplify the design of the filter.

5.2 Experimental Results

To verify the practicability and effectiveness of the proposed 9LSUI, an experimental prototype has been built as shown in Fig. 8. The components and parameters of the model are shown in Table 6. The experiments examine the steady-state performance and dynamic responses of the proposed topology under several different conditions.

Figure 9 shows the steady-state experiment results and efficiency curve. The output voltage and load current are shown in Fig. 9a. It can be seen that the amplitude of output voltage is 120 V, which verifies that the proposed inverter can achieve a voltage gain of 4. Figure 9b presents the output voltage and load current when the inductive load is integrated. The load current appears as a sinusoidal waveform due to low THD. The voltages of C1 and C2 under the R & L load are shown in Fig. 9c. It can be observed that C1 and C2 are charged to 28.66 V and 57.65 V. Moreover, the capacitor voltage fluctuates periodically within 5 V, which verifies the self-balancing ability of the proposed inverter. Figure 9d shows the theoretical efficiency and experimental efficiency of the proposed inverter under different output power. It can be seen that the 9LSUI has a great performance.

Figure 10 shows the voltage stress of different switches. The peak inverse voltages of the switches S1 ~ S7, SL, and \(\overline{S} _{{\text{L}}}\) are Vdc, and the peak inverse voltages of the switches S8 ~ S10, SR, and \(\overline{S} _{{\text{R}}}\) are 2Vdc. Table 7 presents the steady-state experimental results. The experimental results are in good agreement with the previous theoretical analysis, which proves that the proposed inverter has the characteristics of low voltage stress across switches.

Figure 11 and Table 8 present the dynamic experimental results with the change of M. Figure 11a–c show the dynamic responses when the modulation ratio M varies from 0.9 to 0.7, 0.7 to 0.4 and then 0.4 to 0.2. It can be seen that the number of output levels will reduce with the decrease of M. Meanwhile, the amplitude of the load current also decreases accordingly. The waveforms quickly reach new steady-states after these changes, which is in good agreement with the theoretical analysis and design requirements.

Figures 12a, b are the dynamic responses when the dc source varies from 10 to 30 V and from 30 to 10 V. In Fig. 12, the amplitude of the output voltage gradually rises from 40 to 120 V when the input voltage increases. Meanwhile, the voltage of C1 rises from 10 to 30 V, and the voltage of C2 rises from 20 to 60 V. It can be seen from Fig. 12b that the variations of load current and voltage are opposite to the ones in Fig. 12a when the input voltage decreases. Figures 12c, d are the dynamic responses when the load varies from no-load to resistive load (50 Ω), and then to resistive-inductive load (50 Ω-15 mH). The output voltage remains constant, and the load current varies instantaneously with the change of load, and then reaches a new steady-state.

In summary, the experimental results of the proposed 9LSUI validate the previous theoretical analysis. The capacitor voltage self-balancing can be achieved under steady-state and dynamic conditions, which verifies the practicability and effectiveness of proposed inverter.

6 Conclusion

The paper presents a switched-capacitor step-up inverter, which can generate nine output levels and achieve quadruple voltage gain without H-bridge. In addition, the proposed 9LSUI has voltage-self-balance ability without any auxiliary circuits, and the peak inverse voltage of all switches is kept within 2Vdc. Moreover, the extended structure of the proposed inverter can generate more output levels, while the PIV of all switches is kept within 3Vdc. The comparison results with other inverters show that the proposed inverter has the advantages of reducing the components, raise the voltage gain, and lowering the TSV of devices. An experimental prototype is implemented to verify the effectiveness and feasibility of proposed 9LSUI. The experimental results indicate that the proposed topology performs well in different conditions.

References

Axelrod B, Berkovich Y, Ioinovici A (2005) A cascade boost-switched-capacitor-converter - two level inverter with an optimized multilevel output waveform. IEEE Trans Circuits Syst I: Reg Pap 52(12):2763–2770

Salem A, Van Khang H, Robbersmyr KG, Norambuena M, Rodriguez J (2021) Voltage source multilevel inverters with reduced device count: topological review and novel comparative factors. IEEE Trans Power Electron 36(3):2720–2747

Yang T, Mok K, Ho S, Tan S, Lee C, Hui RSY (2019) Use of integrated photovoltaic-electric spring system as a power balancer in power distribution networks. IEEE Trans Power Electron 34(6):5312–5324

Wang Y, Yuan Y, Li G, Ye K, Wang K, Liang J (2020) A T-type switched-capacitor multilevel inverter with low voltage stress and self-balancing. IEEE Trans Circ Syst I: Regular Papers 68(5):2257–2270

Beniwal N, Tafti HD, Farivar GG, Ceballos S, Pou J, Blaabjerg F (2021) A control strategy for dual-input neutral-point-clamped inverter-based grid-connected photovoltaic system. IEEE Trans Power Electron 36(9):9743–9757

Guo F, Yang T, Li C, Bozhko S, Wheeler P (2022) Active modulation strategy for capacitor voltage balancing of three-level neutral-point-clamped converters in high-speed drives. IEEE Trans Ind Electron 69(3):2276–2287

Wang C, Lu Y, Huang M, Martins RP (2021) A two-phase three-level buck converter with cross-connected flying capacitors for inductor current balancing. IEEE Trans Power Electron 36(12):13855–13866

Amini J, Moallem M (2017) A fault-diagnosis and fault-tolerant control scheme for flying capacitor multilevel inverter. IEEE Trans Ind Electron 64(3):1818–1826

Wang Y, Yuan Y, Li G, Chen T, Wang K, Liang J (2020) A generalized multilevel inverter based on T-Type switched capacitor module with reduced devices. Energies 13(17):1–20

Xiao B, Hang L, Mei J, Riley C, Tolbert LM, Ozpineci B (2015) Modular cascaded H-bridge multilevel PV inverter with distributed MPPT for grid-connected applications. IEEE Trans Ind Appl 51(2):1722–1731

Cortes P, Wilson A, Kouro S, Rodriguez J, Rub HA (2010) Model predictive control of multilevel cascaded H-bridge inverters. IEEE Trans Ind Electron 57(8):2691–2699

Jang M, Ciobotaru M, Agelidis VG (2013) A single-phase grid connected fuel cell system based on a boost-inverter. IEEE Trans Power Electron 28(1):279–288

Kerekes T, Sera D, Mathe L (2015) Three-phase photovoltaic systems: structures, topologies, and control. Electr Power Compon Syst 43(12):1364–1375

Ellabban O, Abu-Rub H (2016) Z-source inverter: topology improvements review. IEEE Trans Ind Electron Mag 10(1):6–24

Ahmad A, Singh RK, Beig AR (2019) Switched-capacitor based modified extended high gain switched boost z-source inverters. IEEE Access 7:179918–179928

Ho A, Chun T (2018) Single-phase modified quasi-Z-source cascaded hybrid five-level inverter. IEEE Trans Ind Electron 65(6):5125–5134

Sun D, Ge B, Liang W, Abu-Rub H, Peng FZ (2015) An energy stored quasi-Z-source cascade multilevel inverter-based photovoltaic power generation system. IEEE Trans Ind Electron 62(9):5458–5467

Saeedian M, Hosseini SM, Adabi J (2018) Step-up switched-capacitor module for cascaded MLI topologies. IET Power Electron 11(7):1286–1296

Liu J, Wu J, Zeng J, Guo H (2017) A novel nine-level inverter employing one voltage source and reduced components as high-frequency AC power source. IEEE Trans Power Electron 32(4):2939–2947

Barzegarkhoo R, Moradzadeh M, Zamiri E, Kojabadi HM, Blaabjerg F (2018) A new boost switched-capacitor multilevel converter with reduced circuit devices. IEEE Trans Power Electron 33(8):6738–6754

Hinago Y, Koizumi H (2012) A switched-capacitor inverter using series/parallel conversion with inductive load. IEEE Trans Ind Electron 59(2):878–887

Ye YM, Cheng KWE, Liu JF, Ding K (2014) A step-up switched-capacitor multilevel inverter with self-voltage balancing. IEEE Trans Ind Electron 61(12):6672–6680

Barzegarkhoo R, Kojabadi HM, Zamiry E, Vosoughi N, Chang L (2016) Generalized structure for a single phase switched-capacitor multilevel inverter using a new multiple DC link producer with reduced number of switches. IEEE Trans Power Electron 31(8):5604–5617

Liu J, Cheng KWE, Ye Y (2014) A cascaded multilevel inverter based on switched-capacitor for high-frequency AC power distribution system. IEEE Trans Power Electron 29(8):4219–4230

Taghvaie A, Adabi J, Rezanejad M (2018) A self-balanced step-up multilevel inverter based on switched-capacitor structure. IEEE Trans Power Electron 33(1):199–209

Sandeep N, Ali JSM, Yaragatti UR, Vijayakumar K (2019) A self-balancing five-level boosting inverter with reduced components. IEEE Trans Power Electron 34(7):6020–6024

Liu J, Lin W, Wu J, Zeng J (2019) A novel nine-level quadruple boost inverter with inductive-load ability. IEEE Trans Power Electron 34(5):4014–4018

Saeedian M, Adabi ME, Hosseini SM, Adabi J, Pouresmaeil E (2019) A novel step-up single source multilevel inverter: topology, operating principle, and modulation. IEEE Trans Power Electron 34(4):3269–3282

Alishah RS, Hosseini SH, Babaei E, Sabahi M, Zare A (2016) Extended high step-up structure for multilevel converter. IET Power Electron 9(9):1894–1902

Peng W, Ni Q, Qiu X, Ye Y (2019) Seven-level inverter with self-balanced switched-capacitor and its cascaded extension. IEEE Trans Power Electron 34(12):11889–11896

Liu J, Zhu X, Zeng J (2020) A seven-level inverter with self-balancing and low-voltage stress. IEEE Trans Emerg Sel Topics Power Electron 8(1):685–696

Acknowledgements

This work was supported in part by the National Natural Science Foundation of China under Grant 51507155, in part by the Youth Key Teacher Project of Henan Universities under Grant 2019GGJS011, and in part by the Key R&D and Promotion Special Project of Henan Province under Grant 222102520001.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Wang, Y., Ye, J., Wang, K. et al. A Nine-Level Switched-Capacitor Step-Up Inverter with Low Voltage Stress. J. Electr. Eng. Technol. 18, 1147–1159 (2023). https://doi.org/10.1007/s42835-022-01187-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s42835-022-01187-z