Abstract

The advent of 6G communication promises a transformative leap in wireless connectivity, ushering in an era of unprecedented data rates, ultra-low latency, and pervasive connectivity. To harness the full potential of 6G networks, it is imperative to address the unique challenges posed by evolving communication environments. In this context, we present a novel framework that integrates Adaptive Composite Bandwidth and Automatic Gain Control techniques into the 6G communication paradigm. Optical wireless receivers experience large input current difference due to the large transmitted power, noise from ambient light and the varying efficiencies of different photodiode receivers. With its large dynamic range of μA to mA, transimpedance amplifiers are suitable to handle photodiode efficiency with a large dynamic range. The receiver design proposed in this article incorporates two characteristic parameter adjustments, namely, bandwidth and automatic gain. By adjusting the bandwidth the signal-to-noise ratio of the incoming signal is automatically controlled. By controlling the bandwidth, the unwanted noise is reduced and amplifier output is liable to low noise and enhances the dynamic range without extra filtering. The automatic gain control adapts its gain based on slight change in the input signal at the receiver front-end. This optimization technique ensures low photo-detection and amplification noise to achieve better quality of service. The results indicate that the bootstrap transimpedance amplifier gain is around 53.3 dB and frequency cut-off at 109.7 MHz. Thus, when gain control capacitance is varied between 50 pF to 1 nF, the bandwidth adjustment falls in the range 7.5–104.1 MHz, and the amplifier’s second stage gain becomes 10.4 dB. The overall gain of the proposed configuration with automatic gain control integrated into the transimpedance amplifier increases up to 31.1 dB, while the bandwidth increases from 9.4 to 60.7 MHz. Consequently, the gain bandwidth product is optimized from 10.4 to 31.1 dB. The main contribution of this work is optimizing the product by selecting a capacitance value within the given range that maximizes the gain-bandwidth product. This optimization paradigm is predicated on identifying a capacitance value that minimizes the gain-bandwidth product, thereby effectuating effective noise mitigation. This proposed framework embodies a significant contribution to the domain of 6G communications, heralding a new epoch in the optimization of wireless connectivity through the strategic integration of adaptive bandwidth and automatic gain control mechanism.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

PIN diodes used in optical receivers must have a wide capacitive intrinsic region to be sensitive and efficient enough to detect optical signals [1,2,3]. Unfortunately, a large intrinsic region increases the transit time across the intrinsic region by the majority charge carriers and thus possibly limit the receiver’s high-frequency reponse.

A challenge with typical PIN diode is how to maintain a large capacitive intrinsic region that is acceptable for wireless optical receiver, as illustrated and described with a reasonable solution by Sibley et al. [1,2,3]. The main problem of receiver yield is the requirement to have a wide range of capacitive impedance handling at the same time. To enhance the chance of having these desribale properties, we need to engineer a wide intrinsic region, and the possible outcome of a device using a composite material which produce limitation across the junction due to transit time during the performance at high frequency [4]. A typical PN device operates at 95% efficiency, in the intrinsic region with not more than 1 μm width near the illumination surface [2]. As the signal majority charge takes time to travel through the intrinsic region, delivery to the external circuit experiences a delay which also reduces the high frequency bandwidth response. The p- or n- region that is illuminated depends on the frequency response effectiveness that is governed by a relationship of the approximate form \({\text{sin}}(x/x)\). The consequence is that, to increase the signal bandwidth effectively, we must consider frequency compensation. As shown subsequently, combining automatic gain and bandwidth control produces the signal charge at the very edge of the intrinsic region. From the circuit performance point of view, this approximation is reasonable. Thus, this article proposes a technique that exploits the angle view of both optical communications and video systems that share the same front-end receiver equivalent circuit, as illustrated in Fig. 1 [1].

Equivalent circuit of a photodetector’s front-end excluding noise sources [1]

Referring to Fig. 1, Iph is the photocurrent, Rbulk the represents bulk resistance, Rb is the bias resistance Cd represents capacitance device capacitance, Cs is stray capacitance. The effect of Rbulk is assumed to be small [1]. Therefore, the equivalent circuit reduces to Iph parallel to Rb and (Cs + Cd). In any receiver system design, the widely known problem involves large source impedance and capacitance components, requiring equalization [1, 5,6,7,8,9]. This is associated directly with the characteristic of correcting the triangular frequency response, near the corner frequency. It is clear that when the RC device’s time constant is high, corner frequency becomes low, resulting in heavy increase in noise effect. This is because amplifiers in frontend devices tend to create noise with white spectrum. However, adding equalization to the system the process is affected by three things: large source impedance, receiver capacitance, and white noise resulting from the RC time constant.

The signal response will be corrected, but at the expense of possible change in operating frequency that results in rapid increase in noise root-mean-squared (RMS) voltage or RMS current. The technical analysis demonstrates that integrated noise power above the corner frequency thus tends to have a B bandwidth of the signal channel as a function of bandwidth. This important technical analysis of the detector capacitance shows that the capacitance value must be small, and the smaller it is the better. This is because reducing the load resistance value can also effectively ensure the output signal voltage reduces which is equal to a gain-bandwidth theory of argument. The discussion highlights the difficulty of balancing the capacitive impedance requirements of these diodes while aiming for high performance in wireless optical receivers. Here, I'll attempt to distill the main points and propose a simplified explanation along with a potential solution, as hinted at in your text. Key Challenges highlighteda are:

-

PIN diodes used in optical receivers need a wide intrinsic region to function effectively. This is crucial for achieving desirable sensitivity and efficiency in detecting the optical signal. However, this requirement poses a significant challenge because a wider intrinsic region can lead to increased capacitance, which in turn affects the receiver's ability to handle high-frequency signals.

-

As the signal travels through the intrinsic region of the PIN diode, there's a delay before it reaches the external circuit. This delay can limit the receiver's high-frequency bandwidth response. The crux of the problem lies in the time it takes for the majority charge carriers to traverse the intrinsic region.

-

The need to manage a wide range of capacitive impedance is crucial for receiver yield. This becomes particularly challenging when trying to ensure that the device can operate efficiently across a broad spectrum of frequencies.

In order to solve these, carefully design of PIN diode's intrinsic region, it's possible to maintain the necessary wide area while mitigating some of the adverse effects on high-frequency performance. This might involve optimizing the material properties or the physical dimensions of the intrinsic region. These materials could potentially reduce the intrinsic region's capacitance without compromising its size, thereby enhancing the diode's high-frequency response. A critical part of the solution involves circuit design strategies, such as the implementation of automatic gain and bandwidth control. This approach can help manage the signal delay and frequency response issues by adjusting the circuit's properties in real-time, based on the characteristics of the incoming signal. To counteract the effects of large source impedance and capacitance, as well as the increase in noise associated with high RC time constants, this suggests incorporating equalization into the system. This would help correct the signal response, ensuring that the receiver can operate efficiently across a broader frequency range while minimizing noise.

2 Literature review and background

The literature review and background provided point towards a nuanced challenge in the design of optical receivers, particularly those utilizing PIN diodes. PIN diodes are preferred in optical communication systems for their ability to convert light signals into electrical signals efficiently. The challenge lies in optimizing these diodes to handle a wide range of capacitive impedance while maintaining a large capacitive intrinsic region, which is crucial for achieving high performance in wireless optical receivers. A critical issue with typical PIN diodes is balancing the need for a large intrinsic region, which is beneficial for high-efficiency light conversion, against the capacitive impedance requirements of wireless optical receivers. A wide intrinsic region can lead to limitations due to the transit time of charge carriers across the junction, impacting the device's performance at high frequencies. The literature suggests that while a typical PN device can operate with up to 95% efficiency in the intrinsic region, this efficiency comes at the cost of bandwidth, particularly at higher frequencies. The delay in charge carrier delivery to the external circuit from the intrinsic region reduces the high-frequency bandwidth response. This is attributed to the time it takes for the majority of the signal charge to travel through the intrinsic region.

In [10], the bandwidth of a rectangular microstrip antenna is raised by 62.9% (1910 MHz) to the range 2.08 and 3.99 GHz by loading two C-shape notches of different sizes and a vertical slot inside a patch of antenna excited by 50 Ω line feed. In [11], a bandwidth enhancement was performed for wireless communication application and achieved the antenna gain and efficiency of greater than 2.89 dBi and 38.54%, respectively, with a peak gain of 9.41 dBi and a peak efficiency of 99.93%. In [12], bandwidth enhancement was achieved by shortening one edge of the main radiating patch to reduce the antenna’s footprint. The design exhibits stable patterns, with a measured peak gain and efficiency of 5.5 dBi and 86%, respectively. The bandwidth enhancement of 168% is achieved for MIMO antenna however, gain bandwith is not mentioed the system provide better isolation, structureand with lowcost, low directivity and distorted pattern and limited gain [13]. In [14] a symmetrically stair-shaped ground plane antenna fed by a coplanar waveguideis proposed. This antenna of size is 20 × 14 × 1.6 mm3 covers a very wide frequency range from 2.8 to 40 GHz. It exhibits a large variation of gain over its operating range, with a peak gain of 37.2 dB. Despite its advantages, it suffers from small gain and low directivity, which could limit its application in scenarios requiring consistent high-gain performance. In [15] tapered slot ground antenna is designed for bandwidth enhancement for both 4G and 5G applications within the same aperture. This antenna, measuring 158 × 77.8 × 0.381 mm, is built on an RT/Duroid-5880 substrate, which is known for its low dielectric constant (i.e. εr = 2.2) and very low loss tangent (i.e. tanδ = 0.0009), optimizing the antenna's performance. Among its key features, the antenna offers MIMO capability, which is crucial for achieving higher data rates and increased network capacity. It also exhibits a low user's hand effect, enhancing signal reliability and quality in mobile devices. The design facilitates ease of mobile integration, meeting the demanding requirements of contemporary wireless communication standards. However, it's not without its drawbacks, as the antenna exhibits high side lobe levels and poor matching at the 4G band, which could impact performance in certain scenarios. Reference [16] proposes the modified patch with a diagonal slot and metasurface, which is characterized by a dielectric constant (εr) of 2.2 and a low loss tangent (tanδ) of 0.0009. One of the standout features of this design is its ability to achieve circular polarization, which is highly desirable for various communication applications. Additionally, it maintains a stable radiation pattern across its operational bandwidth, contributing to its effectiveness in targeted applications. From a practical standpoint, its compact size, low profile, and the ease of fabrication are significant advantages, making it suitable for integration into a wide array of devices where space and complexity are constraints. Despite its many strengths, its limited gain might affect its suitability for applications where high signal strength is crucial.

To overcome the limitations imposed by the intrinsic region's width and to enhance signal bandwidth, frequency compensation is necessary. The proposed solution is this article involves a technique that combines automatic gain and bandwidth control to optimize the placement of the signal charge at the very edge of the intrinsic region, thereby minimizing delay and improving bandwidth. The proposal extends beyond optical communications to include video systems, suggesting a unified receiver front-end design that can serve both applications effectively. This approach leverages the similarities in the requirements for optical communications and video systems to create a versatile and efficient receiver design.

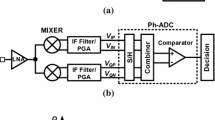

3 Modeling of 6G receivers with automatic bandwidth control & AG

The proposed technique for bandwidth enhancement in 6G receiver design innovatively integrates automatic bandwidth control (ABC) and automatic gain control (AGC) within a discrete-time modeling (DTM) framework. This cutting-edge approach is geared towards optimizing key performance metrics, including signal-to-noise ratio (SNR), gain stability, and bandwidth efficiency, particularly under fluctuating signal conditions. At the core of this architecture lies a transimpedance amplifier (TIA), which is pivotal in converting the current from an incoming optical signal (via a photodiode) into a voltage. The AGC component of this system dynamically adjusts the gain of the TIA to ensure a constant output amplitude, irrespective of the input signal strength. Concurrently, the ABC mechanism is tasked with modulating the system's bandwidth in real-time. This adjustment is crucial for optimizing the SNR by minimizing noise, thereby enhancing the receiver's overall efficiency and performance.

The most innovative aspect of the design proposed in this article is the incorporation of a discrete-time controller. This controller is responsible for governing the AGC and ABC mechanisms based on prevailing signal conditions, utilizing an optimization algorithm. Through the implementation of the DTM, the control system samples the receiver output at discrete intervals. This sampling allows for the precise and timely adjustment of both gain and bandwidth in response to any signal variations. By adopting this approach, the receiver design promises significant improvements in handling the dynamic and diverse conditions expected in a typical 6G network. The integration of AGC, ABC, and DTM ensures that the receiver can rapidly adapt to changing signal conditions, maintaining optimal performance metrics across a wide range of scenarios.

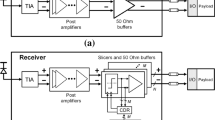

In this paper, 6G receiver design incorporating both ABC and AGC to address the optimization challenges in a DTM framework is proposed. The model is illustrated in Fig. 2. The receiver design aims to maximize performance metrics such as SNR, gain stability, and bandwidth efficiency under varying signal conditions.

The proposed receiver architecture integrates a transimpedance amplifier (TIA) with AGC and ABC mechanisms. The AGC adjusts the amplifier's gain to maintain a constant output level, while the ABC adjusts the bandwidth to optimize the SNR while minimizing the noise. The model includes a photodiode to convert an incoming optical signal into electrical current, a TIA that amplifies the current from the photodiode into a voltage. The AGC dynamically adjusts the TIA gain to maintain output amplitude while the ABC modifies the bandwidth in response to changing signal conditions to optimize the SNR. The importance of work falls in implementing the discrete-time controller that governs AGC and ABC based on the signal conditions and the optimization algorithm. The DTM for the AGC and the ABC is implemented using a discrete-time control system that samples the receiver’s output and adjusts the gain and bandwidth at discrete intervals. This model facilitates precise control and rapid adaptation to signal variations.

In the following, let s(t) represent the transmitted optical signal, where t is time. The received signal r(t) can be modeled as

where, G(t) is the gain applied by the AGC, L(t) represents the channel loss, including path loss and fading, and n(t) is the additive noise, including both ambient noise and system noise.

3.1 Adaptive composite bandwidth model

The bandwidth B(t) of the receiver can be adapted based on the current signal characteristics and system requirements. Let Bmin and Bmax be the minimum and maximum bandwidth limits, respectively. The adaptive bandwidth B(t) is a function of the received signal quality, such as

The function f() defines how the bandwidth adapts to changes in the SNR, which could be derived empirically or based on theoretical models of the expected system performance.

3.2 Automatic gain control model

The AGC adjusts the gain G(t) to keep the output signal amplitude within a target range to optimize the input to the ADC. The gain adjustment can be modeled as a control system problem, where the control input is the gain G(t), and the reference input is the desired signal level R. A simple AGC model could use a proportional control strategy such as

where, Kp is the proportional gain, R is the reference signal level, ∣r(t)∣ is the magnitude of the received signal after channel loss but before gain application. More sophisticated models might use proportional-integral-derivative (PID) control for improved stability and response time.

3.3 Optimization problem

The overall objective is to maximize data throughput while minimizing energy consumption and maintaining signal quality within acceptable limits. This is formulated as an optimization problem, with constraints on bandwidth, gain, and possibly other system parameters. The optimization algorithm aims to find the optimal gain and bandwidth settings to maximize the SNR while minimizing noise under varying signal conditions as illustrated in (4)

where, λ is a weighting factor that balances the SNR improvement against noise reduction. This optimization is adjusted according to constraints such as Gmin ≤ G ≤ Gmax and BWmin ≤ BW ≤ BW.

Max.

3.4 Discrete-time modeling

For practical implementation, the models described above are discretized. Thus, continuous-time signals and adjustments must be sampled and processed in discrete time intervals. Algorithms for dynamically adjusting B(t) and G(t) need to be designed, taking into consideration the processing delay and computational complexity. The models for adaptive bandwidth and AGC need to be integrated into a comprehensive system model that includes the transmitter, channel, and receiver to simulate and optimized overall system performance. This simplified framework outlines the core components of a mathematical model for an adaptive composite bandwidth and AGC receiver in a 6G wireless optical communication system. Detailed design would require further specification of the functions and control strategies for G(t), as well as extensive simulation and testing to refine the models and algorithms for practical application. The system is represented as a series of discrete-time processes that adjust the receiver's bandwidth and gain to optimize performance under varying signal conditions. The input signal x(t), affected by channel conditions including noise and interference, is sampled and processed to produce an output y[n] that approximates the original signal with desired adjustments. Continuous-time signals are sampled to be processed in a digital framework as in Eq. (5)

where x[n] is the sampled input signal, Ts is the sampling period, and n is the discrete time index. The system's response to these inputs is characterized by discrete adjustments of bandwidth B[n] and gain G[n]. The adaptive bandwidth mechanism dynamically adjusts the filter bandwidth to optimize the SNR and mitigate the impact of channel interference. The bandwidth at any discrete time n is a function of the current and past signal conditions as in Eq. (6):

where \({f}_{B}\) is a function determining the bandwidth adjustment based on the last Z + 1 samples of x[n]. The AGC dynamically adjusts the system's gain to maintain a consistent output amplitude, compensating for variations in the signal strength as in Eq. (6):

where \({f}_{G}\) is the gain adjustment function based on the last W + 1 processed but pre-gain adjusted samples \({y}{\prime}\left[n\right]\) and \({y}{\prime}\left[n\right]\) is the signal after bandwidth adjustment but before gain application. G[n] need to be designed with a focus on minimizing processing delay and computational complexity.

3.5 Bandwidth enhancement design and simulation results

The proposed 3-dB frequency response improvement method is to ensure that capacitance effect in an amplifier such as in transimpedance feedback amplifier is reduced. The device effect and stray capacitance are minimized in accordance with the open-loop gain [3, 17,18,19,20] as in Eq. (8)

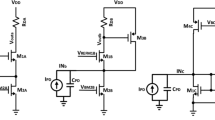

In (8), C represents photodiode plus the stray capacitance, Rf is the feedback resistance, and A is the open-loop amplifier’s gain. The performance of an amplifier is determined by the available intrinsic bandwidth and the open-loop gain to ensure the amplifier gain can stabilize. The change in the transimpedance amplifier refers to the original bandwidth for a particular photodiode when using 1 kΩ load at the 3 dB bandwidth of around 8 MHz, but after amplification exhibits around 20.4 MHz, with low impedance configuration. Therefore, the proposed solution to the capacitance reduction requirement is to employ the bootstrap configuration approach, where the dV/dt capacitive current element is being reduced [21,22,23]. Referring to Fig. 1, the capacitive current, instead of passing into the load resistance Rb, is bypassed into the device- and stray capacitances, Cd and Cs, respectively. The frequency rises as the capacitive current reduces the load current. Thus, conventional method of recovering the bandwidth is either to reduce the load resistance (and hence reducing the output voltage), or to reduce the photodetector area in order to reduce its capacitance. Therefore, the basic concept is to add an intrinsic region to the photodiode structure by virtue of reducing the capacitance but encounter minor setback of transit time within the device which eventually leads to improvement in terms of sensitivity and bandwidth [6, 24, 25]. The circuit diagram in Fig. 2 shows the proposed modified bootstrap amplifier. This circuit configuration employs the positive feedback technique with an amplifier gain near to unity instead of the capacitance reduction technique with respect to the amplifier gain. Assuming that IL represents load current IPh is the photocurrent and A is the voltage amplifier gain, the transfer function is as in Equations [1, 5, 26]

where Zf = Rf ‖Cf is shown in Fig. 3.

The receiver bandwidth according to Eq. (11) is determined from the RfCd time constant component in addition to the component Re3 and Cf, which is a complex function. Therefore, to ensure successful bandwidth adjustment for an amplifier with the feedback resistor Rf, a modification on Fig. 3 was proposed, by adding the capacitor Cp with a small capacitance in series with the emitter resistor Re3 (of Q3) at the second stage of the gain amplification. Considering this change, the circuit feedback is through resistor the Re3 and the capacitor Cp. Therefore, when the capacitor Cp is varied, thes receiver circuit’s bandwidth can be controlled. Hence when the value A approaches unity, the diode capacitance effect becomes smaller and therefore enhance the circuit bandwidth, in the assumption that there is no limit performance from the amplifier.

The main factors to consider when selecting a suitable component and circuit configurations for variable gain amplifier (VGA) is to ensure an AGC system with a wide frequency response and a VGA with desired control range [7,8,9,10,11,12,13,14,15,16, 23, 24, 27]. Figure 4 proposes a gain control circuit with automatic capabilities that uses two LMH6504 integrated circuits. According to its datasheet, and internal chip configuration, LMH6504 was chosen because the component incorporates input closed loop buffer, variable gain voltage control cell with a current feedback amplifier output. LMH6504 also provides a dc-coupled voltage-controlled gain stage that is wideband and incorporated with a high speed current feedback operational amplifier that is able to drive low impedance load directly. The gain control bandwidth for this configuration is 150 MHz. Referring to Fig. 4, U1 receives an input signal and produces an output signal that has constant amplitude. Negative feedback is provided through U2 configuration. Therefore, by setting potentiometer and Rb, a rectified gain control signal generated by U2 works against an adjustable bias level. The component Cb integrates the bias and negative feedback. This results in a resultant signal gain control which will be applied to U1 input gain control, Vg through pin 1. This bias allows U1 to adjust the output to be set at a normal level much lesser than the required maximum output amplifier specification. Component U2 completes the rectification by controlling the input gain control and the input amplifier with the U1 output signal. R1 and R2 form the voltage divider configuration that determine the rectifier gain. The allowable maximum gain set in Fig. 4 which is 9.65, can be determined using the following formula as in Eq. (12):

3.6 Frequency response analysis for integrated AGC and bandwidth control

Figure 5 shows the proposed integrated configuration as discussed earlier which is the combination of automatic gain control circuit, bootstrap transimpedance amplifier and voltage feedback amplifier.

combining Eqs. (15) and (16) yields:

The transfer function in Eq. (14) shows that the feedback resistor Rf is vital in determining the gain output for the receiver circuit. It is observed that the amplifier gain of the overall system increases as feedback resistor, Rf value increases, but the overall gain system decreases in the amplification second stage as the feedback resistor, Rf1 value increases. Figure 6 provides the output frequency response of the integrated configuration. The 3 dB bootstrap transimpedance amplifier gain is 53.3 dB while the frequency cut-off is 109.7 MHz. As Cfilter is varied from 50pF to 1nF, the adjustment system produces a range of bandwidth starting from 7.5 MHz and ending at 104.1 MHz. Looking at the second stage of the amplifier, the gain produced is only 10.4 dB. Thus, the proposed integrated ABC and AGC increases the overall receiver’s gain by up to 31.1 dB at the expense of the adjustable bandwidth range which falls in the range between 9.4 to 60.7 MHz.

This paper also presents the noise analysis for the circuit as in Fig. 5. The AGC circuit gain is calculated to be 10 dB when the voltage source is driven with a 50Ω source resistance [28]. The input noise for the AGC is calculated as

Equation (13) shows how the AGC voltage noise is determined:

The noise votage and current as function of frequency is:

\(V_{n}^{2} = 1.9e^{ - 17} {V \mathord{\left/ {\vphantom {V {\sqrt {Hz} }}} \right. \kern-0pt} {\sqrt {Hz} }}\) and \(I_{n}^{2} = 6.76e^{ - 24} {V \mathord{\left/ {\vphantom {V {\sqrt {Hz} }}} \right. \kern-0pt} {\sqrt {Hz} }}\),

RG = 100Ω while Rf = 1kΩ. Therefore, the noise figure for AGC is in (20)

The AGC circuit input and output noise densities are displayed in Fig. 7. The output result indicated around \(\frac{{6{\mu V}}}{{\sqrt {Hz} }}\) for input noise density, and \(\frac{{14{\mu V}}}{{\sqrt {Hz} }}\) for the output noise density. This graph also indicates that the noise AGC circuit main contribution is due to the lower end range frequency or probably flicker noise.

The frequency versus output noise density plot for the proposed combined configuration discussed in Sect. 3 is shown in Fig. 8. The measurement is taken at the AGC output system after the integrated composite amplifier system. The result shows an identical pattern as Fig. 6, indicating that output noise is high at the early stages between 10 to 100 Hz. The output noise after the combination of the bootstrap transimpedance amplifier and voltage feedback amplifier exhibits the lowest output noise density around \(\frac{{13.3{\mu V}}}{{\sqrt {Hz} }}\) and continues to decrease to around \(\frac{{1.6{\mu V}}}{{\sqrt {Hz} }}\) at 2 kHz. The value further reduces to near zero after 10 MHz.

4 Discussion on results

The key findings from the study related to gain, bandwidth, and noise performance in the context of a 6G wireless application receiver design include:

-

Gain Performance

-

The integrated AGC with bootstrap transimpedance amplifier configuration achieved an overall receiver gain of 31.1 dB.

-

Gain control is achieved using a circuit with LMH6504 integrated circuits, ensuring a wide control range and stable output.

-

Bandwidth Enhancement

-

The adjustable bandwidth capability of the receiver ranges from 9.4 to 60.7 MHz, facilitated by the proposed integration of AGC, bootstrap transimpedance amplifier, and voltage feedback amplifier.

-

The design effectively handles the trade-off between gain and bandwidth, with bandwidth adjustments allowing for optimal signal processing across a wide frequency range.

Noise Performance.

-

(1)

The proposed configuration exhibits low input and output noise density, contributing to an improved SNR.

-

(2)

The output noise spectral density for the combined configuration of bootstrap transimpedance amplifier and voltage feedback amplifier shows a low noise level, decreasing to near zero after 10 MHz.

-

(3)

The front-end noise analysis indicates that the design effectively minimizes the impact of flicker noise and other low-frequency noise sources on the receiver's performance.

In the rapidly evolving field of wireless communication, the transition from existing technologies to the promising horizon of 6G represents a critical leap towards achieving unparalleled connectivity, bandwidth, and data transmission capabilities. This transition underscores the imperative need for innovative solutions that can address the intrinsic challenges posed by new-generation networks. The literature review and examination of past work have laid down a foundation, highlighting the advancements and persistent challenges in the design of optical receivers, particularly those employing PIN diodes for efficient light-to-electrical signal conversion. These challenges revolve primarily around optimizing capacitive impedance while maintaining a large intrinsic region within PIN diodes to achieve high performance in wireless optical receivers.

Past work in the realm of bandwidth enhancement for wireless communication technologies has introduced various design strategies aimed at improving performance metrics such as gain, efficiency, and antenna footprint. Notably, designs have incorporated features like notches, vertical slots, and modified ground planes to enhance bandwidth and address the limitations of traditional PIN diodes at high frequencies. For instance, bandwidth enhancements have been achieved through the introduction of stair-shaped ground planes, tapered slot designs for dual-band applications, and the integration of metasurfaces for circular polarization. These designs, while advancing the field, often grapple with trade-offs between gain, bandwidth, and the physical constraints of antenna design, highlighting a recurrent theme of balancing efficiency against performance limitations in specific scenarios.

Contrasting previous endeavors, our research reported in this article introduces a novel framework that seamlessly aligns with the 6G communication paradigm, setting a new benchmark in the design of optical wireless receivers. By integrating Adaptive Composite Bandwidth and AGC techniques, our approach transcends traditional limitations, offering a more adaptive and dynamic response to the varying demands of 6G connectivity. Our proposed receiver design, leveraging a bootstrap transimpedance amplifier, not only addresses the large dynamic range challenges posed by varying input currents and photodiode efficiencies but also optimizes the gain-bandwidth product (GBP) through strategic capacitance selection. This optimization ensures enhanced signal quality by minimizing noise through bandwidth control and adapting gain in response to slight variations in input signals. The resultant configuration achieves a notable gain of up to 31.1 dB with a bandwidth adjustment ranging from 9.4 to 60.7 MHz, optimizing the GBP from 10.4 to 31.1 dB. This signifies a substantial improvement over previous works, which, despite their contributions, often faced limitations in gain, bandwidth, and adaptability to varying operational conditions.

In this work, performance metrics such as gain, efficiency, bandwidth, and the GBP cannot be overstated. These metrics serve as critical indicators of the technological advancements and their readiness to meet future demands. A closer look at recent studies and design innovations reveals a concerted effort to address these metrics, albeit with varying degrees of success and focus. Historical approaches to antenna and receiver design have shown promising results, with several studies making noteworthy contributions. For instance, a design tailored for WLAN/WiMAX technology reported a peak gain of 4.7 dB, highlighting the focused attempts to enhance gain within specific communication standards. Another effort achieved remarkable efficiency, boasting a gain greater than 2.89 dBi and an efficiency rate surpassing 38.54%, culminating in a peak gain of 9.41 dBi and an astonishing peak efficiency of 99.93%. This level of efficiency underscores the potential for achieving high-performance in wireless communication technologies. Meanwhile, a study aimed at MIMO antenna configurations managed a bandwidth enhancement of 168%, coupled with a measured peak gain and efficiency of 5.5 dBi and 86%, respectively, showcasing the possibilities in bandwidth and efficiency improvements. Despite these advancements, challenges persist. Some designs suffered from limitations such as high side lobe levels, poor matching at specific bands, and a notable lack of detailed quantitative metrics on gain and efficiency. These shortcomings emphasize the ongoing struggle to balance performance across all crucial metrics. The proposed receiver design incorporating Adaptive Composite Bandwidth and Automatic Gain Control (AGC) techniques marks a significant leap forward, especially in the context of 6G communication. This design achieved a bootstrap transimpedance amplifier gain of 53.3 dB with a frequency cut-off at 109.7 MHz. The bandwidth adjustment capability of this design, ranging from 7.5 to 104.1 MHz, coupled with a second-stage amplifier gain of 10.4 dB, represents a flexible and powerful response to varying signal conditions. The integration of AGC further elevates the system's performance, optimizing the GBP from 10.4 to 31.1 dB. This optimization not only signifies an enhancement in balancing gain and bandwidth but also positions this design as a pivotal solution for the high-performance requirements of future wireless communications. Comparing these advancements to past efforts highlights the substantial progress made in signal amplification, as seen in the peak gain of 53.3 dB. Although specific efficiency metrics were not detailed in this novel approach, the achievements in peak efficiencies from previous studies set a high benchmark for comparison.

Furthermore, the flexibility and range of the bandwidth adjustment in this new design surpass previous enhancements, indicating a broader applicability and potential for meeting diverse communication needs. The advancements presented in the latest research offer a compelling glimpse into the future of wireless communication technologies. By addressing key performance metrics through innovative designs and integration of advanced techniques, such as AGC, these advancements not only overcome previous limitations but also set new standards for efficiency, gain, and bandwidth optimization. As the demands of 6G communication continue to unfold, the potential of these innovations to meet and exceed these demands becomes increasingly apparent, heralding a new era in wireless connectivity. In the context of 6G's demanding requirements for ultra-low latency, high data rates, and pervasive connectivity, our work not only demonstrates superior performance in optimizing the GBP but also underscores a more adaptive approach to receiver design. This adaptability, characterized by the ability to dynamically adjust bandwidth and gain, positions our framework as a pivotal solution for 6G applications, offering a tailored response to the diverse and evolving needs of next-generation wireless networks. These findings underscore the effectiveness of the proposed receiver design in achieving a balance between gain, bandwidth, and noise performance, positioning it as a viable solution for enhancing the quality of service in 6G wireless applications.

5 Conclusion

In conclusion, this paper has delved into the realm of circuit design, proposing an innovative configuration aimed at elevating the receiver quality of service criteria in the context of 6G wireless applications. By strategically combining a range of techniques, the presented bootstrap transimpedance feedback amplifier configuration stands out as a promising alternative, showcasing commendable results in terms of bandwidth enhancement, low input noise, and wide dynamic range. From the perspective of circuit design, this paper presents an alternative configuration to achieve better receiver quality of service criteria, which are bandwidth enhancement, low input noise and wide dynamic range, using a combination of various techniques. This paper demonstrates a bootstrap transimpedance feedback amplifier configuration and obtains reasonable gain and excellent bandwidth adjustment. The proposed AGC, integrated with bootstrap transimpedance amplifier configuration, produces an overall receiver gain of 31.1 dB, with an adjustable bandwidth ability ranging from 9.4 to 60.7 MHz. From the receiver noise analysis perceptive, this paper demonstrates how the front-end noise can affect the input of a receiver. The results also show that a rapid increment value of relatively noise mostly from proportional square and cube receiver bandwidth terms effect, which is one of the factors limiting receivers from achieving low noise performance. The output noise spectral density demonstrates that bootstrapped transimpedance amplifier designed in this article is able to exhibit low noise level. The output noise for the bootstrap transimpedance amplifier and voltage feedback amplifier integration exhibits the noise density output value \(\frac{{13.3{\mu V}}}{{\sqrt {Hz} }}\) and decreases to the value \(\frac{{1.6{\mu V}}}{{\sqrt {Hz} }}\) at 2 kHz. It further reduces to near zero after 10 MHz. Therefore, the transimpedance amplifier with feedback resistor serves as an excellent choice as a front-end because of receiver design complexity trade-offs and demanding requirements faced in analogue circuit design.

Data availability

We've done a bunch of tests and simulations to see how well our new methods work, and we're happy to share the big picture findings in our paper. However, some of this information is a bit sensitive or special because it could be used to make new technology, so we have to be careful about who gets the full details. If you tell us why you want the data and what you'll use it for, we'll take a look and see if we can share it with you, making sure to keep any secret stuff safe. We really want to work with others to make 6G technology better, but we also need to protect certain information just to be safe.

References

Xiong W, Peng Z, Yao R, Guo Q, Chi C, Ji C. Systematic analysis of a modified uni-traveling-carrier photodiode under high-power operating conditions. Photonics. 2023;10(4):471.

Bellon J, Sibley MJN. Frequency response compensation of transit time limited pin photodiode. Electron Lett. 2000;36(14):1222–3.

Grzeslo M, Dülme S, Clochiatti S, Neerfeld T, Haddad T, Lu P, Tebart J, et al. High saturation photocurrent THz waveguide-type MUTC-photodiodes reaching mW output power within the WR3.4 band. Opt Express. 2023;31(4):6484–98.

Amraoui R, Aissat A, Vilcot JP, Decoster D. Frequency response optimization of PIN photodiode based on InGaAsN lattice matched to GaAs for high-speed photodetection applications. Opt Laser Technol. 2022;145:107468.

Li C, Xie S, Zhou G, Mao L, Qiu B. A low noise transimpedance amplifier for optical receiver. Rev Sci Instrum. 2021;92:034706.

Abdullah MFL, Green RJ. Noise analysis adjustable bootstrap transimpedance and voltage feedback receiver amplifier. J Appl Sci. 2011;11(23):3775–82.

Boucovalas AC. Indoor ambient light noise and its effect on wireless optical links. IEE Proc Optoelectron. 1996;143(6):334–8.

Barbio C, Mekonnen KA, Huijskens F, Koonen T, Tangdiongga E. Bidirectional gigabits per second spatial diversity link using POF for passive optical front-ends. J Lightwave Technol. 2022;40(20):6753–61.

Metin T, Emmelmann M, Corici M, Jungnickel V, Kottke C, Müller M. Integration of optical wireless communication with 5G systems. In: 2020 IEEE Globecom Workshops (GC Wkshps), pp. 1–6. IEEE, 2020.

Tripathi D, Srivastava DK, Verma RK. Bandwidth enhancement of slotted rectangular wideband microstrip antenna for the application of WLAN/WiMAX. Wirel Pers Commun. 2021;119:1193–207.

Alibakhshi-Kenari M, Naser-Moghadasi M, Sadeghzadeh RA, Virdee BS, Limiti E. Miniature CRLH-based ultra wideband antenna with gain enhancement for wireless communication applications. ICT Express. 2016;2(2):75–9.

Boukarkar A, Rachdi S, Merabet MA, Baguigui S, Adda Benziane K. Miniaturized frequency-reconfigurable single-feed multi-band antenna with bandwidth enhancement for wireless applications. J Electromagn Waves Appl. 2024;38(2):170–84.

Singhal S. Feather-shaped super wideband MIMO antenna. Int J Microw Wirel Technol. 2021;13(1):94–102.

Dastranj A, Lari G, Bornapour M. A compact dual band-notched SWB antenna with high bandwidth dimension ratio. Int J Microw Wirel Technol. 2021;13(1):87–93.

Kiani SH, Iqbal A, Wong SW, Savci HS, Alibakhshikenari M, Dalarsson M. Multiple elements MIMO antenna system with broadband operation for 5th generation smart phones. IEEE Access. 2022;10:38446–57.

Hussain N, Jeong M-J, Abbas A, Kim T-J, Kim N. A metasurface-based low-profile wideband circularly polarized patch antenna for 5G millimeter-wave systems. IEEE Access. 2020;8:22127–35.

Graeme JG. Photodiode amplifiers: op amp solutions. New York: McGraw Hill; 1985. p. 1–19.

Kohneh Poushi SS, Goll B, Schneider-Hornstein K, Hofbauer M, Zimmermann H. Area and bandwidth enhancement of an n+/p-well dot avalanche photodiode in 0.35 μm CMOS technology. Sensors. 2023;23(7):3403.

Alexander SB. Optical communication receiver design. London: SPIE Optical Engineering Press; 1997. p. 173–201.

Zhang N, Wen Z, Hou X, Wen W. Digital automatic gain control design with large dynamic range in wireless communication receivers. In: 2017 IEEE 17th international conference on communication technology (ICCT)

Abdullah MFL, Green RJ, Leeson M. Optical wireless communication front-ends. In: High Frequency Postgraduate Student Colloquium, 2004;3–8.

Ramachandrapura S, Ahmad F, Prosad A, Raghunathan V. Dual-carrier multiplexed laser-based hybrid transmitter for high data-rate indoor optical wireless communication. Optik. 2023;274:170522.

Street AM, Stavrinou PN, Edwards DJ, Parry G. Optical preamplifier designs for Ir-LAN applications. In: Optical free space communication links, IEE Colloquium, pp. 8/1–8/6; 1996

Maes D, Lemey S, Roelkens G, Zaknoune M, Avramovic V, Okada E, Kuyken B. High-speed uni-traveling-carrier photodiodes on silicon nitride. APL Photon. 2023;8(1):016104.

Abdullah NM, Abdullah MFL, Rus AZM. Mechanical reinforcement of conductive graphite/biopolymer thin film composite. ARPN J Eng Appl Sci. 2015;10(20):9772–5.

Abdullah MFL, Green R. Indoor optical wireless receiver—theory and design. Int J Integr Eng. 2011;3(2):31–8.

Moreira AJ, Valadas RT, de Oliveira Duarte AM. Characterisation and modelling of artificial light interference in optical wireless communication systems. In: Sixth IEEE international symposium on personal, indoor and mobile radio communications, vol 1, pp. 326–331; 1995

Abdullah MFL, Green RJ. Receiver amplifier technique for dynamic service quality adaptation in optical wireless communication. In: 4th international symposium on broadband communication, 2010

Acknowledgements

The authors would like to express their thankfulness to the School of Information and Technology, Melbourne Institute of Technology, Australia for providing the funding and resources for this research.

Funding

This research was supported and funded by the School of Information Technology and Engineering (SITE), Melbourne Institute of Technology, Melbourne, Victoria, 3000, Australia.

Author information

Authors and Affiliations

Contributions

Bhagwan Das (Concept, Experiment, Writing, Submission, Review, Editing). Johnson Ihyeh Agbinya (Review and Revise). Mohammad Faiz Liew Abdullah (Concept, Experiment, Writing, Review, Editing). Osama A. Mahdi (Editing, Review and Revise). Nawfal Ali (Review and Revise). Abdul Ghaffar (Editing, Review and Revise). Amoakoh Gyasi-Agyei (Review and Revise).

Corresponding author

Ethics declarations

Conflict of interest

Authors have no confilcit of interest by any mean.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Das, B., Agbinya, J.I., Abdullah, M.F.L. et al. Adaptive composite bandwidth and automatic gain control receiver for 6G wireless optical communication. Discov Appl Sci 6, 225 (2024). https://doi.org/10.1007/s42452-024-05882-6

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s42452-024-05882-6