Abstract

This research work designs a prototype of an active-loaded differential amplifier using Double-Gate (DG) MOSFETs. The following text outlines the prototype design with testing in developing the conceptual understanding of the differential amplifier and its design requirement. This designed model uses mathematical models while assessing possible limitations of the amplifier and the DG MOSFET. The designed amplifier exhibits a differential gain of 4 V/V, with a bandwidth of 1 MHz. The common-mode output and gain values were tested, along with the resultant CMRR to assess the overall performance of the differential amplifier designed.

Article Highlights

-

An active-loaded differential amplifier using Double-Gate (DG) MOSFETs has been designed using hardware circuits.

-

The designed amplifier exhibits a differential gain of 4 V/V, with a bandwidth of 1 MHz.

-

The common-mode output and gain values have been tested, along with the resultant CMRR to assess the overall performance of the designed differential amplifier.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The differential amplifier is one of the essential building blocks of electronic systems, commonly designed using operational amplifiers [1]. However, there are various advantages of using transistors to design this differential amplifier, namely higher input and output impedance. An operational amplifier comprises transistors, where transistors are designed to be a differential amplifier at the input terminals [2]. Thus, it is an alternative design method and component that may help to improve products for specific applications. The basic BJT and MOSFET-based differential amplifier consists of two transistors and two resistors and has been further developed by replacing the resistors with transistors. The advantages include its inherent single-ended output, improved Common-Mode Rejection Ratio (CMRR), and greater output impedance [3,4,5]. For cryogenic applications, Zavjalov et al. [6] have designed a differential amplifier for temperatures below 4 K (− 269 °C), while evaluating various parameters such as differential and common-mode gain at different temperatures to verify the design integrity at this level of application. A clear design process and circuital information were provided, showing the addition of a cascade input stage to reduce the Miller effect and voltage follower at the output stage to reduce the output resistance of the amplifier for their application.

A differential amplifier is often utilized with a current mirror to provide adequate current drive, preventing resistors from being the only current-limiting components. Deo et al. [7] have realized the effect of different current-mirror topologies affecting the differential amplifier’s performance. It has been found that the Widlar current mirror exhibits a larger CMRR but the smallest differential gain. In contrast, an active loaded differential amplifier exhibits the most significant differential gain but has an inferior CMRR w.r.t. the Widlar current source. Aziz et al. [8] have proposed a 90 nm single-stage FGMOS amplifier design. The scope of this work has helped highlight the main parameters that new amplifier design should focus on. AC analysis and slew-rate investigations were conducted, which shows a change. A simulation-based model was proposed and tested. Hashem [9] has designed an NMOS differential amplifier with passive loading using a modified Wilson current mirror. The output power which can be produced is 6.66 mW with an output resistance of 2.297 MΩ, observed from the current mirror. A considerable CMRR of 33.35 dB was obtained from this design.

Garcia-Perez et al. [10] have highlighted the need for differential amplifier design as part of an aperture array. Investigating various differential amplifier topologies, the gain of a balanced differential amplifier for a 50 Ω input was much higher than the gain of a fully-differential amplifier, where the minimum gain of the balanced topology was measured at 39 dB, and the maximum gain of the fully-differential topology was approximately 35 dB for a bandwidth of 1.3 GHz. Kabiri and Mokhtari [11] have used a differential amplifier to design Multi-Varied Logic (MVL) circuits, where the differential amplifier built uses a supply voltage of 0–5.5 V, as a dual-supply is used to improve the development of digital devices. Jain et al. [12] have implemented a two-stage differential amplifier using stacked transistors for bio-medical applications. Implemented in cadence and designed with a 45 nm CMOS process for a supply voltage of 0.85 V, the CMRR was measured at 178 dB at 100 Hz and power dissipation of 1.5 μW. It is inevitably noted these measurements prove their design is greatly efficient.

From the literature review, the parameters that must be paid careful attention to, involve the supply voltage (minimization of the maximum supply voltage and minimum supply voltage, to reduce power consumption), differential and common-mode gains, and resulting CMRR (differential gain should be maximized according to application requirements and be stable over a frequency range, whereas the common-mode gain should be minimized, resulting in a higher CMRR) [13].

These discussions show that the differential amplifier can always be improved in various aspects for many applications. In this research work, a differential amplifier has been designed and fabricated using the Double-Gate (DG) MOSFET. Authors have chosen this transistor in sight of the acceptance of the simulation-based model [14]. It also overcomes the Short-Channel Effects (SCEs) that arise as the downscaling is performed on transistor channel lengths [15]. SCEs include threshold voltage roll-off (decay of the threshold voltage due to a decrease in gate length) [16], subthreshold slope degradation, an increase in the OFF-current slope of the MOSFET, which contributes to leakage current [13, 16]. These non-ideal effects are a result of a decrease in the channel length of MOSFET devices, reducing the magnitude of the electric field present in the MOSFET [17]. However, modeling of the drain current and transconductance of the DG MOSFET has proven challenging, as equations and polynomials at the sub-micron level prove difficult to be computationally efficient and accurate [17]. For this reason, ICs have advanced by using multi-gate transistors, such as DG MOSFET, Tri-Gate MOSFET, and Pi-Gate MOSFET [18,19,20].

Pillay and Srivastava [20] have realized that the DG MOSFET provides twice the drain current flow compared to the traditional MOSFET, which improves various circuit parameters, increasing the device performance, and efficiency of the source follower circuit. Two dual-gate MOSFET source follower models, using DC and AC analysis, were realized in this work. In further advancement of that work, in this present research work, an active-loaded differential amplifier has been designed using a prototype set up to assess the differential gain, common-mode gain, frequency response, and CMRR [21]. The differential amplifier was previously designed by Pakaree and Srivastava [22] have examined the resistive-loaded model using the DG MOSFET. However, to extend that work, the authors have investigated the proposed design of a differential amplifier using the active-loaded differential-amplifier topology. Pillay and Srivastava [21] have presented a simulation-based design for this model.

In continuation of the work in [21], this present work highlights the design steps to construct an active-loaded differential amplifier using the DG MOSFET. Using this design process and the desired set of functional requirements, a design process that includes the respective biasing values of voltages, current, and component values has been presented. This paper has been organized as follows. Section 2 has materials and methods. Section highlights the design methodology of the differential amplifier. This includes biasing information and required resources. Section 4 provides a detailed analysis of testing and the results, including slew rate with comparative analysis with existing models. Finally, Sect. 5 concludes the work and recommends the future aspects.

2 Materials and methods

The Operational Amplifier (op-amp) is the most common component used in designing a differential amplifier [23]. Using two inputs and a single output provides a robust and efficient solution in subtracting two signals, fulfilling the purpose of a differential amplifier. However, under the hood, an op-amp utilises transistors to construct the native differential amplifier, along with other circuital building blocks, e.g., cascode stages and class-AB amplifiers [24]. There are two common differential amplifier topologies: the active-loaded and resistive-loaded differential amplifier [25]. For ease of use and design restrictions, a resistive-loaded differential amplifier is usually an attractive option, as it consists of two transistors and two resistors. This can be seen in Fig. 1a, where the RD is the drain resistance and M1,2 are the transistors used. A differential input voltage is applied to both transistors, and the differential output voltage (Vo1 and Vo2) can be given by [17]:

where, Avd is the differential gain. A single-ended output can be taken from any output terminal (Vo1 or Vo2) and ground (GND) and will be half the value of the differential output voltage given in Eq. (1).

The differential gain of this amplifier is determined by the transconductance gm and the value of the RD:

This topology was utilised in designing the differential amplifier [22], and analysed accordingly, exhibiting a differential gain of 8.69 V/V from simulation results. Expounding on this work, the authors have designed an active-loaded differential amplifier using the DG MOSFET. The active-loaded topology can be seen in Fig. 1b, where a single-gate MOSFET was used. Where the differential gain Avd can be given by:

which shows ro2 as the output resistance of T2 and ro4 is the output resistance of T4.

In designing and analysing the active-loaded differential amplifier, the following comparisons and advantages/disadvantages (over the differential amplifier designed by [22]) have been noted, which motivate the study of the active-loaded topology:

-

An improved CMRR is aided by the negation of non-ideal effects posed by passive-loads (resistors), such as resistor mismatch [3]. However, active loads (transistors) also introduce transconductance (gm) mismatch.

-

An inherent single-ended output, which aids in circuit design and simplification of IC and Very Large Scale Integration (VLSI) design.

-

It can be realized that common op-amp schematics from popular semiconductor manufacturers [26], such as the LM741 from Texas Instruments, LA6500 from ON-Semiconductors, and the LT1213 from Analog Devices be seen that an active-loaded topology is evidently used in all these op-amps with no use of the resistive-loaded topology.

In assessing the points above, a design process highlighting the use of the DG MOSFET in an active-loaded topology will provide a valuable reference. It can allow engineers to possibly replace the single-gate MOSFET in operational amplifiers and differential amplifier design as a whole. The DG MOSFET is a four-terminal component with a drain, source, and two gates (gate 1 and gate 2). The planar structure can be seen in Fig. 2.

The planar structure of Double-Gate MOSFET (S: Source, D: Drain, G1 and G2: Gate-1 and gate-2, SiO2: Silicon di-oxide) [2]

In this application’s biasing of the DG MOSFET, authors are constantly driving the DG MOSFET into saturation to provide stable amplification; hence, the body (or back-gate) of the DG MOSFET is connected to the source internally [2, 27, 28]. The body effect, which is responsible for potentially altering the threshold voltage of a MOSFET, can only be considered when VBS (VBody − VSource) < 0. The differential gain (using circuital components) achieved is 2 V/V at a cut-off frequency of 1 MHz. The input DC-offset range is 1–100 mV with an input peak-to-peak voltage range of 500 mV. These were achieved with drain current ID = 3 mA (under no-load conditions). To design the prototype, four BF998 DG MOSFETs have been used, with a 5 V, 0.5 A supply voltage.

3 Design methodology

-

(1)

Common-source amplifier design using DG MOSFET.

To simplify the amplifier’s design, one may realise the differential half-circuit of the schematic shown in Fig. 2 resembles a common-source amplifier. Figure 3 shows the basic layout for a common-source amplifier using a SG MOSFET [3]. A pseudo-schematic has been depicted in Fig. 4, showing the common-source amplifier using the DG MOSFET [29, 30].

The basic layout of the common-source amplifier using the SG MOSFET [3]

From ref. [21], a dual-rail power supply ± 12 V has been used. To reduce power consumption by removing the negative rail and further experimentation, a + 5 V single-rail power supply will be used. However, with the power supply at hand, it is rated at 5.89 V. To calculate the power consumption under no-load conditions:

where in the worst-case scenario, VDS = 5.89 V and ID = 3 mA, yields a power consumption of 17.7 mW. Here, gate-1 is utilised as an input for RF signals, and gate-2 is utilised for Local Oscillator (LO) inputs. However, gate-2 will solely be used to bias the DG MOSFET for the desired drain current of 3 mA. Since it has been stated the input-offset voltage VINoffset is 100 mV, VG1 = 0.1 V. While using the typical value noted by the datasheet, gate-2-to-source voltage VG2-S = 4 V, VG2 may be specified as 4.4 V. Thus, VS = 0.4 V. From Fig. 4 R6 can be calculated as:

where the voltage at the source VS = 0.4 V, ID = 3 mA, thus R6 = 133 Ω. E12 values of 100 Ω and 33 Ω can be used in series. Low resistance values will be chosen to reduce the minor effects of resistor noise when biasing gate 2 at a voltage of VG2 = 4.5 V. Given the power supply voltage of 5.89 V, R2 = 100 Ω and R3 = 33 Ω. To calculate the value of R5, which is the current-limiting resistor for the drain terminal, the value VDS may be assessed. The DG MOSFET must be driven into the saturation region to ensure stable amplification, thus providing a constraint in choosing a suitable VDS value. To design the common-source amplifier for the specified frequency response, resistor R4 and capacitor C1 may be used to create a low-pass response with the specified cut-off frequency of 1 MHz. If values fc = 1 MHz, C1 = 2.2 pF:

which yields a value of R4 \(\cong\) 72 kΩ. Using E12 values, 47 kΩ and 33 kΩ will be used in series. This, in turn, exhibits a frequency response with a cut-off of 904 kHz. Capacitor C2 can be chosen as 0.1 µF as a DC blocking capacitor [31,32,33] and C3 can be chosen as 47 µF. Figure 5 shows a prototype of the common-source amplifier. The differential gain of approximately 2 V/V (input signal of 397 mVpk–pk and the output signal of 1.66 Vpk–pk shown in Fig. 6, and a frequency response showing a cut-off frequency of 904 kHz (a reduction in mid-band gain, from 12.36 to 10.50 dB), the design process has been validated as shown in Fig. 7.

-

(2)

Differential amplifier design using common-source amplifier half circuits.

Figure 8 shows the schematic of the differential amplifier using the common-source amplifier half-circuits, where a single half-circuit is shown in Fig. 4. This may be labeled as the resistive-loaded differential amplifier using asymmetrical DG MOSFETs. The addition of the current source I1 (shown as “I1” in Fig. 8) of 6 mA is a sum of the equal drain currents for DG MOSFET M1 and M2.

-

(3)

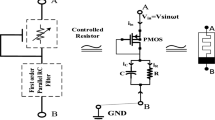

Active-loading using DG MOSFETs and Widlar current mirror

In improving the proposed design in Fig. 8, current-limiting resistors R5 and R7 will be replaced with DG MOSFETs, in unison with a Widlar current mirror replacing the ideal current source I1. This has been shown in ref. [21], which validates the feasibility of the proposed method of current control. The architecture of a Widlar current mirror can be seen in Fig. 9.

Widlar current mirror [3]

In the Fig. 9, the drain of Q1 and Q2 is connected to the supply voltage Vsupply (shown in Fig. 8), the current source Iin will be replaced by a resistor Rbias, which would bias the current mirror for the desired current. To calculate Rbias, the drain current of both common-source half-circuits is the sum of 6 mA:

To select an E12 value, 1 kΩ will be used. The significance of “active-loading” of a differential amplifier allows the resistors at the drain (or collector for a BJT) to be removed and replaced by current sources which allow the use of a current mirror. Current sources can be modelled using transistors and their output impedance is interpreted as what would be the drain resistances that have been replaced [3]. Configuring the DG MOSFET as a current source can be done using symmetrical DG MOSFETs, where both gate-1 and gate-2 will be connected [34, 35]. Figure 10 provides a bird’s eye view of the breadboard schematic of the proposed differential amplifier. The section enclosed in blue, employs a phase-shift of 180°, to provide a pair of differential signals, injected at the input (blue and yellow arrows, respectively), which are DG MOSFETs M1 and M2, from Fig. 8. The designed differential amplifier can be seen in Fig. 11, encompassed in white. The circuit enclosed in blue denoted the common-source amplifier was designed to provide two signals 180° out-of-phase. The output of the common-source amplifier is a 100 mVpk sinusoid, which forms input-1 of the differential amplifier, shown by the blue arrow. Input-2, shown by the yellow arrow, is the raw input signal from the function generator, which is a 20 mVpk sinusoid.

In Fig. 11, the prototype is shown in the bottom-right corner. The orange wire is the power connection (captured in the red box), signal-in is shown by the white wire (captured in a red box), input-1 of the differential amplifier is shown by the blue wire (captured by the blue box), and input-2 of the differential amplifier shown by yellow wire (captured by the yellow box).

4 Testing and analysis with discussions of the prototype design

The testing and other analysis has been performed for the Differential gain and frequency response, Common-mode gain and resulting CMRR, Slew rate measurement.

-

(1)

Differential gain and frequency response.

To demonstrate the differential gain of the amplifier, the removal of common-mode (DC) voltages should be shown, where only the difference of the AC components exists at the output [36]. This function demonstrates the functional requirement for a differential amplifier. In the Fig. 11, the input signals of 100 mVpk and 20 mVpk (208 mVpk–pk shown in Fig. 11a, 42 mVpk–pk shown in Fig. 11b are amplified by the gain of 2 V/V, as specified in Sect. 2.A. One may note that calculating VOpk, which would be the peak voltage of the output waveform with the gain applied from Eq. (1)

The resulting peak voltage can be seen in the oscilloscope image in Fig. 12 with input-1, input-2, and output of the differential amplifier. Providing a differential gain vs frequency plot to visualise the frequency response, the designed differential amplifier has a cut-off frequency of 1 MHz. In Fig. 13, the frequency response of the constructed differential amplifier has been observed. The bandwidth is noted as 1 MHz (the approximate − 3 dB frequency). Table 1 summarises the testing results of the amplifier.

-

(2)

Common-mode gain and resulting CMRR.

The common-mode gain can be assessed because the differential amplifier has been biased with a DC offset of 100 mV (applied to the input signal). The objective of the differential amplifier is to remove the DC offset applied to the input signals. Common-mode signals may be in electrical noise, which should be suppressed when generating a single-ended differential output signal [3, 36].

To find the common-mode gain, both inputs of the differential amplifier will be injected with the same signal. Figure 14 shows the output signal, which is unchanged for the frequency spectrum as shown in Table 1, where a 4 mVpk output can be seen. Thus, the common-mode gain:

From this, the CMRR can be calculated and shown in Table 2.

-

(3)

Slew rate measurement.

The slew rate of an amplifier is an usful parameter that indicates the effect of the parasitic capacitance of the amplifier. It is a large-signal parameter, typically measured in V/µS and is related to the rise time and other transient response parameters [38]. It can be defined as the maximum rate at which an amplifier’s output can change in response to a change in its input [37]. One would expect the slew rate to be directly equivalent to the change in time of the output signal but the slew rate can effectively determine this isn’t the case.

From an analysis into possible slew rate enhancement done by Singh et. al. [39], the fastest slew rate was produced by an Operational Transconductance Amplifier (OTA) using self-cascoded and local feedback techniques which was 158.3 V/µS. Other circuitry tested included a conventional OTA and one lacking the cascade input stage. Using an oscilloscope, a method to estimate the slew rate of an amplifier was described by [40]. This includes measuring the change in voltage over time between 10 and 90% of the signal amplitude. From Fig. 15, where the input signal’s frequency was 100 Hz with a peak-to-peak voltage of 96.8 mV, was injected into the amplifier, the slew rate can be measured as:

The slew rate for the above instance would be calculated as:

The values used for the computation of the slew rate can be found in Table 3 and it uses Eq. (6) to calculate. For peak-to-peak voltages of 200 mV, 500 mV, and 1 V, the slew rate was computed and presented in Fig. 16. Realizing the slew rate of the differential amplifier, its shortcomings can be observed at a higher frequency (shown by a drastic degradation in its slew rate at 1 MHz) and lower large-signal voltages (demonstrated by the lowest slew rate for 100 mVpeak-to-peak).

-

(4)

Comparison of existing topologies and the proposed topology.

To compare this work with the existing work, here in Table 4, a comparative analysis has been given for better understanding.

5 Conclusion and future recommendations

This work highlights the design steps to construct an active-loaded differential amplifier using the DG MOSFET. Using this design process and the desired set of functional requirements, a design process that includes the respective biasing values of voltages, current, and component values has been presented. It has been validated that all design requirements have been met from testing the designed differential amplifier. The differential gain of 2 V/V was chosen to exhibit basic amplification of the differential amplifier, along with a frequency range for which the given differential gain should be valid. The common-mode output and gain values were tested, along with the resultant CMRR to assess the overall performance of the differential amplifier designed. The prototype justifies the functional requirements and proves a better design process. The frequency response and slew rate were investigated to establish the differential amplifier's performance in the frequency domain.

The future work will include the design of notable electronic subsystems to expose and improve the shortcomings of the active-loaded differential amplifier, such as differential mixer, Voltage-Controlled Oscillator (VCO), or Low Noise Amplifier (LNA). Designing these devices will introduce the need for optimization of the proposed differential amplifier, e.g., load-carrying conditions would have to be considered. The output resistance must be monitored at high frequencies, RF losses must be assessed and improved to meet functional requirements, etc. A proposed method of improving the input resistance and frequency response includes the addition of a cascade input stage-to improve the input resistance, hence improving the frequency response.

Data availability

All data and materials used to prepare this manuscript are available in this document.

References

Gayakwad RA (2016) Op-amps and linear integrated circuits, 4th edn. Pearson Publication, London

Srivastava VM, Singh G (2013) MOSFET technologies for double-pole four throw radio frequency switch. Springer, Switzerland. https://doi.org/10.1007/978-3-319-01165-3

Sedra A, Kenneth S (2004) Microelectronic circuits. Oxford University Press, New York

Fiore J (2002) Operational amplifiers and linear integrated circuits: theory and applications. Jaico Publishing House, Mumbai

Bell D (2007) Operational amplifiers and linear ICs. Oxford University Press, New York

Zavjalov V, Savin A, Hakonen P (2019) Cryogenic differential amplifier for NMR applications. J Low Temp Phys 195:72–80. https://doi.org/10.1007/s10909-018-02130-1

Deo GS, Totlani JA, Mamidi KE, Mahamuni CV (2020) Performance analysis of BiMOS differential pair with active load, Wilson and Widlar current mirrors, and diode connected topology. In: 4th international conference on intelligent computing and control systems (ICICCS), Madurai, India

Aziz F, Ahmad N, Musa F (2018) Design topology: 90 nm single stage FGMOS amplifier design. In: AIP conference proceedings 2045. https://doi.org/10.1063/1.5080903

Hashem MA (2019) Analysis and simulation of MOSFET differential amplifier. J Eng Sustain Dev 23(6):1–10. https://doi.org/10.31272/jeasd.23.6.1

Godoy A, Villanueva JAL, Tejada J, Palma A, Gamiz F (2001) A simple subthrehold swing model for short channel MOSFETs. Solid-State Electron 45:391–397. https://doi.org/10.1016/S0038-1101(01)00060-0

Mokhtari A, Kabiri P (2021) A new multi-valued logic buffer and inverter using metal oxide semiconductor field effect transistor based differential amplifier. Int J Eng. https://doi.org/10.5829/ije.2022.35.01A.14

Jain P, Sharma SDS, Joshi AM (2021) Design of two stage differential amplifier with stacked transistors for biomedical applications. Wirel Personal Commun. https://doi.org/10.21203/rs.3.rs-583725/v1

Neamen DA (2012) Semiconductor physics and devices. McGraw Hill, New York

NXP Semiconductors (2010) Silicon N-channel dual-gate—BF998, NXP Semiconductors

Abede H, Cumberbatch E, Morris H, Tyree H, Numata T, Uno S (2009) Symmetric and asymmetric double-gate MOSFET modeling. J Semicond Technol Sci 9(4):225–232. https://doi.org/10.5573/JSTS.2009.9.4.225

Hossain M, Khosru DQ (2013) Threshold voltage roll-off due to channel length reduction for a nanoscale n-channel FinFET. Int J Emerg Technol Comput Appl Sci 13(125):152–156. https://doi.org/10.1109/TED.2009.2028403

Taur Y, Liang X (2004) A continuous, analytic drain-current model for DG MOSFETs. IEEE Electron Device Lett 25(2):107–109. https://doi.org/10.1109/LED.2003.822661

Weis M, Emling R, Schmitt-Landsiedel D (2009) Circuit design with independent double-gate transistors. Adv Radio Sci 7:231–236

Park J, Colinge JP, Diaz CH (2001) Pi-Gate SOI MOSFET. IEEE Electron Device Lett 22:405–406. https://doi.org/10.1109/55.936358

Pillay D, Srivastava VM (2022) Realization with fabrication of dual-gate MOSFET based source follower. Silicon. https://doi.org/10.1007/s12633-022-01922-1

Pillay S, Srivastava VM (2022) Design of an active-loaded differential amplifier using double-gate (DG) MOSFETs. SN Appl Sci 4(8):1–15. https://doi.org/10.1007/s42452-022-05100-1

Pakaree JE, Srivastava VM (2019) Realization with fabrication of double-gate MOSFET based differential amplifier. Microelectron J 91:70–83. https://doi.org/10.1016/j.mejo.2019.07.012

Texas Instruments (2015) LM741 operational amplifier. Texas Instruments, Texas

Gupta A, Rai MK, Pandey AK, Pandey D, Rai S (2021) A novel approach to investigate analog and digital circuit applications of silicon Junctionless-Double-Gate (JL-DG) MOSFETs. Silicon. https://doi.org/10.1007/s12633-021-01520-7

Razavi B (2001) Design of analog CMOS integrated circuits. McGraw-Hill, New York

High speed, ±0.1 μV/˚C offset drift, fully differential ADC driver (ADA4945-1) datasheet. Analog Devices, 2019

Ajay S (2021) Resistances and ESD reliability study of core–shell channel junctionless DG MOSFET. Silicon 13(5):1325–1329. https://doi.org/10.1007/s12633-020-00527-w

Maduagwu UA, Srivastava VM (2021) Sensitivity of lightly and heavily dopped cylindrical surrounding double-gate (CSDG) MOSFET to process variation. IEEE Access 9:142541–142550. https://doi.org/10.1109/ACCESS.2021.3121315

Maduagwu UA, Srivastava VM (2020) Channel length scaling pattern for cylindrical surrounding Double-Gate (CSDG) MOSFET. IEEE Access 8:121204–121210. https://doi.org/10.1109/ACCESS.2020.3006705

Gray PR, Hurst PJ, Lewis SH, Meyer RG (2009) Analysis and design of the analog integrated circuit, 5th edn. Wiley, Singapore

Arnub IBK, Ali MT (2018) Design and analysis of logic gates using GaN-based double gate MOSFET (DG-MOS). J Sci Eng 17(1):1–13. https://doi.org/10.53799/ajse.v17i1.3

Zhang P, Li B, Li W, Li L (2021) Influence of inhomogeneous residual charges on the stress of filter capacitor components. IEEE Access 9:134289–134297. https://doi.org/10.1109/ACCESS.2021.3116200

Gowthaman N, Srivastava VM (2021) Capacitive modeling of CSDG MOSFETs for hybrid RF applications. IEEE Access 9:89234–89242. https://doi.org/10.1109/ACCESS.2021.3090956

Mandapathi V, Nishanth P, Paily R (2011) Study of transistor mismatch in differential amplifier at 32nm CMOS technology. Int J Comput Sci 1(1):109–115

Colinge JP (2004) Multiple-gate SOI MOSFETs. Solid-State Electron 48:897–905. https://doi.org/10.1016/j.sse.2003.12.020

Gray PR, Hurst PJ, Lewis SH, Meyer RG (2009) Analysis and design of analog integrated circuits. Wiley, New Jersey

Martin M Measuring slew rate or rise time, Axiometrix. https://www.ap.com/blog/measuring-slew-rate-or-rise-time/. Accessed 7 July 2022

Hung CH, Zheng Y, Guo J, Leung KN (2020) Bandwidth and slew rate enhanced OTA with sustainable dynamic bias. IEEE Trans Circuits Syst II: Express Briefs 67(4):635–639. https://doi.org/10.1109/TCSII.2019.2924983

Singh A, Soni S, Niranjan V, Kumar A (2018) Slew rate enhancement. In: Conference on advances in computing, communication control and networking (ICACCCN). https://doi.org/10.1109/ICACCCN.2018.8748664

Williams I (2015) Slew-rate lab. https://training.ti.com/sites/default/files/docs/precision-labs-op-amps-slew-rate-presentation.pdf. Accessed 10 July 2022

Acknowledgements

Authors are thankful to Mr. Logan Pillay, Chairperson of TESP, Mr. Cecil Ramonotsi, CEO, Eskom Development Foundation, South Africa and Mr. Tshidi Ramaboa, Eskom Academy of Learning, Human Resources, Midrand. The authors are also thankful to Ms. Leena Rajpal, Public Relations Officer, University of KwaZulu-Natal, Durban, South Africa, for providing various support to carry on this research work.

Funding

This research work is funded by the Electricity Supply Commission (Eskom), South Africa, dated 31 Jan 2020, under the Tertiary Education Support Programme (TESP).

Author information

Authors and Affiliations

Contributions

SP and VMS conducted this research; SP has designed and analyzed the model with data and wrote this article; VMS has verified the result with the designed model; all authors had approved the final version.

Corresponding author

Ethics declarations

Conflict of interest

The authors have no relevant financial or non-financial interests to disclose.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Pillay, S., Srivastava, V.M. Prototype design and modeling of active-loaded differential amplifier using Double-Gate MOSFET. SN Appl. Sci. 5, 107 (2023). https://doi.org/10.1007/s42452-023-05326-7

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s42452-023-05326-7