Abstract

This study presents a high common-mode rejection ratio (CMRR), and high power-supply rejection ratio (PSRR) current-mode instrumentation amplifier (CMIA) to overcome the limitations of existing differential voltage second-generation current conveyors (DVCCII)-based CMIAs in achieving high CMRR. The design is based on a fully differential second-generation current conveyor block with a novel circuit design following by a current subtracting stage. The CMIA is designed and laid out in 130 nm CMOS technology operating under ± 1.2 V supply voltage in Cadence software. The post-layout simulation results show that the CMIA achieves low-frequency voltage and current CMRR- BW of 228.8 dB–10 kHz and 246 dB–10.6 kHz, respectively, with PSRR + /PSRR- of 108.2 dB/99.7 dB, power consumption of 507 µW, and a core area of 0.0015 mm2. The unique quality of the circuit is that, it does not need well-matched active blocks, but inherently improves CMRR, bandwidth, and PSRR; hence it gains an excellent choice for integration.

Article highlights

-

Highly accurate amplifier is designed to detect very weak signals of information (such as biomedical signals), and amplify them for further processing.

-

This circuit has two different input terminals to accommodate both voltage and current signals.

-

The final circuit is very small and consumes low power. Thus, it is a good choice for seamless integration to develop portable systems.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

In the last decades, due to the increasing demand for portable and battery powered equipment and advances in technology downscaling trend, researchers and designers of analog processors have been encountered with some major challenges in the design of low-power low-voltage (LPLV) circuits and systems [1,2,3]. Current-mode (CM) signal processing was envisioned as a promising solution to design small and fast LPLV circuits and thus gained more popularity [3,4,5,6,7]. The major advantages of CM processors over the voltage-mode (VM) processors include wide dynamic range and bandwidth (BW), simple circuitry, high speed, low supply voltage and power consumption [4,5,6]. The incorporation of a high-CMRR instrumentation amplifier (IA) is crucial in many analog/mixed-mode systems such as data acquisition, biomedical circuits and control systems in order to suppress the unwanted common-mode signals along with the desired signals of information [1,2,3,4,5]. Several different voltage-mode instrumentation amplifiers (VMIA) have been reported so far, but they seriously suffer from gain-BW trade-off, and need for precisely matched resistors to achieve high CMRR [8,9,10]. As a result, the conventional VMIAs have been gradually replaced by current-mode instrumentation amplifiers (CMIA) [11,12,13].

The CMIA structures can be divided into two main configurations based on input signals as: the low input impedance CMIAs compatible with current input signals [14,15,16] and the high input impedance ones compatible with voltage input signals [8, 9]. The low input impedance CMIAs utilize the advantages of CM signal processing and have attracted great interests especially after the introduction of CM alternative of Wheatstone bridge (Azka cell) [17]. However, most of the reported CMIAs are of the high input impedance ones [8, 9] whose structures are classified into second-generation current conveyors (CCII)-based CMIAs [15, 19] and current sensing-based CMIAs [8, 20].

CCIIs are active blocks that have been used in designing different analog circuits and systems such as amplifiers [18,19,20], oscillators [21], analog switches [22, 23], and active filters [24, 25] to grant the benefits of CM circuit design. Although CMRR performance of CCII-based CMIAs is not limited by matching resistors to improve CMRR, they need well-matched active block pairs to achieve higher CMRR. For example, two topologies of CCII-based CMIAs by Wilson [15] and Kaulberg [26] which are suitable for floating loads and both floating and grounded loads, respectively, are reported. Based on experimental results in [15] and [26], CMRR performance of the CMIAs was controlled entirely by the quality and matching of CCII blocks; also, high differential gain and BW was achieved simultaneously while by varying the resistive load, CMRR was almost unchanged. To avoid this matching constraint, differential voltage second-generation current conveyors (DVCCII)-based CMIAs were introduced [10, 20]. Although DVCCII-based CMIAs contain only one active block, they are compatible with only voltage input signals. Among all of the reported CMIAs, those based on fully differential second-generation current conveyors (FDCCIIs) [13, 14] have been of great interest since they employ only one active block and thus no critical component matching conditions are required. Moreover, FDCCII-based CMIAs are compatible with differential input terminals that can be adapted to both voltage and current input signals and differential output terminals.

This paper proposes a FDCCII-based CMIA benefiting from the following features: a) the circuit is designed based on CM circuit techniques and benefits from all advantages of CM signal processing. b) The CMIA has been designed based on only one block of FDCCII with novel circuit design; thus, there is no need for well-matched active blocks to achieve high CMRR. c) Despite the conventional VMIA, in the designed CMIA for a good range of output resistive load there is almost no dependency between gain and BW meaning that the differential gain can increase while the BW remains unchanged. d) Also, the designed CMIA contains one low-impedance differential input in addition to another high-impedance one to process and amplify both current and voltage input signals, respectively. e) Finally, a current subtracting stage has been added to the main block to further improve CMRR and realize a high CMRR CMIA. The rest of the paper is organized as follows: in section II an overview of the FDCCII building blocks is provided. Transistor-level implementation of the CMIA and a detailed design description are presented in section III. Post-layout simulation results along with Process, Voltage, and Temperature (PVT) effect on the performance of the proposed FDCCII and the CMIA, implemented in TSMC 130-nm CMOS technology, are presented in section IV. Finally, section V concludes this work.

2 Fully differential second-generation current conveyors blocK

Functional block diagram with the directions of current and voltage along with the operational matrix of a typical FDCCII are shown in Fig. 1 and Eq. (1), respectively [5]. FDCCII is a current-mode active building block consists of two consecutively connected voltage and current buffers with six terminals, conventionally denoted as Y+, Y–, X+, X–, Z+, and Z–, as illustrated in Fig. 1. Ideally, there is a unity differential voltage gain across X and Y terminals (Vxd/ Vyd = 1) and a unity differential current gain between Z and X terminals (Izd/ Ixd = 1). The ideal input impedance at Y, input (output) impedance at X and output impedance at Z nodes are infinite, zero (infinite), and infinite, respectively. Practically, the non-ideal impedances at any abovementioned terminals, results in undesirable effects on the functionality of FDCCII.

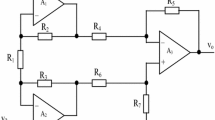

The setup block diagrams of the implemented CMIA including the FDCCII followed by a current subtraction stage for voltage and current inputs are shown in Fig. 2a and b, respectively. The current subtracting circuit provides a single-ended topology enabling the CMIA to drive grounded loads.

Also, the current subtractor cancels out the common-mode components of the output current signals at Z terminals resulting in a significant improvement in CMRR, which is a key characteristic of an IA.

The operation of the CMIA can be described based on the type of the input signal as follows. First, as it is shown in Fig. 2a, for voltage-input configuration, the unity gain voltage buffer between Y and X terminals transfers input voltage signals from Y to X [5] and assuming an ideal current conveyor, X+ and X- are receiving identical common mode signals. Thus, no common mode current signal is produced through the external resistor, Rext. As a result, no common-mode current signal conveys from X to Z terminals through the current buffer, and hence no common-mode current passes through the resistive load (RL). However, in real case, the existence of the common-mode signals cannot be ignored.

In case of current-input configuration, the current signal is applied to the low-impedance differential input terminal of X (Fig. 2b) and Y terminals are grounded. The common-mode components of the current signal are conveyed from X to Z through the unity-gain current buffer. Assuming a perfectly matched current mirrors in the current subtractor, any potentially common-mode current components can be removed at the final output using the current subtractor leading to higher voltage and current CMRR.

3 Current-mode instrumentation amplifier circuit

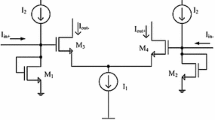

The design is mainly focusing on improving CMRR, targeting high-performance CMIA. The CMOS realization of the designed CMIA is shown in Fig. 3 consisting of the FDCCII and the current subtracting stage. Like most of the FDCCIIs [14, 27], the voltage tracking performance depends on the matching tolerances between output currents of two transconductors (M1–M8). Transistors M1–M2 and M3–M4 are the differential pairs of the input transconductor stages that share active loads of M25–M26. The differential pairs must be tightly matched to achieve a unity differential voltage gain from Y to X terminals. Using translinear loops in X terminals (including MT1–MT8), the internal impedances of X nodes get reduced resulting in very low impedance input terminals with higher absorption of current signal. A common-mode feed forward (CMFF) approach has been employed using M5-M8 to decrease common-mode voltage/current signals at nodes B, C, X+, and X-. In common mode condition, any common mode signals at Y (X) input terminals generate current signals in M2 and M3 (M1 and M4) and the same current signals will be generated in M6 and M7 (M5 and M8). Then, M23-M26 generate the same current signals with negative sign (as M23–M26 are NMOS devices) and add them to B and C. Thus, at node B and C the effect of common mode current signals is removed following by the cancellation of the effect of common mode signals at X nodes. The CMFF technique makes voltage/current signals at B (C) and X+ (X-) to remain unchanged in the presence of common mode signals resulting in CMRR improvement.

To avoid amplification of common-mode voltage signals at M11 and M12 drains (D and E), another CMFF circuit was employed using current mirrors M11-M13 and the pair of M29- M30. Any common mode signals at B and C generate common mode current signals in M27 and M28. Then, M29–M30 apply the same current signals (as the current signals in M27 and M28) with negative sign to current mirror M11–M13 and node D and E. Thus, the common-mode current signals of D and E nodes are cancelled following by the cancellation of common mode signals at X nodes and further improvement of CMRR. M31-M34 are current buffer stages between X and Z terminals that should be matched to achieve a unity differential current gain. At Z terminals, the simple current mirror M18–M20 along with transistors M35–M36, act as a CMFF technique. These transistors remove common-mode currents passing through Z terminals by adding the same current signals with negative sign to Z terminals resulting in current and voltage CMRR improvement.

The bias voltage of the current and voltage buffers is provided by Vocm. This voltage is generated by the CMFB (Common Mode Feed Back) block consisting of the current mirror M16-M17 and differential pair M37–M38. The function of the CMFB block is to set the common-mode voltages of X nodes to zero using negative feedback approach. By considering the internal mismatches in the FDCCII, the presence of common mode signals at Y terminals results in nonidentical common mode signals at X+ and X-. As a result, a common mode current signals flows through the external resistances Rext due to the difference between X+ and X- potentials. This current signal changes the common-mode voltage of node Vicm. (M37 gate) This voltage variation, stimulates differential pair M37–M38 to change M38 drain voltage (Vocm) using M16 and M17. Variation in Vocm changes common-mode currents passing through M14–M15 using a negative feedback connection that finally prevents the common-mode currents to pass through MT1–MT2. As a result, the common mode signals at X+ and X- are removed.

The current subtracting stage consists of three improved Wilson current mirrors (M39-M56) with cascade active loads (M57–M64) [27] as it is shown in Fig. 3. The first current mirror (M39-M41, M48–M50) sends Iz+ to the final output (node out in Fig. 3). The second and the third current mirrors (M42- M44, M51- M53, and M45-M47, M54-M56) convey -Iz- to the output.

In common mode condition, \({I}_{z+,com} \cong {I}_{z-,com}\) and in differential mode condition \({I}_{z+,diff} \cong {-I}_{z-,diff}.\) At the output node,\({I}_{out}={I}_{z+}- {I}_{z-}\) flows through the resistive load connected to the output (RL). This means (as expressed in Eq. 2), ideally the common-mode current signals of Z+ and Z- are removed at the output current flow through RL, while the differential ones are doubled. This results in the improvement of differential gain and reduction in common mode gain which can be translated into a significant improvement in CMRR. In the following sections, the performance of the CMIA with and without current subtracting stage is studied in detail to investigate the effect of adding the current subtracting stage on the performance of the CMIA.

The voltage and current CMRRs are obtained using Eq. (3) and Eq. (4) where \({\varepsilon }_{1(2)}\) and \({{\varepsilon }^{^{\prime}}}_{1(2)}\) are the current tracking errors of the current subtracting stage for differential and common-mode signals, respectively and βi for i = 1–9 are defined gains and errors (the detailed derivation is described in the Appendix). Also, the internal resistance of X terminals can be expressed using Eq. (5).

4 Post-layout simulation results and discussion

The proposed circuit is designed and laid out in TSMC 130 nm single-poly, eight-metal CMOS process and its performance is evaluated using CADENCE software tool after parasitic (RC) extraction. Figure. 4 shows the CMIA layout which occupies an active area of only 37 × 42 µm2. The transistor dimensions used in this design are listed in Table 1. In this simulation, the following parameters are set: Rext = 450 Ω, RL = 1 kΩ, the bias voltage applied to the gates of M9, M10, MT11, and MT12 (VBB) is 0.6 V, and the bias voltage of the current subtracting stage (VSB) is 0.5 V, such that each transistor of the input differential pairs (M1–M8) have a current bias of approximately 4.2 µA.

4.1 Core fully differential second-generation current conveyors characterization

In this section, the performance of the stand-alone FDCCII is evaluated to ensure that the performance of the main building block is sufficient to support the CMIA operation. The post-layout and Monte Carlo (MC) simulation results on the most important design metrics of the FDCCII block including common mode and differential mode voltage and current gains between X and Y as well as Z and X, respectively, the BW of the differential gains, the internal impedance in X and Z terminals, and power consumption for 1000 iterations are given in Table 2. For differential signals, the FDCCII achieves an input voltage tracking error of ~ 0.009 from Y terminal to X terminal (\(1 - \frac{{V_{xd} }}{{V_{yd} }}\)). In addition, the output differential current tracking error from X to Z+(-) terminal (\(1 - \frac{{I_{z + \left( - \right)} }}{{I_{xd} }}\)) is approximately 0.024. The FDCCII also has a low impedance of 16.1 Ω at current input terminal of X+ (X-) and a high output impedance of ~ 687 kΩ at terminal Z+ (Z-). The frequency response of X terminal internal resistance, Rx, is shown in Fig. 5 which shows a low-frequency value of 16.1 Ω with a 3-dB BW of 2.53 MHz. MC simulation results demonstrate that the common-mode voltage and current gains are more susceptible to the device mismatches than the differential ones.

4.2 Current-mode instrumentation amplifier characterization

The frequency responses of voltage and current CMRRs of the CMIA consisting of the FDCCII followed by the current subtracting stage are shown in Fig. 6. The designed CMIA achieves a high voltage CMRR of 228.8 dB with 3-dB BW of 10.0 kHz and a high current CMRR of 246 dB with 3-dB BW of 10.6 kHz at a supply voltage of ± 1.2 V. Figure 7a shows voltage and current CMRR magnitude at DC over different Rext. An average voltage and current CMRR magnitude of ⁓220 and ⁓240 dB are obtained, respectively, when Rext varies from 400 Ω to 500 Ω. Differential voltage and current gain-bandwidth products (GBPs) with different resistive loads (RL) changing from 1 kΩ to 300 kΩ are shown in Fig. 7b. Also, Fig. 7c and d shows the differential voltage gain and current gain of the CMIA over different RL. From Fig. 7b, it is obvious that for 1 kΩ ≤ RL < 32 kΩ, both voltage and current GBPs were linearly increasing with the output load, indicating that the differential voltage/current gain increases with an increase in RL, while the BW remains almost constant as shown in Fig. 7c and d. In this range of RL, the trade-off between gain and BW that inherently exists in voltage-mode circuits is almost negligible. For RL ≥ 32 kΩ, the compromise between gain and BW develops, leading to a decrease in GBPs rate. For RL ≥ 100 kΩ, the CMIA behaves similar to a voltage mode circuit as the GBPs remain almost constant with increase in RL suggesting that the magnitude of the differential gains is inversely proportional to the BW. The magnitude of differential gain, common mode gain, and CMRR at DC frequency over different RL for the CMIA with voltage and current input signals, are shown in Fig. 7e and f, respectively. Based on the figures, it is obvious that by increasing the RL, the differential gain magnitude increased, but increasing RL resulted in the decrease of common mode gain magnitude; as a result, the CMRR for both voltage and current signals remained almost constant over different RL. Figure 7g and h shows the voltage and current CMRR magnitude at DC over different VBB, changing from 0.95 × VBB (∆VBB = − 5%) to 1.05 × VBB (∆VBB = + 5%) while ∆VSB is 0%, + 5%, or − 5%, respectively. Based on Fig. 7g and h, the voltage and current CMRR magnitudes are > 180 dB while bias voltages are changing by ± 5% and this magnitude of CMRRs are close to Monte Carlo results shown in Fig. 8. Also, the current CMRR magnitude is more sensitive to variations in the bias voltages when compared to that of voltage CMRR.

a Voltage and current CMRR magnitude at DC over different Rext varying from 400 to 500 Ω. b Voltage and current GBP c differential voltage gain, and d differential current gain for different RL from 1 kΩ to 300 kΩ. e and f the magnitude at DC frequency of differential, common mode and CMRR over different RL for the CMIA with voltage and current input signals, respectively. g Voltage and h current CMRR magnitude at DC over different VBB and VSB. Note: in b–h Rext is 450 Ω

The impact of local process variations on voltage and current CMRRs of the CMIA and their BWs is investigated using Monte Carlo (MC) analysis with 1000 runs. The obtained results are shown in Fig. 8 indicating that both the current and voltage CMRRs have almost equal mean values of ~ 185 dB with ~ 11.3 kHz of 3 dB-BWs. The positive and negative PSSR curves (PSRR+ and PSRR−) are depicted in Fig. 9. The PSRR+ and PSRR − are 108.2 dB and 99.7 dB at DC frequencies, respectively. Figure 10 illustrates the input referred noise of the CMIA from 10 to 100 kHz. The rms value of the input referred noise is 3.61 μV, integrated from 10 to 1 kHz. The simulation results also indicate that the output offset of the CMIA is 1.67 µV. Table 3 summarizes the performance of the CMIA and compares it with the single FDCCII block. In the case where the current subtractor is detached from the FDCCII outputs, and two load resistors of 1 kΩ are connected to Z+ and Z−, while other circuit parameters and simulation conditions remain unchanged. The results verify the effectiveness of incorporation of the current subtracting stage in the CMIA as it enhances current and voltage CMRRs by 131 and 110 dB, respectively, while increasing power consumption by only 12%.

4.3 Process, voltage, and temperature variations' influence

In this section the robustness of the proposed CMIA against process, voltage, and temperature (PVT) variations is investigated in details. The simulated differential voltage gain from X to Y and differential current gain from Z to X for the FDCCII block in different process corners including Typical-Typical (TT), Slow-Slow (SS), Fast-Slow (FS), Slow-Fast (SF), and Fast–Fast (FF) are shown in Fig. 11a and b, respectively. In Fig. 11a and b, the worst corners of FS and FF shows a maximum of ~ 10 and ~ 5% variation in differential voltage and current gains, respectively, when compared to TT condition. In addition to the FDCCII, the aforementioned five process corners for the simulated voltage and current CMRRs of the CMIA are shown in Fig. 11c and d, respectively. For the CMIA, the average low-frequency voltage/current CMRR over different process corners is 204.1 dB/200.2 dB while a maximum variation of 16.5%/32.9%, with respect to the TT corner, is observed at FF/FF corner. Moreover, 3 dB-BW for the voltage/current CMRR remains above 7.94 kHz/7.82 kHz in the worst corner (SS/FS).

The performance summary of the CMIA over temperature range of − 25 °C to 75 °C at ± 1.2 V supply voltage is shown in Table 4. A minimum CMRR of ~ 170 dB is achieved for both current and voltage signals at − 25 °C which is quite comparable to that of the recently reported CMIA designs [14, 19, 27]. Despite the CMRR magnitude, the voltage/current CMRR 3 dB-BW is less vulnerable to the temperature changes as it remains above 10 kHz/9.5 kHz over the entire temperature range.

In addition to ± 1.2 V supply voltage, the CMIA is characterized for lower supply voltages of ± 1.0 V, ± 0.8 V, and even ± 0.6 V at room temperature as it is shown in Table 4. The CMIA exhibits nearly similar CMRRs’ performances with ± 1 V and ± 0.8 V while the CMRRs’ BWs are approximately scaled down with the voltage supply. Also, it shows 15.2%/17.8% and 13.1%/23.3% voltage/current CMRR reduction when voltage supply is reduced from ± 1.2 V to ± 1 V and ± 0.8 V, respectively. While a voltage/current CMRR of 185.6 dB/191.9 dB is obtained from ± 0.6 V supply voltage (which corresponds to only 18.8%/21.9% reduction in voltage/current CMRR compared to ± 1.2 V nominal supply voltage at room temperature), the power consumption significantly decreases from 507.2 to 72.8 µW which can be translated into ~ 86% reduction, as it is shown in Table 4.

Table 5 summarizes the CMIA performance and compares it to previously published designs. The novel CMIA exhibits superior performance in terms of CMRR for both voltage and current inputs without the need for accurately matched components. To make a fair comparison, a figure of merit (FoM) is defined in Eq. 6.

In Eq. 6, \(CMRR_{{\text{V}}}\) and \(CMRR_{{\text{I}}}\) are low-frequency voltage and current CMRRs, respectively, \(BW_{{{\text{CMRR}}_{{\text{V}}} }}\) and \(BW_{{{\text{CMRR}}_{{\text{I}}} }}\) are their corresponding 3-dB BWs (in kHz), and \(P\) is the power consumption (in µW). The FoM reflects the ability of a CMIA to reject the frequency components of common-mode signals at a given power consumption. To provide a fair comparison, same voltage/current CMRR and BW are assumed in FoM calculations when either of the data was not reported.

5 Conclusion

In this paper, a novel high CMRR CMIA in 130-nm CMOS technology is proposed. The CMIA includes an FDCCII to accurately convey the differential signals which is followed by a current subtracting stage to remove the common-mode components from the output current. The employed CMFB and CMFF techniques along with an accurate common-mode current subtraction stage allows the CMIA to achieve a high CMRR for both types of input signals. Post-layout simulation results have demonstrated the robustness of the CMIA against PVT variations. The CMIA’s ability to efficiently operate with 50% of its nominal supply voltage as well as the small silicon area, and low power dissipation makes it suitable for battery-powered and portable health monitoring systems. Future research focuses on realizing the circuit using the same technology and demonstrate its high CMRR performance and feasibility for fabricating standalone health monitoring devices such as highly sensitive portable stethoscopes for measuring electroencephalography (EEG) signals.

Data availability

The datasets generated during and/or analyzed during the current study are available from the corresponding author on reasonable request.

References

Turner JS (2002) New directions in communications (or which way to the information age?). IEEE Commun Mag 40(5):50–57. https://doi.org/10.1109/mcom.2002.1006972

Caviglia S, Gastaldo P, Zunino R, Caviglia DD, (2014) A high-linearity design for rail-to-rail fully differential current conveyors. 21st IEEE International Conference on Electronics, Circuits and Systems (ICECS) 550–553. https://doi.org/10.1109/ICECS.2014.7050044

Annema AJ, Nauta B, Van Langevelde R, Tuinhout H (2005) Analog circuits in ultra-deep-submicron CMOS. IEEE J Solid-State Circuits 40(1):132–143

Toumazou C, Lidgey FJ, Haigh D (Eds), (1990) Analogue IC design: the current-mode approach. Vol. 2, Presbyterian Publishing Corp. ISBN: 0863412157

Ferri G, Guerrini NC, (2003) Low-voltage low-power CMOS current conveyors. Springer Science & Business Media. ISBN: 978-1-4020-7486-8; https://doi.org/10.1007/b105853

Archana S, Madhavi BK, Krishna IM (2016) Design of CMOS current mode and voltage mode winner take all circuit on 180nm technology. ICEEOT. https://doi.org/10.1109/ICEEOT.2016.7755014

Broomandnia H, Azhari SJ (2015) Design of a fully differential current buffer (FDCB) based on a new common mode feedforward (CMFF) based common mode separation technique. KBEI conference. https://doi.org/10.1109/KBEI.2015.7436074

Douglas EL, Lovely DF, Luke DM (2004) A low-voltage current-mode instrumentation amplifier designed in a 0.18-micron CMOS technology. CCECE 3:1777–1780. https://doi.org/10.1109/CCECE.2004.1349760

Azhari SJ, Fazlalipoor H (2008) CMRR in voltage-op-amp-based current-mode instrumentation amplifiers (CMIA). IEEE Trans Instrum Meas 58:563–569. https://doi.org/10.1109/TIM.2008.2005559

Ahmad M et al (2020) An auto-calibrated resistive measurement system with low noise instrumentation ASIC. IEEE J Sol State Circuits 55:3036–3050. https://doi.org/10.1109/JSSC.2020.3017639

Azhari SJ, Fazlalipoor H (2000) A novel current mode instrumentation amplifier (CMIA) topology. IEEE Trans Instrum Meas 49:1272–1277. https://doi.org/10.1109/19.893269

Silverio AA, Reyes RS, Chung WY (2012) A low power high CMRR CMOS instrumentation amplifier based on differential voltage–current conveyor for beta-dispersion range bio-impedance applications. Recent Res Circuits Systems, Multimed Autom Control 5:31–36

Panchal A, Jain PK, Ajnar DS, (2011) Instrumentation Amplifier using Differential voltage second generation current conveyor (DVCCII) in standard 0.18 μm CMOS technology. International Journal of Engineering Science and Technology (IJEST), 3. ISSN: 0975-5462. https://www.researchgate.net/publication/228450319_Instrumentation_Amplifier_using_Differential_voltage_second_generation_current_conveyor_DVCCII_in_standard_018_mm_CMOS_tech

Safari L, Minaei S (2013) A novel resistor-free electronically adjustable current-mode instrumentation amplifier. Circuits Syst Signal Process 32:1025–1038. https://doi.org/10.1007/s00034-012-9522-y

Toumazou C, Lidgey FJ, Makris CA, (1989) Current-mode instrumentation amplifier. In IEE Colloquium on Current Mode Analogue Circuits 8–1

Das DM et al (2014) Design considerations for high-cmrr low-power current mode instrumentation amplifier for biomedical data acquisition systems. ICECS. https://doi.org/10.1109/ICECS.2014.7049969

Azhari SJ, Kaabi H (2000) AZKA cell, the current-mode alternative of Wheatstone bridge. IEEE Trans Circuit Syst I Fundam Theory Appl 47:1277–1284. https://doi.org/10.1109/81.883322

Sobhy EA, Soliman AM (2010) Realizations of fully differential voltage second generation current conveyor with an application. Int J Circuit Theory Appl 38:441–452. https://doi.org/10.1002/cta.566

Eldeeb MA et al (2017) A 0.4-V miniature CMOS current mode instrumentation amplifier. IEEE Trans Circuits Syst II Exp Briefs 65:261–265. https://doi.org/10.1109/TCSII.2017.2685589

Gupta M, Arora TS (2020) Various applications of analog signal processing employing voltage differencing current conveyor and only grounded passive elements: a re-convertible approach. SN Applied Sciences 2:1–18. https://doi.org/10.1007/s42452-020-03379-6

Malik S et al (2016) A CCII-based relaxation oscillator as a versatile interface for resistive and capacitive sensors. 3rd International Conference on SPIN. https://doi.org/10.1109/SPIN.2016.7566719

Alarcon E et al (2004) CCII-based analog integrated circuit for sliding-mode control of switching power converters. Analog Integr Circ Sig Process 38:203–213. https://doi.org/10.1023/B:ALOG.0000011168.00276.84

Monpapassorn A (2002) An analogue switch using a current conveyor. Int J Electron 89:651–656

Choubey CK, Tiwari G, Paul SK (2016) CCII based multifunction inverse filter. ICAECCT. https://doi.org/10.1109/ICAECCT.2016.7942574

Zhu Z, Bai W (2016) A 0.5-V 1.3-μW analog front-end CMOS circuit. IEEE Trans Circuits Syst II Express Briefs 63:523–527. https://doi.org/10.1109/tcsii.2016.2530879

Khan AA, Al-Turaigi MA, Ei-Ela MA (1995) An improved current-mode instrumentation amplifier with bandwidth independent of gain. IEEE Trans Instrum Meas 44:887–891. https://doi.org/10.1109/19.392876

Ahmadi S, Azhari SJ (2019) A LP, Very High-CMRR, wide-bandwidth FDCCII-Based CMIA adapted to both current and voltage inputs. Arab J Sci Eng 44:6727–6740. https://doi.org/10.1007/s13369-018-3601-8

Zhang S, Zhou X, Gao C, Li Q (2022) A 130-dB CMRR Instrumentation amplifier with common-mode replication. IEEE J Solid-State Circuits 57:278–289. https://doi.org/10.1109/JSSC.2021.3090100

Qian Y et al (2019) A high gain and high CMRR instrumentation amplifier for biomedical applications. IEEE ICICM. https://doi.org/10.1109/ICICM48536.2019.8977189

Konar M et al (2019) Improvement of the gain accuracy of the instrumentation amplifier using a very high gain operational amplifier. IEEE DevIC. https://doi.org/10.1109/DEVIC.2019.8783414

Zhang S, Zhou X, Gao C, Li Q (2021) An AC-Coupled Instrumentation amplifier achieving 110-dB CMRR at 50 Hz With Chopped Pseudo resistors and Successive-Approximation-Based Capacitor Trimming. IEEE J Solid-State Circuits 56:277–286. https://doi.org/10.1109/JSSC.2020.3010816

Funding

This research did not receive any specific grant from funding agencies in the public/commercial sectors.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors have no relevant financial or non-financial interests to disclose.

Ethical approval

This article does not contain any studies with human participants or animals performed by any of the authors.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Appendix

Appendix

This section describes the governing equations of the proposed FDCCII. In the following calculations, Rext has not been considered.

1.1 Voltage gain between X and Y

If differential input voltage of \(V_{{Y_{diff} }} = V_{{Y_{ + } }} - V_{{Y_{ - } }}\) (\(V_{{Y + { }}} = { } - V_{{Y - { }}} = \frac{{V_{{Ydiff{ }}} }}{2}\)) is applied to Y-terminals, Eq. (7) to Eq. (8) could be concluded. The drain currents of M1 (M2) and M5 (M6) can be written as Eq. (7), where VsM1 and VsM5 are the source voltages of M1 and M5.

Applying KCL at the source of M1, we arrive at:

using (7) and (8), small signal voltage and internal resistance at node B(C) can be written as Eq. (9) and (10):

where Ais can be derived based on Eq. (1) and (2) as follow:

When differential voltage signal is applied to the input nodes (Y+, Y-), as \(V_{gs1} = V_{gs3} ,{ }V_{gs2} = V_{gs4} ,{ }V_{gs5} = V_{gs7} ,{ }V_{gs6} = V_{gs8}\) and M1-M8 have the same bias current, we can assume that \({ }g_{m1} = g_{m3} ,g_{m2} = g_{m4} ,g_{m5} = g_{m7} ,g_{m6} = g_{m8}\). In addition, in the denominator of Eq. (11) \(r_{{o9\left( {10} \right)}} \left( {g_{m1\left( 6 \right)} + g_{m2\left( 5 \right)} + g_{m3\left( 8 \right)} + g_{m4\left( 7 \right)} } \right) \gg - 1\). As a result, A1-A8 can be expressed as Eq. (12) and \(V_{B\left( C \right)}\) can be simplified to Eq. (13). On the other hand, when a common-mode voltage is applied to the input nodes (terminals Y) since the bias currents of M1–M8 are not equal anymore, A1-A8 are defined as previously shown in Eq. (11).

The drain voltage and internal resistance of M11(M12) are shown in Eq. (14) and (15), respectively. Using Eq. (14) and KCL at X+ (X-), voltage at X+ (X-) node is as Eq. (16).

Based on Eq. (1) to (10), voltage at terminal X is simplified as follow:

where,

For differential-mode voltage signals (\(V_{Y + } = - V_{Y - } = \frac{{V_{Ydiff} }}{2}{ }\)), based on Eq. (18), we get:

As a result, the differential gain between X and Y is as follow in Eq. (19).

Where,

On the other hand, According to Eq. (18) , for common-mode voltage signals (VY+ = VY- = VYcom) we have:

and therefore, the common-mode gain between X and Y can be derived as follows:

where,

1.2 Current Gain between X and Z terminals

The internal resistance of X nodes can be derived as:

For current input signals, the output current signal at Z terminals are as follow:

Where,

For differential mode current signals, ignoring the channel-length modulation effect \(\left( \lambda \right)\), the current gain between Z and X terminals can be expressed as follow:

According to Eq. (18) and (19), we have:

Assuming that \(r_{x + } = r_{x - } = r_{x}\) and, as a result \(V_{xdiff} = r_{x} { }i_{xdiff}\), and using Eq. 24)ifferential current Z terminal can be calculated by Eq. (26) as follow.

Therefore, the differential current gain between X and Z nodes can now be expressed as given in Eq. (27).

Where,

Moreover, the differential voltage gain between Y and Z nodes can be calculated by Eq. (28) as follows:

For common-mode current signals (VY+ = VY- = VYcom), the common-mode current signal at Z terminals are given by Eq. (29).

Assuming \(r_{x + } = r_{x - } = r_{x} { },{ }r_{x} \ll { }2R_{ext} {\text{ and as }}V_{xcom} = r_{x} { }i_{xcom}\), then froEq. (11a), we obtain:

As a result, the common-mode current and voltage gains between X and Z nodes can be derived as given in Eq. (31) and Eq. (32), respectively.

Where,

1.3 Voltage and CurrenCMRR

By combining Eq. (19) and (21), voltage CMRR between X and Y terminals is obtained as given in Eq. (27), (30)

Using (28) and (31), voltage CMRR between terminals Z and Y can be expressed by Eq. (34) as follows.

Finally using Eq. (27) and (31), current CMRR between Z and X terminals can be simplified to Eq. (35).

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Ahmadi, S., Mahmoudi, A., Maddipatla, D. et al. A current mode instrumentation amplifier with high common-mode rejection ratio designed using a novel fully differential second-generation current conveyor. SN Appl. Sci. 5, 34 (2023). https://doi.org/10.1007/s42452-022-05247-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s42452-022-05247-x