Abstract

This research paper proposes the design of an active-loaded differential amplifier using the Double-Gate (DG) MOSFET. This differential amplifier employs feedback and simplifies a previously designed topology by reducing it to a single-ended output instead of a differential one. Other topologies have been referred to determine the benchmark of this design work. The DG MOSFET has been utilized for its high-frequency characteristics, Radio Frequency (RF) applications, and possible advantages in scalability. Electronic device simulation determines the technical feasibility of this differential amplifier using DG MOSFET. The designed differential amplifier exhibits a differential gain of 1.7–1.8 V/V and −3 dB cut-off frequency of 42 MHz. The amplifier can be used in various applications using this methodical design process and the circuital information.

Article Highlights

-

The Double-Gate (DG) MOSFET has been used to design an active-loaded differential amplifier by building common electronic systems.

-

The design process has been outlined to achieve parameters (avoiding mathematical models) using simulation, and manufacturer’s, resources.

-

An array of methods to improve performance have been deduced, as the physical implementation of the amplifier has been considered.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

According to Moore's law, transistor-usage doubles every two years in Integrated Circuit (IC) design, forcing engineers and scientists to consider the effect of scalability, performance, and overall ease of use [1, 2]. Therefore, scaling of transistors to the nanometer level was introduced, which included drawbacks such as Short-Channel Effects (SCEs), etc., resulting in the breakdown of the transistor’s integrity. Nowadays, transistor channel lengths are shorter than 0.13 μm and are constantly being reduced [3]. Various considerations have been made to ensure the magnitude of the electric field in a transistor remains constant, despite reducing its dimensions. This includes constant-field scaling and threshold voltage approximation, which are the main factors to assess for scaling.

To provide a working solution to standard building blocks such as amplifiers, switches, and other electronic subsystems, the Double-Gate (DG) MOSFET is a possible substitute for analogue transistors and their limitations. The differential amplifier is one of the evident subsystems in various electronic devices to reduce electrical noise and suppress excess DC voltage components. Its differential gain, Common-Mode Rejection Ratio (CMRR), bandwidth, and input offset voltage can be characterized. Various topologies exist in analyzing the research and development of the differential amplifier, and each has its pros and cons. Shilpa and Srilatha [4] have simulated four topologies using single-gate MOSFETs designed for a supply voltage of 1.8 V. The purpose was to simulate differential amplifier topologies at 180 nm. It realized that the resistive-loaded differential amplifier consumes more power at 6.04 mW than the active-loaded differential amplifier, which consumes 2.13 mW. It was concluded that the active-loaded topology is favorable but is deficient in its 3 dB-bandwidth as opposed to the resistive-loaded topology.

Mandapathi et. al. [5] have analyzed the effect of device mismatch for 32-nm single-gate MOS technologies. To reduce the effects of device mismatch, which are resultant of a 16% difference in device dimensions, various circuit modifications were added to the active-loaded topology. These modifications include splitting signal transistors, adding source-degenerative resistances, and Common-Mode Resistive Feedback (CMFB). After applying these changes, several measurement parameters (gain, frequency response, power usage) improved. The addition of the CMFB exhibits a massive improvement (more than 800 kHz) in 3 dB-bandwidth and total harmonic distortion (9% less) from the control, which is the active-loaded topology. However, the basic active-loaded topology has a superior output swing. Comparing the effectiveness of the modifications to reduce device mismatch and analyzing the resulting parameters provides an example that highlights a need for constant attention to detail, minimizing trade-offs, and improving performance.

The challenge of this design was attempting to use the DG MOSFET as a prominent component in the differential amplifier to demonstrate it as a usable component in typical electronic applications. To apply the DG MOSFET, various mathematical and circuital models have been presented for the drain current [6,7,8], transconductance [6] (for symmetrical and asymmetrically-driven DG MOSFETs), and logic gate-modeling [9, 10]. However, these models still require biasing information to achieve voltages and currents to meet design specifications, allowing one to use the component.

Authors have looked to apply the DG MOSFET in amplifier models (previously in the class AB amplifier [12], and in this paper, the differential amplifier) that can be used in native amplifier design and possibly, replace single-gate MOSFETs. Research of bulk CMOS scaling is approaching a limit, and the alternatives are considered a point in the direction of the DG MOSFET [11, 13]. Pakaree and Srivastava [14] have designed a DG MOSFET-based resistive-loaded differential amplifier and analyzed its small-signal model. Testing conducted in simulation shows a differential gain (differential output) of − 8.69 V/V, common-mode voltage gain (single-ended) of − 0.40 V/V, and CMRR of 19.06 dB (single-ended output), and simulated frequency response of 32 MHz. Maduagwu and Srivastava [15] have analyzed a parallel gate differential amplifier with a signal conditioning unit set at Vi1 = Vi2 = 3.05 V, 4.05 V, and 5.0 V dc and current mirror circuit at current 2 mA to measure the ac differential voltage gain (Vo1 − Vo2)/ (Vi1 − Vi2). Due to two transistors being used, the hamming / noise is canceled, and a clear output signal can be achieved. Pillay and Srivastava [12] have used the DG MOSFET in audio amplifier design for its low power and low noise application, high to low power voltage regulation, etc.

To extend the work on the differential amplifier, the emphasis is on low power applications with common parameters, i.e., differential gain, bandwidth, and CMRR. The DG MOSFET is equipped for use in low-power RF applications given by its low noise figure of applications up to 1 GHz and smaller drain currents. Using the aforementioned MOSFET, an active-loaded differential amplifier will be designed. The device’s working principle ought to be established, providing comparisons to the design of the differential amplifier using the DG MOSFET against the single-gate MOSFET. The design method followed would expose biasing information and design methods for this multi-gate transistor.

The amplifier designed in this paper poses advantages over common differential amplifier models, such as its single-ended output and improvement in CMRR and would consist of active and passive components. For simulation purposes, an electronic device simulator has been used. The BF998 DG MOSFET has been used in this research work [16]. This has been chosen for this design because it allows actual device parameters to be considered and the SPICE model is readily available. This research paper has been organized as follows. Section 2 emphasizes the design process highlighting the essential components of device design. Section 3 has the schematic for the differential amplifier design based on the DG MOSFET and analyzes its structure, design, and biasing information. Section 4 provides measurements from a simulation perspective of the differential gain, common-mode gain, frequency response, and CMRR. In addition, it has a comparative analysis of this differential amplifier model with a resistive-loaded differential amplifier that was designed using the double-gate MOSFET. Finally, Sect. 5 concludes the research work and recommends the future aspect of the work.

2 Materials and methods

This section highlights the necessary background knowledge to understand the demands of the design process and DG MOSFET. Figure 1 represents the process of this design. To simulate the aforementioned differential amplifier, the LTSpice simulation tool was used, given it provides a comprehensive circuital model for the BF998.

2.1 Double-gate (DG) MOSFET basics

A planar model of the DG MOSFET structure is shown in Fig. 2, where the gates are arranged. The immunity of Silicon-on-Insulator (SOI) structures, which the DG MOSFET utilizes, can be owed to the insulation layer inserted underneath the Silicon substrate. Compared to bulk CMOS technology used in the single-gate MOSFET, SOI MOSFETs offer lower coupling capacitance between the conducting channel and substrate. From this, SOI devices provide a higher current drive. The buried oxide layer provides a lower leakage current, specifically from the drain or source, to the substrate [17]. Other Short Channel Effects (SCE's), such as Drain Induced Barrier Lowering (DIBL) and Subthreshold Slope (SS) degradation, persist in conventional bulk CMOS technology due to MOS downscaling.

Schematic of the Double-Gate MOSFET [14] (S: Source, D: Drain, G1 and G2: Gate-1 and gate-2, SiO2: Silicon dioxide)

Focusing on the technology and fabrication of the DG MOSFET, using two gates allows the user to actively manipulate the electric field developed by giving more control of the channel than in singular gate devices. This control leads to be enhanced transconductance of the DG MOSFET, as predicted in the early 1980s [18].

However, in noting various advantages, there is still a need for continued research into SOI fabrication processes and multi-gate MOSFETs. Considering essential parametrization, such as explicit threshold voltage models that include gate-to-source voltages for both gates of the DG MOSFET and their relationship has been used, as they are popular single-gate (SG) MOSFETs such as the 2N7000 [19,20,21].

2.2 Differential amplifiers and their operation

Overall, the importance of the differential amplifier or a pair of differential signals cannot be exaggerated in large-scale analogue and digital electronics. Devices such as Analogue-to-Digital Converters (ADC), microcontrollers, fuel cells, Universal Serial Bus (USB), and the Ethernet communications protocol are electronic devices and communications frameworks and components that utilize differential signals. Hence, their signal sink ought to have a differential amplifier at its input [22,23,24]. A differential signal has two signals overall, with each the opposite polarity of the other. The differential amplifier's output is ideally produced by amplifying the difference between the input signals by way of applying a differential gain. The output should also reject any common-mode signals. In superior designs, it may reduce input harmonic distortion [25]. A basic differential signal process is shown in Fig. 3. The advantage of a differential signal is that both signals that make up the differential signal are affected equally by unwanted noise or harmonics. Thus, the resulting differential single-ended output is unaffected by unwanted noise or harmonics. The difference between the signals provides the physical property quantified by the differential signal output [26]. Let the input signals of the operational amplifier be V- and V+, the signal which is viewed at the receiver would be A(V-—V+), where ‘A’ is the differential gain. If a non-ideal signal is added to the differential pair of signals, it will affect each input signal equally. Processing the difference between the input signals allows effective minimization of any non-ideal elements, such as noise of any type of Electro-Magnetic Interference (EMI), as opposed to using a single-ended signal.

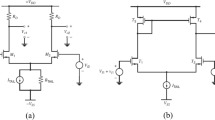

The applications that would employ a differential pair of signals are typically where the signal source (sensors or other electronic measurement tools) and signal sink (microcontroller or any different user interface) are separated by a large distance or require precision in the quantifiable measurements taken (e.g. pressure, temperature etc.) [27]. There are many derivations of the differential amplifier architecture; however, the basic topologies of the differential amplifier can be found in Fig. 3(b) and (c), which are the resistive-loaded differential amplifier and the active-loaded differential amplifier models, respectively. The resistive-loaded model is ineffective in minimizing non-ideal effects such as resistive mismatch. However, it is easily configurable and from Fig. 3(c), one can determine the expected output as [25,26,27]:

where I is the current supplied by the current source, VDD is the supply voltage, and R is biasing resistors. The output can be taken in a single-ended or differential output.

However, in this research work, the active-loaded architecture has been utilized. This allows a direct comparison to the resistive-loaded differential amplifier using the DG MOSFET, designed by Pakaree and Srivastava [14]. Comparative advantages and disadvantages of resistive-loaded and active-loaded differential amplifier topologies have been given in Table 1 [6, 8, 19, 26,27,28]. An active-loaded topology enables the resistors to be replaced by current sources for each differential pair transistor. Provided perfect matching by transistors used as current sources, the drain voltage of Q4 will match the drain voltage of Q3. The active-loaded topology converts the differential amplifier to a single-ended output.

3 Proposed design of active-loaded differential amplifier using DG MOSFET

As previously mentioned, in this research work, consideration has been made in designing the differential amplifier using the active-loaded topology. The BF998 DG MOSFET, having two gates, can be driven symmetrically (both gates have the same work function or, injected with the same signal) or independently (both gates have separate signals and biased separately) [30] as shown in Fig. 4. Gate 1 may be known as the front-gate, and gate-2 may be known was the back-gate.

If independently driven, it is recommended that gate-1 be injected with the RF (low frequency, low-voltage) signal and gate-2 biases the MOSFET accordingly or used as a Local Oscillator (LO) input. Further elaborating, gate-2 is utilized for biasing the MOSFET to produce the required drain current. All four transistors will share this characteristic in the proposed design.

The proposed differential amplifier would ideally consist of two main sections, the differential amplifier combined with a current mirror. The differential amplifier architecture chosen in Fig. 5, differs slightly from the “classical” one shown in Fig. 3(a) and (b), where a degenerative source resistance RS is added. From research conducted by Mandapathi et al. [5], this method delivers a superior gain, as opposed to the architecture shown in Fig. 3(a) and (b). Given the low-voltage constraints of the DG MOSFET, an increase in the gain can be favourable. The current mirror is shown in Fig. 5, using NMOS transistors M5 and M6.

Active-load differential amplifier topology with the addition of degenerative feedback resistance Rs and NMOS current mirror [5]

The current method proposed by Pakaree and Srivastava [14] implemented an asymmetrically-driven pair of DG MOSFETs. However, driving each MOSFET independently offers much more control given that gate-2 is responsible for the transconductance, threshold voltage and current characteristics. The output characteristics of the BF998 are shown in Fig. 6e, for a “typical value” of (gate 2-to source voltage) VG2-S of 4 V. In application, an increase or decrease in VG2, yields a larger or smaller transconductance, respectively. This can be seen in Fig. 6f, where VG2-S is changed to 2 V (the simulation of the device at this VG2-S was performed using the schematic shown in Fig. 6(d), showing a larger gradient in the linear region of the device. Thus, reducing VG2-S leads to a smaller voltage at saturation and a smaller drain current required. Hence, the differential amplifier designed in this work may be independently driven by examining this given advantage. In attempting to look for further biasing methods and techniques, it has proven challenging to find biasing methods that accommodate independently-driven DG MOSFETs.

a Proposed design of active-loaded differential amplifier using DG MOSFET. b Active-loaded Differential amplifier using DG MOSFET under small-signal conditions, c Half-circuit consisting of small-signal models of U2 and U4, d Test circuit to derive ID-VGS characteristics e Typical VGS characteristics from BF998 datasheet for VGS-2 = 4 V, and f Derived VGS characteristics for VG2-S = 2 V using the circuit in Fig. 6(d)

Figure 6a is a full circuit design of the proposed active-loaded differential amplifier using DG MOSFET. It's resultant half circuit to determine the differential gain is drawn in Fig. 6b–e. From Fig. 6a, transistors M1 and M2 form a Widlar current mirror with DG MOSFETs U3 and U4 while resembling an NMOS current source. This is an important note, as one of the secondary objectives was to normalize the amplifier design to NMOS transistors. Initial specifications of allowing a 1 Vpk – 1.2 Vpk output swing, an output current of the amplifier was simulated and achievable with an output current of 10 mA. A degenerated-resistive feedback topology was utilized in conjunction with the previously mentioned analogue circuitry for current sourcing. The addition of a source resistance at each source terminal of U1 and U2, as shown in Fig. 6a, which characterizes this topology, aids the amplifier in improving the gain at more significant differential voltage outputs.

The SPICE command.dc VD 0 12 1 VG -0.5 0.4 0.1 implies a DC sweep in LTSpice, where the voltage VD is swept from 0–12 V in 1 V increments, which will appear on the x-axis of the plot, and VG1 is swept from −0.5–0.4 V in 0.1 V increments and appear as multiple traced on the same plot. Also, SINE(1 100 m 10 k) implies a sine signal with a DC offset of 1 V, an amplitude of 100 mV, and a frequency of 10 kHz. For this design, the differential gain is:

where, ro4 and ro2 are design parameters (output resistance), inherently greater than R2, thus:

In Fig. 6e, the datasheet of the BF998 suggests a typical value of the gate-2 to source voltage VG2-S of 4 V. However, the proposed amplifier requires a value of 0 V for VG2-S for a drain current of 5 mA through each DG MOSFET. This is because gate-1 and the source are held at the same voltage, as shown in Fig. 6d. From inspection, the VG2-S can be found from the simulation of the output characteristics to be 2 V. This value biases the device in the saturation region [11]. In considering the connection of the bulk terminal, the MOSFET is biased in the saturation region, which entails the source and bulk terminals being connected, reducing the parasitic capacitances of the MOSFET [30]. In Fig. 6d the source terminal is connected to the ground; thus, VG1 in the legend can be equated to VG1-S.

A dual supply of ± 12 V (shown by Positive rail and Negative rail in Fig. 6a) has been chosen to allow for adequate output swing and current sourcing from the NMOS current mirror constructed from two 2N7000 transistors. While selecting an independently driven configuration for U1 and U2, 1 V offset is advisably maintained for biasing the DG MOSFET for the drain current of 5 mA, for each MOSFET.

4 Analysis and results

To grasp a basic understanding of how this differential amplifier performs in comparison to existing models, LTSpice simulations have been used to measure the differential gain (for different input voltages, for both inputs, allowing a broad range of differential outputs to be considered), common-mode gain (performed at various differential input voltages, common-mode input voltages, and frequencies), CMRR, and frequency response.

4.1 Differential gain

Considering this topology, the output is single-ended, therefore the output can be given as [27, 28]:

where, Vid+ and Vid- are the positive and negative differential voltage, respectively, and VO is the output voltage. Peak voltages of the inputs and outputs were considered in these calculations. In Fig. 7, Vin+ can be seen in yellow and Vin- in green. The output is 16 mVpk, thus the differential voltage gain will be 1.78 V/V. For the use of LTSpice, SINE (1 10 m 10 k) implies a sine signal with a DC offset of 1 V, an amplitude of 10 mV, and a frequency of 10 kHz. The other commands used at different outputs apply the same logic. Differential input voltages used for the designed amplifier 10 and 1 mV have been shown in Table 2.

Tables 3 and 4 indicate the output differential voltage and the differential gain, respectively. Values shown by Vcm denote that the input signal can be regarded as a common-mode signal at that point.

4.2 Common-mode gain analysis

The common-mode gain is the voltage gain for common-mode voltage components. The input signals of a differential amplifier usually have a voltage offset or common-mode voltage added for biasing purposes. A common-mode signal can also be defined as a signal common to both inputs of the differential amplifier. In interpreting the common-mode signal as a voltage offset, this allows the transistors used to be sufficiently turned on, despite a small differential voltage. In Fig. 8, inputs VG1 and VG2 have common-mode components denoted by VIcm.

Differential amplifier showing common-mode components and differential components [19]

However, the differential amplifier as an electronic tool is used to suppress common-mode signals, i.e., no gain should be applied to DC signal components. Amplification of common-mode signals imply noise has been coupled into the circuitry, limiting bandwidth and decreasing gain [29]. The common-mode gain has been analyzed for the DG MOSFET differential amplifier designed. The common-mode gain has been simulated for the differential signals listed as Vin+ in Tables 3 and 4. A maximum value of 84.65 μV has been measured. In Fig. 9a the sine signal has been passed with a common-mode component of 1 V and a differential component of 10 mV. The peak voltage of the output waveform of the differential amplifier is 84.62 μV.

An additional effect on the common-mode gain that must be considered entails increased frequency, as shown by Jorgovanovic et. al. [33]. Applying the common-mode signal used in Fig. 9(a) for a frequency of 1 kHz, the output can be observed in Fig. 9(b). The measured output signal has a peak of 87 μV. The common-mode gain for frequencies for 1–10 MHz is shown in Table 5. Alterations to frequency were made but preserved the DC and AC components i.e. 1 and 10 mV, respectively.

4.3 Frequency response analysis

From Sedra and Smith [19], an active-loaded differential amplifier has a single pole and zero, as shown in Fig. 10. The frequency response can be characterized by having one pole and one zero, where fp and fz have been characterized by the input miller capacitance Cm:

Referring to Fig. 10, Cgd1 is gate-to-drain capacitance for Q1, Cdb1 is drain-to-body capacitance for Q1, Cdb3 is drain-to-body capacitance for Q3, Cgs3 is gate-to-source for Q3, and Cgs4 is gate-to-source for Q4.

The value of the miller capacitance for the differential amplifier corresponds to the single-gate MOSFET in Fig. 10. Figure 11(a) is the frequency response for an active-loaded differential amplifier designed by Shilpa and Srilatha [4], which depicts a single pole. This amplifier uses the single-gate MOSFET. The bandwidth of this amplifier is approximately 5 MHz. Unlike the frequency response shown in Fig. 10, a zero has been excluded. This is possible as the dominant-pole compensation may have been achieved with the output resistance and capacitance [36, 37].

a Frequency response of differential amplifier using DG MOSFET [13]. b Test setup for deriving frequency response of the differential amplifier. c The frequency response of the proposed amplifier exhibits a bandwidth of 42 MHz and a mid-band gain of 11.25 dB

In evaluating the frequency response of a DG MOSFET-based differential amplifier, Pakaree and Srivastava [14] have designed a resistive-loaded differential amplifier using a DG MOSFET with a bandwidth of 32 MHz. In noting the expected frequency response for a differential amplifier in Fig. 11(a), the frequency response for the active-loaded differential amplifier designed in this literature can be seen in Fig. 11(c). In Fig. 11(b), the test setup for a typical frequency response can be observed. An AC signal of amplitude 1 V and phase 0° is injected into Vin+, where Vin- is injected with a phase shift of 180°. The phase shift provides a change in signal to provide a differential output. From Fig. 12(b-e), it has been noted that bandwidth is approximately 42 MHz with a mid-band gain of 11.25 dB. The proposed differential amplifier has one dominant pole, like the active-loaded differential amplifier designed in [5].

a Excerpt of Fig. 6(a) showing test setup to inject signals to derive differential gain for a signal of Vcm = − 8 V. b Distortion at differential voltages of 1 V and 0.5 V, respectively for an input common-mode voltage of -8 V. c Distortion at differential voltages of 10 and 1 mV respectively for an input common-mode voltage of − 8 V. d Distortion at differential voltages of 1 V and 0.5 V respectively for an input common-mode voltage of 7 V. e Distortion at differential voltages of 10 mV and 1 mV respectively for an input common-mode voltage of 7 V

4.4 Common-mode rejection ratio (CMRR) analysis

The CMRR allows designers and engineers to gauge the performance and efficiency of a differential amplifier directly. Texas Instruments [36] defines CMRR as a measure of a device's ability to reject signals common to both negative and positive inputs. In a resistive-loaded differential amplifier, as designed by Pakaree and Srivastava [14], a differential-ended output ideally has an infinite CMRR, and a single-ended output has a theoretically limited CMRR of gmRd, where gm is the transconductance of the transistor and Rd is the drain resistance. To derive the CMRR, for the proposed differential amplifier, requirements have been described in application notes [36] and other usable differential amplifiers such as the ADA4945-1 from analog devices [37].

The CMRR analysis may be conducted for specified common-mode inputs, which from the inspection are − 8 V and 7 V, over the frequency range of 1–100 MHz. Differential inputs for the differential amplifier will be specified as (Vin+ = 10 mV, Vin- = 1 mV) and (Vin+ = 1 V, Vin- = 500 mV). Testing results have been listed in Table 6. In practical design, the input common-mode range can be properly defined and verified. However, this test setup provides a preliminary insight into the differential amplifier and one is able to consider its CMRR over a range of frequencies and differential voltages. This process includes a defined common-input voltage range and these values may expose certain errors in circuital design. The simulation test setup can be shown in Fig. 12(a), where the common-mode voltage is noted as the first value in brackets, and the differential voltage is noted as the second value in brackets. The distorted outputs indicate the limits of the amplifier, as the ‘worst-case scenario’ that can be evaluated i.e. common-mode input voltage range of − 8 V < VIN (cm) < 7 V. The amplifier's differential gain was considered for computing the overall CMRR.

These values provide a preliminary overview of the limitations of the differential amplifier and most likely will be reduced when practically implemented but allows the designer to define a range of input DC voltages that should be allowable i.e. − 8 V < Vcm < 7 V.

The following comparisons may be adapted from Pakaree and Srivastava [14], comprising a resistive-loaded differential amplifier designed using a DG MOSFET. It is listed in Table 7.

5 Conclusions and future work

The design of an active-loaded differential amplifier has been carried out. Following the design procedure, it also continues to shed more light on the DG MOSFET, as it is a device of high performance for small signals in the higher RF spectrum. This transistor is interchangeable with any preferred N-channel MOSFET, as it merely provides adequate output current. The differential gain of the amplifier designed in this paper exhibits stability for a smaller differential output voltage, with a preferred, positive DC (direct current) offset/common-mode voltage applied. In designing this amplifier, 2 V/V was a specified design goal. However, it is possible to improve this value by utilizing greater gate control of the DG MOSFET. To achieve this, the use of active components, i.e., other transistors such as BJTs, may be employed to control the biasing of the gates used as current sources in the future.

The CMRR indicates an improvement is needed in the proposed design’s frequency response. This can be seen in the abrupt decrease in the CMRR for a frequency greater than 1 MHz. A possible solution for improving high-frequency response entails the use of common-mode feedback techniques and improving the performance of the current mirror included in the proposed design. A poor high-frequency response can also negatively affect the amplifier's output impedance, which would contribute to poor performance under load conditions.

In analyzing the results of the common-mode gain, one may observe a distinct increase in the common-mode gain for higher frequencies. However, the simulation's common-mode gain appears on a lower-μV scale, which can still be improved. A suggested improvement would allow for the use of a telescopic-cascode topology, which requires the use of more transistors but may also aid in improving overall gate control of the DG MOSFET at high frequencies. Deriving the frequency response, one can identify the gain of the flat-band of the differential amplifier of 11.25 dB, this response may be analyzed further and manipulated by moving the poles derived for a more favourable response. The bandwidth is of the highest importance and improves the resistive-loaded differential amplifier by 10 MHz. This allows the active-loaded topology to be better suited to high-frequency applications.

Availability of data and materials

All data and materials used to prepare this manuscript are available in this document.

References

Mack CA (2011) Fifty years of Moore’s law. IEEE Trans Semicond Manuf 24(2):202–207

Maduagwu UA, Srivastava VM (2019) Analytical performance of the threshold voltage and subthreshold swing of CSDG MOSFET. MDPI J Low Power Electr Appl 9(1):1–20

Alamo JAD, Antoniadis DA, Lin J, Wenjie L, Vardi A, Zhao X (2016) Nanometer-scale III-V MOSFETs. IEEE J Electr Dev Soc 4(5):205–214

Shilpa S, Srilatha J (2017) Design and analysis of high gain differential amplifier using various topologies. Int Res J Eng Technol 4(5):636–640

Mandapathi V, Nishanth P, Paily R (2011) Study of transistor mismatch in differential amplifier at 32nm CMOS technology. Int J Comp Sci 1(1):109–115

Johansson S, Berg M, Persson KM, Lind E (2012) A high-frequency transconductance method for characterization of high- κ border traps in III-V MOSFETs. IEEE Trans Electr Dev 60(2):776–781

Weis M, Emling R, Schmitt-Landsiedel D (2009) Circuit design with independent double-gate transistors. Adv Radio Sci 7:231–236

Cobianu O, Soffke O, Glesner M (2006) A Verilog-A model of an undoped symmetric dual-gate MOSFET. Adv Radio Sci 4:303–306

Arnub IBK, Ali MT (2018) Design and analysis of logic gates using GaN based double gate MOSFET (DG-MOS). Aiub J Sci Eng 17(1):1–13

Khumalo S, Srivastava VM (2022) Realization with fabrication of double-gate MOSFET based boost regulator. Mater Today: Proc 59(1):827–834

Taur Y, Liang X (2004) A continuous, analytic drain-current model for DG MOSFETs. IEEE Electron Dev Lett 25(2):107–109

Pillay S, Srivastava VM (2020) Realization with fabrication of double-gate MOSFET based class-AB amplifier. Int J Electr Electr Eng Telecommun 9(6):399–408

Crupi G, Schreurs DMMP, Caddemi A (2017) Effects of gate-length scaling on microwave MOSFET performance. MDPI Electr 6(3):1–10

Pakaree JE, Srivastava VM (2019) Realization with fabrication of double-gate MOSFET based differential amplifier. Microelectr J 91:70–83

Maduagwu UA, Srivastava VM (2020) Realization with fabrication parallel-gate MOSFET based differential amplifier. Int J Emerg Trends Eng Res 8(9):6599–6608

Discrete Semiconductors, BF998; BF998R Silicon N-channel dual-gate MOSFETs - Datasheet, Philips Semiconductor, 1996.

Medury AS, Bhat KN, Bhat N (2016) Impact of carrier quantum confinement on the short channel effects of double-gate silicon-on-insulator FINFETs. Microelectron J 55:143–151

Colinge JP (2004) Multiple-gate SOI MOSFETs. Solid-State Electron 48:897–905

Sedra AS, Smith KC (2014) Microelectronic circuits: Theory and applications, 7th Ed., Oxford University Press, USA

Srivastava VM, Singh G (2014) MOSFET technologies for double-pole four-throw radio-frequency switch, Springer International Publishing Switzerland

Sharma RK, Dimitriadis CA, Bucher M (2016) A comprehensive analysis of nanoscale single- and multi-gate MOSFETs. Microelectr J 52:66–72

Cuautle ET, Avina PRC, Guerra RT, Gomez VHC (2019) Design of a wide-band voltage-controlled ring oscillator implemented in 180 nm CMOS technology. MDPI Electr 8(10):3–17

Lee M, Cho S, Lee N, Kim J (2020) New radiation-hardened design of a CMOS instrumentation amplifier and its tolerant characteristic analysis. MDPI Electronics 9(3):1–12

Maduagwu UA, Srivastava VM (2020) Channel length scaling pattern for cylindrical surrounding double-gate (CSDG) MOSFET. IEEE Access 8:121204–121210

Tian Y, Lanni L, Rusu A, Zetterling CM (2016) Silicon Carbide fully differential amplifier characterized up to 500 °C. IEEE Trans Electron Devices 63(6):2242–2247

Gayakwad R (2000) Op-amps and linear integrated circuits, 4th edn. Pearson, USA

Bell, DA (2007) Operational amplifiers and linear ICs, 2nd Ed., Oxford University Press, UK

Fiore JM (2002) Operational amplifiers and linear integrated circuits: Theory and application, Jaico Publishing House

Yilmazer U, Yilmazer C, TokerA (2015) Design and comparison of high bandwidth limiting amplifier topologies. In: 9th International Conference on Electrical and Electronics Engineering, Turkey pp. 66–70

KimJerry K, Fossum G (2001) Double-gate CMOS: Symmetrical- versus asymmetrical-gate devices. IEEE Trans Electron Devices 48(2):294–299

Bha JKK, Priya PA (2019) Low power and high gain differential amplifier using 16 nm FinFET. Microprocess Microsyst 71:1–6

Dessouky M, Kaiser A (2000) Very low-voltage fully differential amplifier for switched-capacitor applications, IEEE International Symposium on Circuits and Systems, Switzerland, pp. 441–444

Jorgovanovic N, Bojanic D, Ilic V, Stanisic D (2009) An improved AC-amplifier for electrophysiology. J Autom Control 19:7–12

Lundberg KH (2004) Internal and external op-amp compensation: a control-centric tutorial. In: American Control Conference, USA, pp. 5197–5211

Ho M, Guo J, Mak KH, Goh WL, Bu S, Zheng Y, Tang X, Leung KN (2016) A CMOS low-dropout regulator with dominant-pole substitution. IEEE Trans Power Electron 31(9):6362–6371

Simmons P (2019) 3.4 TI precision labs - current sense amplifiers: common-mode rejection ratio, Texas Instruments, Available: https://training.ti.com/sites/default/files/docs/current-sense-amplifiers-common-mode-rejection-ratio-presentation-quiz.pdf, Accessed: 21 March 2022

High speed (2019) ±0.1 μV/˚C offset drift, fully differential ADC driver (ADA4945–1) datasheet, Analog Devices, Available: https://www.analog.com/media/en/technical-documentation/data-sheets/ADA4945-1.pdf, Accessed 27 March 2022

Acknowledgements

Authors are thankful to Mr. Logan Pillay, Chairperson of TESP, Mr. Cecil Ramonotsi, CEO, Eskom Development Foundation, South Africa and Mr. Tshidi Ramaboa, Eskom Academy of Learning, Human Resources, Midrand. The authors are also thankful to Ms. Leena Rajpal, Public Relations Officer, University of KwaZulu-Natal, Durban, South Africa, for providing various support to carry on this research work.

Funding

This research work is funded by the Electricity Supply Commission (Eskom), South Africa, dated 31 Jan. 2020, under the Tertiary Education Support Programme (TESP).

Author information

Authors and Affiliations

Contributions

Suvashan Pillay (SP) and Viranjay M. Srivastava (VMS) conducted this research; SP has designed and analyzed the model with data and wrote this article; VMS has verified the result with the designed model; all authors had approved the final version.

Corresponding author

Ethics declarations

Competing Interests

The authors have no relevant financial or non-financial interests to disclose.

Research involving Human Participants and/or Animals

Not applicable.

Informed consent

Not applicable.

Ethics approval

Not applicable.

Consent to participate

Not applicable.

Consent for publication

Not applicable.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Pillay, S., Srivastava, V.M. Design and comparative analysis of active-loaded differential amplifier using double-gate MOSFET. SN Appl. Sci. 4, 202 (2022). https://doi.org/10.1007/s42452-022-05100-1

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s42452-022-05100-1