Abstract

The emerging 5G internet-of-things applications in home automation, smart wearables, healthcare monitoring, automotive sensors require low-cost, area efficient, high-performance and low power radio frequency blocks for effective short-range communication. This growing market demand is addressed in this paper by proposing a fully CMOS RF down-converter (RFDC) network for 5G applications. This work aims to achieve high linearity, low noise figure and high gain simultaneously by optimally splitting the performance between the three stages of the RFDC. The proposed down-conversion system is designed in UMC 180 nm CMOS process technology and the post-layout simulations on layout extracted parameters with Cadence SpectreRF shows an IIP3 of − 3.43 dBm, an IIP2 of 78.13 dBm, double-sideband noise figure of 12.76 dB, a conversion gain of 23.69 dB, the spurious-free dynamic range of 71.7 dB, and the phase noise of − 91.39 dBc/Hz at an offset of 5 MHz. The proposed frequency translation circuit occupies a core area of only 0.0043 mm2 and consumes a low power of 12.6 mW from a 1.8 V supply.

Similar content being viewed by others

1 Introduction

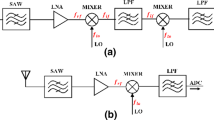

The evolution of telecommunication technologies is unprecedented in recent history with the advent of Internet-of-Things (IoT). The IoT applications are based on the standards framed by IEEE for low-rate wireless personal area networks (LR-WPAN) [1, 2] to operate in the 868/915 MHz band and the 2.4 GHz band. The specifications of IEEE for LR-WPAN explicitly necessitate a low-cost communication system to operate in the frequency band of interest. Hence, the direct-conversion receiver architecture is again gaining prominence over the heterodyne architecture because of the simple, low-cost, direct down-conversion mechanism. Also, the growing technology trends of miniaturization can be aided by the direct-conversion architectures. The wireless sensor networks (WSN) in the short-range communication environment can be micro-managed by a more extensive network or networks such as the Metropolitan Area Network (MAN) and Wide Area Network (WAN). The interaction between the 5G networks should have good quality-of-service (QoS) for reliable wireless communication. However, the QoS of the short-range communication environment in the 2.4 GHz ISM band is hindered by the adverse nonlinearities in the continually brimming network.

Although the direct-conversion systems have benefits in complex silicon integration, these systems have limiting factors due to the second-order and the third-order nonlinearities [3,4,5]. The use of the 2.4 GHz ISM band by multiple users/applications create additional unwanted tones at the input of any 2.4 GHz wireless receiver. For the direct-conversion receivers employing CMOS devices in this day and age, the inevitable nonlinear V–I conversion of the multi-tone input signal by the Metal–Oxide–Semiconductor (MOS) devices create harmonic distortion (HD) and intermodulation distortion (IMD). These nonlinearities are characterized by the second-order intercept point (IP2) and the third-order intercept point (IP3). The direct-conversion wireless systems must have a very high input-referred second-order intercept point (IIP2) [6, 7]. In an ideal, balanced differential system, IIP2 is infinite. However, due to device mismatches and other second-order mechanisms [8,9,10], the IIP2 is no longer infinite but tends to a finite value. The input-referred third-order intercept point (IIP3) determines the dynamic range of the entire wireless receiver, and hence, a higher value of IIP3 is advantageous for distortionless operation and thereby to provide suitable QoS.

The need for high linearity in the direct-conversion system places a trade-off on the conversion gain and the noise figure. The linearity of the last stage in the RF chain largely determines the linearity of the entire system [9]. The RF down-converter is required to facilitate the dynamic range improvement of the wireless system, while substantial contribution to the overall gain and noise figure by the mixer stage is an added benefit to the entire wireless system. Along with the direct-conversion architecture, further cost reduction can be achieved by reducing the area hungry passive devices. Thus, novel circuit techniques employing only MOS devices can further boost the realization of the low-cost requirements of the IEEE 802.15.4 standard. However, the MOS devices limit the noise performance of the circuit due to their inherent flicker noise. Therefore, for satisfying the low-cost specifications of the LR-WPAN standard, the emerging short-range communication systems must be implemented with circuits providing proper gain, noise figure and linearity performance while exploiting minimum silicon chip area.

To achieve the linearity requirements of the LR-WPAN direct-conversion systems using CS input stages, the first-order transconductance (\( g_{m}^{1} \)) must be increased, or the third-order transconductance (\( g_{m}^{3} \)) must be reduced or nullified. Some of the common-source based RF down-converters are reported in [11,12,13,14,15,16,17]. In [11], 3.1–10.6 GHz RFDC is reported with 22.5 dB gain and − 11 dBm IIP3. In [12], slightly lesser gain but improved linearity performance is reported with a power consumption of 24.5 mW. In [13], 5.8–13 GHz RF front-end for software-defined radio (SDR) is proposed with 25.6 dB gain, 2.6–5.1 dBm IIP3 by making use of the area hungry passive inductors. A digitally controlled RF front-end is recently reported in [15] with 24 dB gain and − 44 dBm IIP3. Alternatively, the direct-conversion systems can be implemented with a trans-impedance amplifier (TIA) input stage to reduce the effect of nonlinear V-I conversion. Some of the common gate (CG) based down-conversion circuits are reported in [18, 19]. In [18], a CG based input transconductance stage is used in the RFDC yielding 15.5 dB gain, 6.2 dB NF and 1-dB compression point at − 12 dBm. In [19], linearity is compromised to yield a high gain of 38.4 dB and a noise figure of 16.7 dB. The high conversion gains reported in [11, 13, 15, 19] will prove fruitful for reducing the overall noise figure of the wireless system and also helps to reduce the number of gain stages required in the receiver chain. High IIP3 provides a higher dynamic range for distortionless operation of the wireless system. The trade-off sacrifices at least one of the performance parameters to gain the other in [11,12,13,14,15,16,17,18,19] while consuming large die area. However, modern deep sub-micron silicon process further complicates the gain and linearity trade-off in RF circuits. Hence, a new circuit design methodology is required to have a high conversion gain, low NF and high IIP3 simultaneously when operating in dense environments such as the 2.4 GHz ISM band.

The current technology trend of miniaturized communication devices places stringent goals of providing high-performance in the lowest silicon area possible. The circuits reported in the literature establish the challenge of providing the highest performance in the smallest chip area possible. This paper aims to give a solution to the challenge of designing and implementing high linear, low noise and high gain RF down-converter network for IEEE 802.15.4 LR-WPAN application. Also, the reported works concentrate on techniques to improve any one of the parameters while this proposed work aims to achieve high gain, low noise figure and high gain simultaneously by optimally splitting the circuit performance between the different stages of the RF down-converter. The proposed methodology is shown in Fig. 1. The switching stage is controlled by a novel 2-stage ring voltage-controlled oscillator (VCO) with a control input to switch ON/OFF the oscillations when required.

To aid in the frequency conversion, the LO signal is needed along with the frequency translation circuit. Some of the mixer and VCO co-designs are reported in [20,21,22]. The VCOs are realized using LC tank circuits. The phase noise reported for an offset of 1 MHz are 116.2 dBc/Hz in [20], 116.7 dBc/Hz in [21] and 116.8 dBc/Hz in [22]. The LC tank circuit consumes large silicon area, and hence, the low-cost solution for the IEEE 802.15.4 standard is unachievable. For low-cost minimum silicon area consumption, ring based VCO topology is preferred. However, the ring VCO topology suffers from poor spectral purity when compared to LC-tank based oscillators and thus, presents a new challenge of designing ring based VCO with phase noise performance meeting the specifications of IEEE 802.15.4 standard. The reported mixer and VCO networks [20,21,22] also suffer from poor gain and linearity characteristics along with large silicon area consumption. The specifications for the wireless system performance as per IEEE 802.15.4 is listed in Table 1 based on data from [1] and [2].

The equations for gain, noise figure and linearity are derived and examined for trade-offs to suitably design the RF down-converter. The design, parasitic modelling, layout, and post-layout simulation of the RFDC and VCO network for the 2.4 GHz system is carried out in UMC 180 nm CMOS technology using Cadence SpectreRF tool. The process, voltage, temperature (PVT) variation analysis, corner analysis and mismatch analysis for various performance parameters is carried out to establish the reliability of the proposed network for reliable wireless industrial communications. The design of the RFDC network is presented in the Sect. 2. Design optimization and trade-offs between conversion gain, noise figure and linearity are discussed in the Sect. 3 with equations for linearity and NF. The performance analysis of the mixer and VCO is characterized in the Sect. 4 and the Sect. 5 concludes the proposed work.

2 Proposed frequency conversion circuit

2.1 Mixer

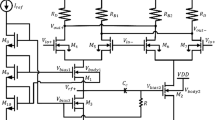

The schematic diagram of the conventional mixer and the proposed 3-stage RFDC are shown in Fig. 1a, b respectively. The input stage of the conventional mixer senses the input voltage, and the proposed 3-stage frequency conversion circuit senses the input current instead of the input voltage. In conventional mixing stage, the input matching is not easily achieved whereas, in proposed RFDC, the input resistance can be set to \( 1/{\text{g}}_{\text{m}} \) of the input transistor. Also, in conventional mixers, the load is passive while in the proposed RFDC, the load is replaced by another gain stage. Thus enabling the proposed RFDC to provide better gain and reduced NF. The proposed 3-stage frequency converter circuit is shown in Fig. 2. The corresponding equivalent circuit is given in Fig. 3. The input RF signal is sensed at the source of the NMOS CG devices \( T_{1} \) and T2. \( V_{b} \) is the gate voltage for the common-gate transistors. The transistors \( MT_{1} \) and \( MT_{2} \) provide the necessary bias at the source of transistors \( T_{1} \) and \( T_{2} \). \( V_{cs} \) provides the necessary bias voltage for the transistors \( MT_{1} \) and \( MT_{2} \). The RF input is processed by the TIA stage, and the output from the drain of the TIA transistors is fed to the mixing stage (switching stage). The use of PMOS transistors in the switching stage helps in keeping the flicker noise contribution of the MOS devices to a minimum. The equation for flicker noise is modelled in [23] and [24] as

where \( K_{f} \) and \( \alpha f \) are process dependent, Cox is the gate-oxide capacitance, f is the frequency, WxL is the area of the MOS device. Since PMOS devices have lower mobility than the NMOS devices, the flicker noise contribution is minimized. Depending upon the polarity of the local oscillator (LO) signal \( V_{lo} \), one of the switching transistors provide the signal path from the TIA stage to the gain boosting stage. The mixing stage is a double-balanced stage, and the output of the mixing stage is the input to the final stage for gain boosting. Although the LO signal is a large signal for effective switching function, the transistors \( T_{3 - 6} \) provide a time-varying resistive path from current sensing stage to the gain boosting stage. This resistive path is modelled as \( r_{03,4,5,6} \) for numerical analysis. The PMOS transistors \( T_{7} \) and T8 sense the signal from the switching stage and the intermediate frequency (IF) output signal (Vif) is available at the drain of the PMOS transistors. The necessary potential for the drain of PMOS transistors is provided by the NMOS load transistors MT3 and MT4. Vtail is the gate bias for the transistors MT3 and MT4. The proposed 3-stage frequency converter circuit is analysed for conversion gain calculations as follows. The gain equations are derived as a function of the equivalent RF voltage (Vrf) sensed at the source node of the input current sensing transistors. The analysis follows the methodology reported in [11, 16, 25]. The RF signal voltage (Vrf) with amplitude (Arf) and frequency (ωrf) in radians can be expressed as

moreover, the local oscillator signal (Vlo) with amplitude (Alo) and frequency in radians (ωlo) generated by the VCO expressed as

then the down-converted IF signal (Vif) is derived based on [25, 26] as

The IF signal in (4) can be simplified as

where \( G_{O} \) is the gain factor, and ωif is the frequency of the IF signal in radians and is expressed as

The (\( {\raise0.7ex\hbox{$1$} \!\mathord{\left/ {\vphantom {1 \pi }}\right.\kern-0pt} \!\lower0.7ex\hbox{$\pi $}} \)) term comes from the first harmonic of the Fourier expansion of the LO signal applied to the mixer. Thus, from (5), the conversion gain (Gc) for a double-balanced mixer is expressed as

The gain factor (GO) can be calculated from the equivalent circuit in Fig. 3 as follows. Since, the first stage seen by the input RF signal is a TIA stage, the gain from the input (Vrf) to the node Vx can be derived as

where, gm1,2 is the transconductance of the input transistor T1.2, ro1,2 is the output resistance of the input transistor T1.2 and roI1,I2 is the output resistance of the PMOS current source I1.2.

The switching transistors (T3-6) provide the signal path from node Vx to node Vy depending on the polarity of the LO signal. At any given point in time, only one transistor is switched ON by the LO signal, and the ON transistor acts as a resistive path between the two nodes, Vx and Vy. The gain from node Vx to node Vy is almost equal to 1 and can be easily derived from the voltage divider shown in Fig. 4.

The ON resistance of the switching transistors T3-6 is modelled as r03,4,5,6. At the node Vy, the signal encounters the poly-silicon gate of the gain boosting transistors T7,8. Hence, the signal path is modelled with a large resistance of rlarge to include the very high resistance of the polysilicon layer and the gate oxide (SiO2) layer. By applying voltage division at Vy, we have

From (10), it can be seen that almost all of the signal at node Vx is available at the input node of the gain boosting transistors, Vy after frequency conversion by the switching transistors. The frequency conversion is represented as a function of the LO signal, \( f\left[ {v_{lo} } \right] \). The PMOS transistors T7 and T8 offer differential common-source amplification to the frequency-converted IF signal, and the amplified output IF signal is available at the drain of the PMOS transistors. The output resistance of the switching transistor is a nonlinear function of the LO signal [24, 25]. Thus, the RF signal is modulated by the LO signal and hence, the gain offered by the circuit is dependent on the LO signal. The gain of the signal from Vy to Vif can be derived from the equivalent circuit in Fig. 3 as

where,gm7,8 is the transconductance of the PMOS transistor T7,8, ro7,8 is the output resistance of the PMOS transistor T7,8 and \( r_{oMT3,4} \) is the output resistance of the NMOS load transistors MT3,4.

From (8), (10), and (11), the overall gain from the input (Vrf) to the output (Vif) can be expressed as

Thus, by substituting the value of GO from (13) in (7), the conversion gain for the proposed mixer circuit can be expressed as

The above Eq. (14) provides insights into the optimization of the circuit about conversion gain, noise figure, and linearity. In (14), the transconductance of the input transistors in the TIA stage (gm1,2) is optimized for the impedance matching, linearity and noise figure and the transconductance of the gain boosting CS stage transistors (gm7,8) is optimized for gain. The linearity analysis, optimizations and, trade-offs are discussed in the Sect. 3.

2.2 Voltage controlled oscillator (VCO)

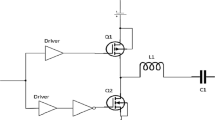

Ring VCO is preferred over LC tank based VCO because the latter’s silicon consumption in the chip affects the low-cost metric necessary for the IEEE 802.15.4 LR-WPAN standards. In the proposed work, the ring oscillator (RO) is designed with only two delay stages and a NAND gate for controlling the oscillation based on (\( \overline{EN} \)) signal for low power operation. Some of the ROs implemented with an even number of stages are reported in [27, 28]. The proposed 2-stage ring VCO with enable input (\( \overline{EN} \)) is shown in Fig. 5. The \( \overline{EN} \) signal helps to shut down the VCO circuit when necessary to minimize the power consumption. This arrangement helps in saving battery life of the devices in LR-WPAN wireless applications. Each stage of the VCO is a current starved inverter made up of PMOS transistors M1,3 and NMOS transistors M2.4. The transistors B1 and B2 act as tail current sources to stage-I and stage-II respectively. When \( \overline{EN} \) goes logic high, the signal in the feedback path (f/b) is inverted and produced at the output of the NAND gate. The inverter stages provide further polarity reversal, and the cycle continues. When \( \overline{EN} \) goes logic low, and if the signal in the feedback path is logic high, then no polarity reversal takes place in the feedback path. Hence, the oscillation ceases. Thus, by using enable input, the power consumption of the VCO can be reduced. Table 2 shows the truth table for the VCO with enable input. S1 and S2 are the input nodes to stage I and stage II respectively. The transient response of the 2-stage ring oscillator is shown in Fig. 6. The LO signal swings between VDD and Gnd resulting in a peak-to-peak swing of 1.8Vpp. The VCO is designed to operate at near rail-to-rail swing from a 1.8-V power supply. The rail to rail swing favours hard switching of the mixer stage and also in reducing the noise contribution of the switching transistors.

The frequency of oscillation is calculated in [29, 30] and can be simplified as

where, Ibias is the bias current through the delay stage of the VCO, Vsw is the voltage at the load, Cin is the capacitance at the gate of the delay stage, and N is the number of delay stages.

For rail-to-rail swing, the delay stages are biased at (\( {\raise0.7ex\hbox{${Vdd}$} \!\mathord{\left/ {\vphantom {{Vdd} 2}}\right.\kern-0pt} \!\lower0.7ex\hbox{$2$}}) \). Hence, the gate capacitance can be simplified as

where, WL is the area of the MOS device, and The gate-oxide capacitance is given as

where ɛox is the permittivity and tox is the thickness of the SiO2 layer respectively.

Since the load to any inverter delay stage in Fig. 5 is another delay stage, Vsw is equal to Vgs. Also, rewriting the bias current of the delay stage (Ibias) as the product of transconductance (gm) and the gate to source voltage (Vgs), (15) can be represented as

The transconductance (gm) in (18) can be rewritten as a function of the bias current (Ibias) as

The frequency of oscillation is verified by performing a 512-point Fourier Transform (FT) on the transient signal, and the magnitude spectrum of the LO signal is plotted in Fig. 7. Thus, from (19), by controlling the Ibias, the frequency of oscillation can be varied. The two bias voltages Vb1 and Vb2, for the tail transistors B1 and B2, aids in controlling the bias current and thereby, the frequency of oscillation (f).

The phase noise (PN) power contribution of the ring VCO is the sum of PN power contributed by the delay stages \( i\widehat{{_{n,delay}^{2} }} \) and the phase noise power of the NAND gate \( i\widehat{{_{n,NAND}^{2} }} \). The total PN power can be given as

where,

In (21) and (22), the noise power of transistors \( M_{1} \), \( M_{3} \), \( B_{1} \) and B2 are represented as \( i\widehat{{_{M1}^{2} }} \), \( i\widehat{{_{M3}^{2} }} \), \( i\widehat{{_{B1}^{2} }} \) and \( i\widehat{{_{B2}^{2} }} \) respectively. Similarly, the noise power of transistors in the NAND gate \( A_{1} \), \( A_{3} \), and \( A_{4} \) are represented as \( i\widehat{{_{A1}^{2} }} \), \( i\widehat{{_{A3}^{2} }} \) and \( i\widehat{{_{A4}^{2} }} \) respectively. It should be noted that the noise contribution of transistors \( M_{2} \), \( M_{4} \) and \( A_{2} \) are neglected since these transistors are cascode transistors in the 2-stage ring VCO of Fig. 5 and they do not contribute to the output noise.

3 Design and optimization trade-offs between conversion gain, noise figure, and linearity

From (14), we can see that the conversion gain of the mixer circuit depends on the transconductance of the input transistors (\( g_{m1,2} \)) and the transconductance of the gain boosting devices (\( g_{m7,8} \)). The input stage senses the input signal current directly and hence the effect of nonlinearity is subdued. The gain boosting stage differential pair (\( T_{7,8} \)) is the primary source of nonlinearity in the proposed mixer since the gain boosting stage senses voltage at the gate and produces an equivalent current at the drain by virtue of the nonlinear transconductance effect. When the PMOS and NMOS devices operate in the saturation region, the inherent nonlinearity is evident from the \( I_{D} \) versus \( V_{Ds} \) characteristics. By expanding the output drain current (\( i_{out} \)) of the MOS devices as a function of the input gate to source voltage (\( v_{in} \)) in Taylor series, we get,

where,

Equation (24) gives the nth-order derivative of the output drain current as a function of the input gate to source voltage. In RF systems, the first three terms of (23) are the elementary sources of nonlinearity, and hence, the analysis is restricted to the first three terms. For an input signal (\( v_{in} \)) expressed as

The nonlinear relation in (23) yields frequency components at ωin, 2ωin, 3ωin. The frequency components at 2ωin and 3ωin are filtered out as they occur outside the required frequency band in RF applications. However, since the 2.4 GHz band is shared by multiple users/applications such as Wi-Fi, WiMax, Bluetooth, MobileFi, LTE, more than a single tone may be present at the input of the down-conversion system. This multi-tone input signal having frequency components, for example, ω1 and ω2, are closely spaced with each other and can be expressed as

Equation (26) produces the in-band frequency components when substituted and expanded in (23). The expansion of (23) for multi-tone input in (26) is analysed in [26], and the derivation shows second-order intermodulation (IM) products at \( \omega_{1} \pm \omega_{2} \), and the third-order intermodulation products at \( 2\omega_{1} \pm \omega_{2} \) and \( 2\omega_{2} \pm \omega_{1} \). These in-band frequency components are hard to be filtered, and hence, they are the primary sources of nonlinearity in the RF systems. The IM products \( \omega_{1} - \omega_{2} \), \( 2\omega_{1} - \omega_{2} \) and \( 2\omega_{2} - \omega_{1} \) are of particular interest as they are spaced close to the fundamental components ω1 and ω2. Any nth order IM product grows n-times faster than the fundamental and causes the system to compress the desired signal, resulting in distortion. The IP2 and IP3 can be defined as

where, \( g_{m}^{n} \) is the nth order transconductance of the operating device. From (27) and (28), increasing the first-order transconductance \( g_{m}^{1} \) will increase both the intercept points. The increase in \( g_{m}^{1} \) is not straightforward since this increases the bias current. Alternatively, \( g_{m}^{2} \) and \( g_{m}^{3} \) can be reduced or nullified to increase IP2 and IP3 respectively. Another alternative is to bypass the transconductance effect by sensing the currents directly at the input and processing it further, and this approach is followed in this proposed work. The proposed mixer is a cascade of current sensing, switching and gain boosting stages. Hence, the overall IP3 must include the transconductance of the current sensing stage, transconductance of the gain boosting stage and the gain of the current sensing stage. Therefore, following the analysis based on [23,24,25,26], the IP2 and the IP3 points are derived following extensive calculations as the following:

In (29) and (30), \( S_{0} \) is the feedback factor in the gain boosting stage, \( g_{m,CS} \) is the first-order transconductance of the gain boosting CS stage, \( g_{m,CS}^{\prime } \) and \( g_{m,CS}^{\prime \prime } \) are the second- and third-order derivative of the transconductance of the CS stage respectively. \( G_{m,CG}^{n} \) is the nth-order effective transconductance of the current sensing stage, \( A_{v,CG} \) is the gain of the current sensing stage. The equations are derived based on the schematic of Fig. 2. From (14), (29) and (30), the design trade-offs between linearity and gain can be analysed. The linearity is inversely proportional to the gain of the current sensing stage and the LO signal. However, the overall nonlinear transconductance effect on the signal is minimized, resulting in high IP2 and IP3 values elaborated in the Sect. 4. To find the trade-off between linearity and noise figure, the overall NF has to be derived. The overall NF is contributed by the input current sensing stage, the switching stage, and the gain boosting stage. The noise factor of the input stage is simplified in [31] and is given as

In (31), γ and α, are technology-dependent, and since the transconductance (\( g_{m} ) \) of the input stage transistor is designed to be equal to (\( 1/R_{s} \)) for input matching, the noise factor of the input stage from (31) is found to be constant for a particular process. Fixing the \( g_{m} \) of the input CG stage for providing proper input matching creates a bottle-neck for improving gain. Hence, the gain of the overall down-converter circuit is concentrated in the CS gain boosting stage. The feedback path offered by the gate to drain capacitance (\( C_{gd} \)) to IM products is grounded since the gate is an AC ground in the current sensing stage. This also makes the input stage more linear than the gain boosting stage. Thus, the input current sensing stage concentrates on linearity and matching while gain boosting stage provides the necessary amplification for the RF signal. The gain boosting stage biasing is appropriately chosen to keep the third-order transconductance \( g_{m}^{3} \) to a minimum. Thus, the gain boosting stage of the 3-stage mixer is optimized for both gain and linearity enhancement of the down-conversion system.

Noise contribution of the down-converter circuit is mainly due to the mixing action of the switching transistors. The noise contribution to the output of a double-balanced mixer is generalized in [26] as

In (32), \( k \) is the Boltzmann constant, \( T \) is the temperature in Kelvin, \( R_{L} \) is the load resistance, \( \gamma \) is a process dependent factor, \( A_{lo} \) is the amplitude of the LO signal, and I is the bias current. Since the Alo is inversely proportional to the output noise, increasing the LO signal amplitude is advantageous for reducing the noise contribution of the mixer. Finally, the noise contribution of the CS stage is calculated as follows.

In (33), the noise contribution of transistors \( T_{7} \), \( T_{8} \), \( MT_{3} \) and \( MT_{4} \) are represented by their noise power as \( i\widehat{{_{T7}^{2} }} \), \( i\widehat{{_{T8}^{2} }},\; i\widehat{{_{MT3}^{2} }} \) and \( i\widehat{{_{MT4}^{2} }} \) respectively. If \( i\widehat{{_{T7}^{2} }} \) = \( i\widehat{{_{T8}^{2} }} \) = \( i\widehat{{_{T}^{2} }} \) and \( i\widehat{{_{MT3}^{2} }} \) = \( i\widehat{{_{MT4}^{2} }} \) = \( i\widehat{{_{MT}^{2} }} \), then (33) can be reduced as

where,

Thus, from (31), (32) and (34), the overall noise contribution of the RF down-converter can be expressed as

The above Eq. (37) shows the NF dependence on the LO signal, the gain of the current sensing stage and gain boosting stage. Also, from (29) and (30), the LO signal is inversely proportional to linearity. Hence, in the proposed mixer and VCO network, the VCO is designed to operate from rail-to-rail as mentioned earlier in the Sect. 2. By Friis’ equation [26], the noise factor of the mixer stage is reduced by the gain of the preceding Low-Noise Amplifier (LNA) and thus, relaxing the noise performance requirement of the mixer. In this work, the noise contribution due to the flicker noise of the MOS transistors is minimized by employing PMOS switching devices for mixing action instead of NMOS devices. Since the output of the mixing stage encounters a very high resistance in the form of polysilicon gate of the gain boosting stage, the current through the mixing transistors (\( T_{3 - 6} \)) is drastically reduced aiding in the reduction of the flicker noise contribution modelled in (1). Furthermore, the input stage has an optimized noise performance for a specific process. In this work, the NF is optimized by gain of the gain boosting stage transistors \( T_{7,8} \) and the LO signal. Linearity is optimized by the gain of the input stage transistor \( T_{1,2} \).

Thus, the trade-offs between the gain, linearity and noise figure are divided optimally between the three stages of the mixer. The input stage is optimized for matching and linearity and has a process dependent noise performance. The mixing stage is optimized for noise performance since the mixing stage is the major contributor to noise in the wireless system. Finally, the output stage concentrates on gain improvement and the overall reduction of noise figure along with keeping the growth of third-order tones to a minimum for presenting high dynamic range to the wireless system.

4 Results and discussion

The physical layout of the designed RF down-conversion network is shown in Fig. 8. For calculating the area, the measurement was taken 2λ away from the four sides of the core area. The total silicon area after integrating the RF down-conversion system and including the additional space between the two cores is scaled as 53.75 µm × 80.36 µm. The total layout area of the chip including power rails is 87.35 µm × 114.36 µm. For post-layout validation of the RFDC, BSIM3 models from UMC is used. The wire parasitic from the device terminal to the probe pads is modelled with an inductance, L_wire, of 1nH. The pad capacitance is modelled with a capacitor, C_pad, of 50fF. The model of the test bench with parasitic components is shown in Fig. 9. In reality, the bond-wire inductance and pad capacitance values will be smaller than the values used for modelling in this work. These values are referred from [24]. The bond-wire parasitic modelling helps to compare and calibrate the simulation measurements with the measurements after chip fabrication. This test setup ensures the reliable operation of the circuit after fabrication. The LO signal generated by the VCO swings near rail-to-rail from a 1.8-V power supply. The 1.8 \( V_{pp} \) is equivalent to a power level of 9 dBm. The VCO is tuned to 2.4 GHz by the two bias voltages \( V_{b1} \) and \( V_{b2} \). The required frequency range for IEEE 802.15.4 application is from 2.4 to 2.485 GHz.

The bond-wire parasitic is modelled with an inductor of 1nH. Cadence SpectreRF suite is used for RF simulation and measurement of layout extracted parameters (post-layout simulation). Figure 10 shows the variation of conversion gain in the frequency band of interest with and without bond-wire parasitic. It can be seen that without bond-wire parasitic, the conversion gain is 23.79 dB and with bond-wire parasitic, the conversion gain is 23.69 dB with a reduction of only 0.1 dB. The double-sideband noise figure (DSB-NF) is measured against the frequency and is shown in Fig. 11. From Fig. 11, the variation between measurements without bond-wire parasitic and with bond-wire parasitic is found to be very close. From (14) and (37), the dependence of gain and NF on the LO signal power is characterized, and the variation is plotted in Fig. 12.

The nonlinearity is characterized by the 1 dB compression point, IP2 and IP3 points in Figs. 13, 14 and 15 respectively using a two-tone test. The designed RF circuit has a 1 dB compression point at − 12.5 dBm. The IIP2 and the IIP3 point with bond-wire parasitic are 78.13 dBm and − 3.43 dBm respectively. The high IIP2 value of 78.13 dBm transcribes into a corresponding IMR2 of 163.13dB as per the relation in [10]. The linearity performance of the frequency translation circuit is a helpful tool to characterize the spurious-free dynamic range (SFDR) of the entire wireless system. If \( P_{noise} \) (dBm) is the minimum input noise power level to the circuit, then SFDR can be expressed by definition in [26] as follows:

In (38), \( P_{noise} \) is the noise floor of a noiseless receiver with a value of − 111 dBm \( \left( { - 174dBm + 10\log BW} \right) \). Thus, by (38) the proposed down-conversion network provides a very high dynamic range of 71.7 dB. The achieved SFDR is higher than the recently proposed down-converters in [15, 16, 18, 19]. The phase noise performance of the 2-stage RO is presented in Fig. 16. The designed RO has a phase noise of − 91.39 dBc/Hz at an offset of 5 MHz. The 5 MHz offset is chosen because the channel spacing is 5 MHz for IEEE 802.15.4 applications. The phase noise performance of the designed oscillator at an offset of 100 MHz is − 125.4 dBc/Hz. For IEEE 802.15.4 systems, the required phase noise performance is − 73.5 dBc/Hz at 5 MHz offset [2]. The designed RO lacks the spectral purity of LC-based oscillators but still provides excellent phase noise performance required in low area of only 137 µm2 while consuming a very low power of 100 µW.

For establishing the reliability and dependability of the proposed RF down-converter, the corner, voltage, and temperature variation analysis are carried out across the required frequency range for conversion gain, noise figure and are shown in Figs. 17, 18, 19, 20, 21, and 22. Table 3 presents the corner, voltage, and temperature variation analysis for IIP2 and IIP3. The process and device mismatch analysis of the proposed down-conversion network is performed using Monte-Carlo simulation for gain, NF, IIP2, IIP3, and phase noise of the VCO at both 5 MHz offset and 100 MHz offset. The Monte-Carlo simulation has been run extensively for 500 samples of the process and device mismatch variation analysis with the maximum deviation (3σ). The histogram of the Monte-Carlo simulation results with the mean (µ) value and the standard deviation (3σ) value is shown in Fig. 23, 24, 25, 26, 27, 28. The Y-axis of the histograms represent the frequency of occurrence of the parameter values, and it is unitless.

Feedthrough causes DC offsets and affects the linearity of the wireless system. The feedthrough is caused by the substrate coupling of the strong LO signal in densely integrated systems. The effect of LO feedthrough is characterized by the LO to the RF signal feedthrough and the LO to the IF signal feedthrough. Figures 29 and 30 show the suppressed harmonics of the LO signal in the RF path and the IF path respectively. The fundamental harmonic of the LO signal in the RF path is measured as − 202.3 dB and in the IF path as − 40.17 dB respectively.

Finally, the figure-of-merit (FOM) is calculated for comparison of the proposed RF down-conversion network with the existing frequency translation circuits using the following expression

The Table 4 presents the transistor sizing for the proposed 3-stage down-converter and 2-stage ring network. The Table 5 shows the comparison of the proposed current sensing based 3-stage RFDC against the other current sensing based down-converters and inductorless down-converters reported in the literature. The Table 6 presents the comparison of the proposed mixer and VCO network against some of the existing architectures. It can be seen that the proposed RF down-conversion network performs better than the other reported circuits while consuming the lowest silicon area.

The proposed RFDC architecture is implemented in 180 nm since the IEEE 802.15.4 protocol specifies low-cost SoC for operation [1, 2]. Also, for sub-6 GHz 5G networks, 180 nm SoC is sufficient for quality performance. However, the proposed RFDC architecture can be implemented in lower technologies based on the bias conditions and aspect ratios required. Thus, the proposed RFDC architecture is unconstrained in its practical application.

5 Conclusion

A novel 3-stage RF down-converter and a 2-stage ring VCO is presented in this work with high linearity, high gain and low noise figure for direct down-conversion receivers employed in 2.4 GHz 5G IoT applications. The proposed network efficiently performs the frequency conversion while consuming only 12.6mW of power from a supply of 1.8 V. The PVT variation analysis and the Monte-Carlo simulations show the reliable, dependable, robust operation of the proposed down-conversion system in the required range of 2.4–2.485 GHz. The IIP2 of 78.13 dBm makes the proposed frequency translation network suitable for direct-conversion receiver architectures and the IIP3 of − 3.43 dBm enhances the overall dynamic range of the wireless receiver for distortionless operation. This makes the communication of data between sensor nodes and data centre to be less error-prone and increases the quality-of-service (QoS) of the network. The high conversion gain of 23.69 dB and noise figure of 12.76 dB helps with the overall noise performance of the wireless receiver, and also the high gain helps in reducing the additional amplification stages required in the receiver chain and thereby, the size of the devices is drastically minimized. The figure-of-merit (FoM) for the proposed network is 229.67, and it is found to be better than the other state-of-the-art down-converter and VCO co-designs reported in the literature. Thus, the proposed RF down-conversion circuit design is well suited for low-cost, low power, reliable, high-performance, area-efficient demands of portable, wearable 5G applications in the 2.4 GHz band without increasing the Bill-of-Materials (BoM) since the performance is available at low power consumption and low silicon area of merely 0.0043 mm2.

References

Wireless medium access control and physical layer specifications for low-rate wireless personal area networks. IEEE 802.15.4™ (2006)

Oh NJ, Lee SG (2006) Building a 2.4-GHz radio transceiver using IEEE 802.15.4. IEEE Circ. Dev. Mag. 21:43–51

Abidi AA (1995) Direct-conversion radio transceivers for digital communications. IEEE J Solid-State Circuits 30(12):1399–1410

Razavi B (1997) Design considerations for direct-conversion receivers. IEEE Trans Circuits Syst-II: Analog Digit Signal Process 44(6):428–435

Razavi B (1997) A 900-MHz CMOS direct conversion receiver. In: Symposium on VLSI circuits

Kivekäs K, Pärssinen A, Halonen KAL (2001) Characterization of IIP2 and DC-Offsets in Transconductance Mixers. IEEE Trans Circuits Syst-II: Analog Digit Signal Process 48(11):1028–1038

Sivonen Pete, Vilander Ari, Pärssinen Aarno (2005) Cancellation of second-order intermodulation distortion and enhancement of IIP2 in common-source and common-emitter RF transconductors. IEEE Trans Circuits Syst-I: Regul Pap 52(2):305–317

Manstretta D, Brandolini M, Svelto F (2003) Second-order intermodulation mechanisms in CMOS downconverters. IEEE J Solid-State Circuits 38(3):394–406

Abidi AA (2003) General relations between IP2, IP3, and offsets in differential circuits and the effects of feedback. IEEE Trans Microw Theory Tech 51(5):1610–1612

Bautista Edwin E, Bastani Babak, Heck Joseph (2000) A high IIP2 downconversion mixer using dynamic matching. IEEE J Solid-State Circuits 35(12):1934–1941

N. Vitee, H. Ramiah, W.-K. Chong (2014) A wideband CMOS LNA-mixer for cognitive radio receiver. In: IEEE Asia Pacific conference on circuits and systems, pp 348–351

Wu C-H, Lin Y-P, You H-C, Huang S-Z (2014) A 1.04 mm2, low-power front-end circuit of receiver in 0.18 μm CMOS for IEEE 802.11a application. In: IEEE Asia Pacific conference on circuits and systems

Chironi V, Pasca M, Siciliano P, D’Amico S (2015) A 5.8–13 GHz SDR RF front-end for wireless sensors network robust to out-of-band interferers in 65 nm CMOS. In: 6th international workshop on advances in sensors and interfaces

El-Desouki M, Qasim SM, BenSaleh MS, Deen MJ (2015) Toward realization of 2.4 GHz Balunless narrowband receiver front-end for short range wireless applications. Sens J 15:10791–10805

Liu H, Qu X, Cao L, Liu R, Zhang Y, Zhang M, Li X, Wang W, Lu C (2018) A 5.8 GHz DSRC digitally controlled CMOS RF-SoC transceiver for China ETC. In: IEEE 23rd Asia and South Pacific design automation conference (ASPDAC), pp 323–324

Cao L, Liu R, Zhang Y, Zhang M, Li X, Wang W, Liu H, Lu C (2018) A 5.8 GHz digitally controlled CMOS receiver with a wide dynamic range for Chinese ETC systems. IEEE Trans Circuits Syst II: Express Briefs 65:754–758

Chong W-K, Ramiah H, Tan G-H, Vitee N, Kanesan J (2014) Design of ultra-low voltage integrated CMOS based LNA and mixer for Zigbee application. AEU-Int J Electron Commun 68:138–142

Li Z, Cheng G, Wang Z (2018) A 0.1–1 GHz low power RF receiver front-end with noise cancellation technique for WSN applications. AEU-Int J Electron Commun 83:288–294

Li Z, Yao Y, Wang Z, Cheng G, Luo L (2018) A 1 V 1.4 mW multi-band ZigBee receiver with 64 dB SFDR. Microelectron J 76:43–51

Wu C-H, Jian G-X (2010) Design of up conversion mixer with enhanced transconductance stage and low power consumption oscillator. In: Proceedings of international symposium on signals, systems and electronics

Wu C-H, Wu N-Y (2011) Design of low power up conversion self-oscillating mixer. In: China-Japan joint microwave conference proceedings

Lai W-C, Huang J-F, Hsu C-M, Yang P-G (2011) Low power VCO and mixer for computing miracast and mobile bluetooth applications. In: International conference on cyber-enabled distributed computing and knowledge discovery

Razavi B (2002) Design of analog CMOS integrated circuits. Tata-McGraw Hill Edition

Razavi B (2012) RF microelectronics. Pearson Education

Leung B (2002) VLSI for wireless communication. Pearson Education

Gladson SC, Bhaskar M (2018) A low power high-performance area efficient RF front-end exploiting body effect for 2.4 GHz IEEE 802.15.4 applications. Int J Electron Commun (AEÜ) 96:81–92. https://doi.org/10.1016/j.aeue.2018.09.009

Visweswaran A, Long JR (2017) Injection-locked wideband FM demodulation at IF. IEEE J Solid-State Circuits 52(2):327–343

Wang S-F (2015) Low-voltage, full-swing voltage-controlled oscillator with symmetrical even-phase outputs based on single-ended delay cells. IEEE Trans Very Large Scale Integr Syst 23(9):1801–1807

Docking S, Sachdev M (2003) A method to derive an equation for the oscillating frequency of the ring oscillator. IEEE Trans Circuits Syst-I: Fundam Theory Appl 50(2):259–264

Docking S, Sachdev M (2004) An analytical equation for the oscillating frequency of high-frequency ring oscillators. IEEE Trans Solid-State Circuits 39(3):533–537

Allstot DJ, Li X, Shekhar S (2004) Design considerations for CMOS low-noise amplifiers. In: IEEE radio frequency integrated circuits (RFIC) symposium

Funding

This work was funded by Ministry of Electronics and Information Technology (MeiTy), Govt. of India, with grant no. VISPHD-MEITY-1708.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Gladson, S.C., Bhaskar, M. A 3-stage RF down-converter network for portable, wearable 5G applications. SN Appl. Sci. 2, 61 (2020). https://doi.org/10.1007/s42452-019-1850-0

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s42452-019-1850-0