Abstract

This paper uses Stanford model for MOS-like CNTFET in order to find optimum values of its parameters. The purpose is to test well-designed NAND and D-Latch ICs based on this optimized CNTFET at \(V_{\text{DD}} = 0.9\,{\text{V}}\) in 32-nm technology by HSPICE, in order to observed PDP-based error (power–delay product-based error). This error causes a growth in power consumption of logic gates and circuits. Importance of using “trade-off factor” instead of “PDP factor” in some specific cases is clearly illustrated in this paper. The optimum values of MOS-like CNTFET parameters which are obtained in by Stanford model this paper, are the same as the optimum ones in previous works. This research displays a useful insight about MOS-like CNTFET and PDP-based error and presents trade-off factor to making well-designed gates and circuits.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The first integrated circuit (IC) based on transistors was built in 1958. Over time, the dimensions of these transistors have become smaller and their structures have changed. FINFET, nanowire FET, carbon nanotube FET (CNTFET), etc., are some examples of these new structures. In fact, the ultimate goal is to manufacture an improved IC with smallest dimensions, less power consumption, lower cost, simplest structure, and highest processing speed. Some researchers have endeavored to investigate on different models of both CMOS and CNTFET, design some logic gates by using them, and compare their results. For example, they compared:

-

CMOS and standard-CNTFET [1]

-

C-CMOS (Conventional CMOS), FINFET, and MOS-like CNTFET [7]

-

C-CMOS and CNTFET [8]

-

CMOS and MOS-like CNTFET [9]

By testing the logic gates and circuits (such as AND, OR, MUX, full adder) which were based on CMOS and CNTFET [1,2,3,4,5,6,7,8,9], researchers declared that CNTFET models can provide better results than CMOS models because they can reduce average power, delay, PDP (power–delay product), increase performance speed, and occupy less volume in ICs. These studies were done in different conditions:

-

In \(0.18\,\upmu{\text{m}}\),\(32\,{\text{nm}}\) and \(16\,{\text{nm}}\) process technologies [1, 5,6,7]

-

At different power supply voltages (\(V_{\text{DD}} = 0.5\,{\text{V}}, 0.65\,{\text{V}}, 0.7\,{\text{V}}, 0.8\,{\text{V}}\;{\text{or}}\; 0.9\,{\text{V}}\)) [4, 5, 7, 8]

-

Changing the gate-source voltage (\(0 \le V_{\text{GS}} \le 0.6\;{\text{V}}\)) [4]

Given the advantages of CNTFET over CMOS (according to [1,2,3,4,5,6,7,8,9]), MOS-like CNTFET (Stanford model [7, 9]) is selected and investigated in this paper. For beginning, I study its parameters in NAND structure by HSPICE at \(V_{\text{DD}} = 0.9\,{\text{V}}\) and \(f_{\text{data}} = 250\,{\text{MHz}}\), in 32 nm technology. This paper does not present new model for CNTFET or compare MOS-like CNTFET with other kinds, but it tries to find optimum values for CNTFET parameters by the Stanford model code, illustrate the error of PDP factor and also present “trade-off factor” instead of “PDP factor” in some specific cases. These optimum values for each parameter (pitch, N, and chiral vector) leads to have improved MOS-like CNTFET and optimized NAND gate. Then, a D-Latch (data latch or D-type latch) based on this NAND is tested in order to design an optimized IC with low average power and delay. During this process, the error is displayed. This process shows that this CNTFET (due to its optimized parameters) will provide high performance even in a complicated IC such as FPGA, to make it optimum.

2 Optimum design and test results

2.1 MOS-like CNTFET (Stanford model: HSPICE)

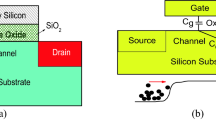

When channel length of MOSFET reaches bellow 10 nm, we actually will face a limit [10]. CNTFET is one of the choices because of its semiconducting and current-carrying properties [10]. Well-controlled channel, high ON current, easily design, and implementation of multi-threshold structures with less complexity are the main advantages of CNTFET over MOSFET [7]. MOS-like CNTFET, which is shown in Fig. 1, has a similar structure as MOSFET. Parameters \(L_{\text{ch}}\), \(W_{\text{gate}}\), \(L_{\text{dd}}\), \(L_{\text{ss}}\), \({\text{Pitch}}\), and \(N\) are, respectively, channel length, channel width, nanotubes length between gate and drain, nanotubes length between gate and source, distance between two adjoining nanotubes, and the number of nanotubes (see Fig. 1a). Parameters N and pitch define \(I_{\text{CNT}}\) (the current from drain to source) and \(W_{\text{gate}}\). These two parameters actually determine the CNTFET dimensions, speed and power consumption, so their values should be selected according to delay and average power. Another important factor in CNTFETs is diameter of nanotubes (\(D_{\text{CNT}}\)) that has effect on \(I_{\text{CNT}} \left( {\text{on}} \right)\). This factor is usually presented by chiral vector. The related equations are [7, 11]:

The coefficient \(a_{0}\) is distance between two carbon atoms (\(\approx 0.142\; {\text{nm}}\)), and the parameters m and n are integers which show the chirality of nanotube. Value of \(V_{\text{th}}\) changes with CNTFET diameter so each CNTFET can have its own \(V_{\text{th}}\) in an IC. The parameters \(g_{\text{CNT}}\),\(L_{\text{s}}\) and \(\rho_{\text{s}}\) are, respectively, transconductance, source length, and source–carrier density (Fig. 2). Investigation on MOS-like CNTFET-based ICs is done by Stanford model (in 32-nm technology) because it includes practical non-idealities such as scattering, inter-CNT charge screening effects, the channel length dependence of current drive, the geometry dependence of the gate-to-channel capacitance, the interconnect wiring capacitance, the source/drain series resistance and their contact resistance, and also parasitic effects, apart from accurate predictions of dynamic and transient performance with more than 90% accuracy [12,13,14]. The simulations are carried in HSPICE software at \(V_{\text{DD}} = 0.9\,{\text{V}}\) and \(f_{\text{data}} = 250\,{\text{MHz}}\) and results are explained in subsections 2.2 and 2.3. The error based on PDP (power–delay product) factor is illustrated too.

a The CNTFET schematic, b the structure of a MOS-like CNTFET [7]

The structure of a two-input NAND based on CNTFET [7]

2.2 NAND gate

In this study, I design a NAND gate based on four MOS-like CNTFETs and set its pitch at 5 nm. After testing its delay, average power, and PDP at different values of N, the process is repeated for pitch = 10 nm and pitch = 20 nm to observe effects of the N-changes and pitch changes on the NAND properties. The test results are placed in Table 1, and their curves are shown in Fig. 3. The increase in N causes the delay reduction and average power growth, because the number of current path is added. Thus there are two options to have an optimized NAND:

-

According to PDP factor, the optimum value for N is 9 because we have the minimum PDP at this number (see Table 1).

-

According to the delay and average power factors, the optimum value for N is 3 because there is a best trade-off between delay and power consumption (see Fig. 3 and Table 1).

At N = 9, the power consumption is approximately doubled, but the delay just has 1-ps improvement than N = 3, and therefore, the number 9 is not optimum value of N. PDP is not really a good factor for investigating properties of one kind of transistor (such as MOS-like CNTFET) or one kind of logic gate (such as NAND). But when the comparison is between two or more kinds of transistors or between two or more kinds of logic gates, using PDP factor can speed up the comparison process without occurring any error. For instance, the comparison between “C-CMOS-based NAND” and “TG-based NAND” which is done by PDP results [7]. Even for testing logic circuits (e.g., D-Latch, full adder, shift register, SRAM, FPGA, etc.) which are composed of different gates, PDP factor is also useful [5]. As a result, in this condition, N = 3 is the optimum value, and the trade-off between delay and average power is the best factor. Now the effects of pitch and chiral vector changes at N = 3 should be checked.

Based on Table 1 results, the growth in the pitch value reduces the delay and increases the power consumption, but because of current saturation, this procedure is not intense and the values are close together. This phenomenon is observed again when the effect of pitch changes is studied at chiral vector (19, 0) and N = 3 that its results are placed in Table 2. We have the best trade-off between delay and average power at pitch = 10 nm. Notice that in this case, PDP factor has the same result as trade-off factor, and both of them show that 10 nm is the optimum value of pitch, but it does not mean that the PDP can be a proper factor for testing one kind of transistor or logic gate. By reduction of the pitch value, the coating effect between nanotubes increases, and it causes an enhancement in the capacitance of parasitic capacitors between nanotubes, and therefore, we observe the delay increase and current decrease (power reduction) in Table 2.

The final step for designing an improved NAND based on optimized MOS-like CNTFET is to peruse the effects of chiral vector changes at N = 3 and pitch = 10 nm. As stated in Sect. 2.1 (Eq. 2, 3), the chiral vector represents the diameter of nanotubes, for example, (19, 0) is equal to 1.478 nm [7]. According to Table 3, the increase in nanotubes diameter causes the current enhancement, so it raises the power consumption. The PDP factor chooses the vector (25, 0) as the optimum chiral vector. But Figs. 4, 5 (based on Table 3) show that the vector (19, 0) has the best trade-off between delay and average power. If we select the vector (25, 0), the power consumption increases in exchange for 0.5 ps less delay, than the vector (19, 0). Thus the error of using PDP factor shows itself again. As a result, the optimum values for MOS-like CNTFET are N = 3, pitch = 10 nm and the chiral vector (19, 0) which lead to have an improved NAND. These results are achieved in previous works that proves their validity, such as [7] and [11] which, respectively, proposes the chiral vectors “(19, 0) and (22, 0)” and “(10, 0), (19, 0) and (29, 0)” for CNTFET but “trade-off factor” in this paper shows why (19, 0) is better. In fact, I use CNTFET (Because of its advantages over MOSFET) and Stanford model (for its non-idealities) to make a well-designed NAND and display the error of using “PDP factor”. NANDs are universal gates that it means all other gates and circuits, e.g., memories and FPGAs, can be designed optimally by this gate if we make it optimum!

HSPICE simulation for this optimized NAND is done by CNTFET library (in 32 nm technology based on Stanford model) at \(V_{\text{DD}} = 0.9^{V}\) and \(f_{\text{data}} = 250^{\text{MHz}}\) which its waveforms are displayed in Fig. 6. The results match table in Fig. 2. It is important to note that, based on Eq. 5, we can have better power consumption at lower \(V_{\text{DD}}\) because \(I_{\text{CNT}}\) will decrease. In subsection 2.3, an improved D-Latch based on this optimized NAND is tested.

2.3 D-Latch IC

D-Latch (data latch) is the smallest element of memory which can store one bit (0 or 1) in itself and its performance is near to D-FF (delay flip-flop). As pictured in Fig. 7, it consists of four optimized NAND and one optimized NOT (which can be made by 1 optimized NAND). Clock pulse and data are applied to the “\(En\)” and “\(D\)” input ports, respectively. Data storage occurs at EN = 0 and its release on \(Q\) output port occurs at EN = 1. Output of the port \(Q^{\prime}\) is the reverse of \(Q\). Effects of N, pitch, and chiral vector changes are observable in Tables 4, 5, 6 respectively. All three tables show that “trade-off” and “PDP” factors have the same result. Both of them refer to N = 3, pitch = 10 nm, and chiral vector (19, 0). This fact proves that PDP is a useful factor to test the performance of a logic circuit (like D-Latch), not a logic gate or a transistor.

Assume we choose N = 9 instead of N = 3 (see Table 1), so the power consumption becomes approximately doubled in one NAND. Then for a D-Latch with four NAND and one NOT, the power consumption becomes at least 10 times higher. Table 4 displays that the average power at N = 9 is equal to \(6.667 \times 10^{ - 7} \,{\text{W}}\) which is 14 times higher than the average power at N = 3. Figure 8 shows input and output waveforms of this improved D-Latch that its HSPICE Simulation is done by CNTFET library (in 32-nm technology based on Stanford model) at \(V_{\text{DD}} = 0.9^{\text{V}}\),\(f_{\text{CLK}} = 1^{\text{GHz}}\) and \(f_{\text{data}} = 250^{\text{MHz}}\). This research demonstrates that this optimized MOS-like CNTFET will provide low power consumption and high processing speed even in complicated circuits such as memories, FPGAs, and processors.

3 Conclusion

After discovering the new carbon structure (C60) in 1985 and making the carbon nanotubes (CNTs) in 1991, the first CNT-based transistor was built in 1998. Its new models have been designed by the efforts of researchers that MOS-like CNTFET is one of these models. This paper tests NAND and D-Latch based on MOS-like CNTFET by HSPICE based on Stanford model in 32-nm technology, and tries to find optimum values of this CNTFET parameters in order to have an optimized universal gate (NAND) which can provide an optimized ICs such as D-Latch, D-FF, memory, FPGA. It also shows that the usage of PDP factor for considering one transistor (such as MOS-like CNTFET) or one logic gate (such as NAND) causes an important error which can intensely enhance power consumption at complicated ICs. This study does not present new model for CNTFET, but it tries to design improved gates and ICs according to PDP and trade-off factors and explains why, for example, the chiral vector (19, 0) is proper than (10, 0), (22, 0) and (29, 0) because all of them were proposed related works. As a result, it presents the trade-off between delay and average power as a proper factor to make them optimized. But also it emphasizes that for investigation one logic circuits (such as D-Latch), or for comparison between two or more kinds of transistors or two or more kinds of logic gates, using PDP factor can speed up our test process without occurring any error. The optimum values for a MOS-like CNTFET (based on the Stanford model) are N = 3, pitch = 10 nm and the chiral vector (19, 0).

References

Mane KS, Narwade PP (2015) Efficient digital circuits based on CNTFET. Int J Electr Electron Eng 7:467–473

Kaur H, Kaur S, Rani EP (2015) A review on design and analysis of D–flip flop with different technologies. Int J Technol Enhanc Emerg Eng Res (IJTEEE) 3:32–35

Saketh KS, Monica PR (2013) Ternary logic implementation and its applications using CNTFET. In: IEEE computer society, IEEE international conference on advanced electronic system (ICAES)

Shreya S, Chandel R (2014) Performance analysis of CNTFET based digital logic circuits. IEEE

Arunlakshman M (2014) An area, delay and power efficient push pull D–flip flop based shift registers In: 32 nm Carbon nano tube field effect transistors (CNTFET) and its comparative analysis with 16 nm MOSFET technology. international journal of emerging technology and research (IJETR), vol 1, ISSN (E): 2347-5900

Murotiya S L, Gupta A (2013) Performance evaluation of CNTFET based dynamic dual edge triggered register. In: International conference on advanced electronic systems (ICAES), IEEE Computer Society

Gowri Sankar PA, Udhayakumar K (2014) MOSFET-like CNFET based logic gate library for low-power application: a comparative study. J Semicond 35(7):75001

I’msaddak L, Issa D B, Kachouri A (2013) Compact modeling and application of carbon nanotube field effect transistors CNTFETs based CMOS-like complementary NOR, OR, NAND, and AND logic gates. In: IEEE 8th international conference on design and technology of integrated systems in nano-scale era (DTlS)

Prabhu S, Sarwade N (2013) Hspice implementation of CNTFET digital gates. Int J Emerg Trends Electr Electron 5:50–53

Fedawy M, Fikry W, Alhenawy A, Hassan H (2012) I–V characteristics model for ballistic single wall carbon nanotube field effect transistors (SW-CNTFET). In: IEEE international conference on electronics design, systems and applications (ICEDSA)

Moaiyeri MH, Mirzaee RF, Doostaregan A, Navi K, Hashemipour O (2013) A universal method for designing low-power carbon nanotube FET-based multiple-valued logic circuits. IET Comput Digital Tech 7(4):167–181

Usmani FA, Hasan M (2010) Carbon nanotube field effect transistors for high performance analog applications: an optimum design approach. Microelectron J 41:395–402

Murotiya S L, Gupta A (2013) Performance evaluation of CNTFET based dynamic dual edge triggered register. In: International conference on advanced electronic systems (ICAES)

Stanford University CNTFET Model website (online). https://nano.stanford.edu/stanford-cnfet-model

Acknowledgement

The author would like to thank Dr. Seyed Ali Sedigh Ziabari and Mr. Shahab Shahrabadi for their suggestions.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The author declares that there is no conflict of interest associated in this manuscript.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Shahrabadi, S. Investigating PDP-based error by testing NAND and D-Latch based on CNTFET (Stanford model). SN Appl. Sci. 1, 702 (2019). https://doi.org/10.1007/s42452-019-0742-7

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s42452-019-0742-7