Abstract

The low-cost Continuous Wave (CW) radar architecture for object speed detection is presented in this research. An FPGA (Field-Programmable Gate Array) processor is utilized to implement the CW radar dependably and optimally. The suggested approach uses a bank of filters made expressly to extract velocity information from radar signals to compute the target velocity. Depending on the needs of the particular application, the acquired data has either undergone additional processing or been presented in an approachable manner. The implemented design is checked in real-time with a chip scope, functionally simulated, and then inspected with lab instruments to compare all simulated and implemented outcomes. Numerous applications, such as industrial automation, surveillance, and automotive systems, where accurate velocity detection is crucial and low-cost design is required, could benefit from this concept.

Similar content being viewed by others

Explore related subjects

Find the latest articles, discoveries, and news in related topics.Avoid common mistakes on your manuscript.

1 Introduction

Recently, various radar systems have been designed to detect target velocity [1,2,3,4,5], but they all have weaknesses in many requirements. In [1], the authors decided that the stationary or multiple targets can be detected and false alarm detection may occur. Detection of targets at distance greater than 5 m is difficult compared with other radars and consequently, their angular resolution is poor [2]. There are problems when detecting a target in dark or in presence of obstacles and high-performance hardware is required for system computations and data extraction [3]. Lidar radar is extremely expensive compared with other applications and susceptibility to weather conditions [4]. In [5], design and implementation of radar signal processing using FPGA is applied in Linear Frequency Modulated Continuous Wave Radar (LFMCW) radar based on adaptive threshold but the complexity is high according to the complexity of compressive sensing due to target information extraction such as range and velocity. Other applications that use the radar sensors in industrial machinery, drones, automobiles [6, 7]

Also, in [8] target classification and estimating movement direction with accuracy of 85%. In addition, the authors in [9] integrate both the transmitter/ receiver circuit with the radar antenna to reduce the radar size.

Radar can be classified into two main parts; pulsed and CW, the latter is simple to implement and has received increasing attention [10]. The velocity of the target can be extracted from the received data after signal processing, also the target range can be determined, according to the radar objectives, after modulating in the frequency of the transmitted signals. Target velocity and range can be evaluated using two-dimensional (2D) Fast Fourier Transform (FFT) in both range and azimuth directions [11]. Radar signal has been processed for target detection and classifications as illustrated in [12,13,14].

Nowadays, FMCW radars are often called “radars of the future” due to achievement an extremely high degree of range resolution making the radar less susceptible to interfering clutter and also Low Probability of Interception (LPI). It is usually in S band or L band that the industry still uses chirp pulse radars, because of the need for long ranges. FMCW radars, unfortunately, do not have long ranges. FMCW radars find widespread usage in military applications and marine navigation due to their stealth properties, allowing them to see without being seen and giving away their location to radar interceptors [15].

In the present work, target velocity only can be extracted from the received radar signals using Doppler filter bank which is designed according to the range of measured velocities. The suggested approach can resolve many problems that appear in the previous related works. Also, image processing can be added in the algorithm if the vehicle plate is required according to the police radar speed in the main highway. The organization of this paper is planned as follows; after the introduction, Sect. 2 gives a survey on the continuous wave radar. Section 3 focuses on the methods of target speed detection. Hardware implementation of the proposed design is presented in Sect. 4. Real-time implementation and experimental results are presented in Sect. 5. Finally, the conclusion comes in Sect. 6.

1.1 Continuous wave radar review

The main function of CW radar system is measuring target speed. However, it does not provide any range (distance) information unless a modulation in frequency is required to perform this matter. The speed can be determined using frequency difference between the transmitted and received signal frequencies which is called Doppler frequency.

Radar motion sensors are based on the same principle, but they must also be capable of detecting slow changes in the received field strength due to variable interference conditions that may exist.

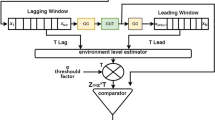

Continuous Wave (CW) radar has several advantages over other radar systems such as: simplicity, low-cost effective, small size, low power consumption, and Doppler capability [16]. According to Fig. 1 which represents the general block diagram of CW radar system, the receiver declares detection at a certain Doppler pin if the output passes through the detection threshold in the detector block. Narrow Filter Bank (NFB) is used after the digital detector output which consists of many filters’ frequency ranges. The length of such blocks is normally referred to as the dwell interval, integration time, or coherent processing interval. The dwell interval determines the frequency resolution or the bandwidth of the individual NBFs.

General block diagram of CW radar system [16]

If the range of the detected target is called “R”, the total distance between the radar and target in a two-way communication path will be 2R. Then, the total angle of excursion made by the electromagnetic wave during the two-way communication path between the Radar and target will be equal to 4πR/λ radians. Where λ is one wave length.

The relation between the angular frequency, w, and phase angle, Φ, is given by:

where, f is the signal frequency, that Eq. (1) can be written as:

Substitute, the phase angle by 4πR/λ in Eq. (2), so the Doppler frequency, \({f}_{d}\), can be written as:

where Vr is the target speed. The CW radar equation can now be determined according to the following equation:

where \({P}_{av}\) is the average power transmitted by the radar system, T is the time duration, \({G}_{r}\) is the receiver antenna gain, \({G}_{t}\) is the transmitted antenna gain, \(\sigma\) is the radar cross-section, \(K\) is the Boltzman constant, \({T}_{o}\) is the room temperature, \(F\) is the system noise figure, and L is the system losses.

1.2 Target speed detection

In FMCW radar, the transmitted waveform can be either triangular or sawtooth to extract the target information. But sawtooth transmission waveforms are commonly used in many radar systems. The frequency of the sawtooth waveform is defined by Eq. (5).

where fc is the carrier frequency; B is the bandwidth; and T is the period. For simplicity, replace B/T by α, and consequently the instantaneous phase, \(\varphi \left(t\right),\) of the transmitted signal can be obtained by integrating the transmitted signal frequency with respect to time t, as illustrated in Eq. (6).

The transmitted signal, STx(t), with initial phase, \({\varphi }_{o}\), and amplitude, A, can be obtained according to Eq. (7).

The received signal, SRx(t), can be expressed after a certain time delay as in Eq. (8)

where B is the received signal amplitude, and τ is expressed as

Here, C is the speed of light.

Figure 2 shows the block diagram of the FMCW radar signal processing based on FFT in range and Doppler directions.

Figure 3 represents a block diagram of radar signal processing for target speed detection based on filter bank. The received beat signal is digitized using Analog-to-Digital (ADC) converter. Window can be used if clutter or unwanted signals are joint to the useful signals with high side lobe levels.

1.3 Hardware Architecture of the proposed design

The proposed signal processor algorithm of CW radar system based on filter bank is implemented using FPGA kit. The usage of FPGA in signal processing has many advantages where it consists of many blocks are composed of lookup tables (LUTs) and flip-flops that can be programmed to implement complex logic functions and algorithms. Also, the interconnects provide pathways for routing signals between different logic blocks, allowing for flexible connectivity. The used FPGA contains many functions that can realize the signal processing algorithms such as: Programmable input/output (I/O) unit, basic programmable logic unit, embedded RAM, abundant wiring resources, bottom embedded functional unit, and embedded dedicated hard core. The used FPGA consists of UltraScale Kintex + platform using the Vivado Xilinx tool. A flow chart describing the process of the signal processor using FPGA to detect the target speed as illustrated in Fig. 4.

The received radar signal is applied to the bank of filters through the used FPGA kit. The bandwidth of each filter is designed according to the specific target speed as shown in Table 1. The response of each filter is obtained which consequently represents nearly the target speed. Once the target speed information has been extracted from the analyzed output filter response, it can be utilized for further processing or display, depending on the specific requirements. This information may be employed in subsequent stages of the signal processing pipeline or presented in a user-friendly format.

According to the filter bank effect, the target speed can be determined according to the bandwidth of the specific filter. In the proposed signal processor, the filter bank is divided into 6 filters with different bandwidths as shown in the above table. The target speed range is considered from 50 km/hr till 100 km/hr which can be changed according to the filter bandwidth.

The hardware implementation of the proposed processor is mainly divided into three stages; first one is the verification of the received signal using FPGA [17, 18], second stage is the verification and implementation of the filter bank specifications, and the third stage is the target speed calculations and display the result.

First stage: The received signal is digitized using ADC converter and then analyzed and verified using FPGA as shown in Fig. 5.

Second stage: According to Table 1 which specifies the bandwidth of the designed filters, there are six filters with different bandwidths dependent on the corresponding target speed; low pass filter with cutoff frequency at 1 MHz, band pass filter with bandwidth form 1 MHz to 5 MHz, band pass filter with bandwidth form 6 MHz to 10 MHz, band pass filter with bandwidth form 11 MHz to 15 MHz, band pass filter with bandwidth form 16 MHz to 20 MHz, and high pass filter with cutoff frequency at 20 MHz as shown in Fig. 6.

1.4 Real-time implementation and Results

The filter specifications in the bank are verified using both MATLAB and Vivado as shown in Fig. 7 and Fig. 8 respectively [19, 20].

Third stage: Target speed can be determined according to the doppler frequency of the received radar signal which extracted from the filter bank using FPGA as shown in Fig. 9.

The output response of each filter leads to a certain speed according to Table 1 within an accuracy of 1 MHz for every 2 km/hr target speed. This accuracy can be modified according to the processor design of the filter bank. The response of any filter can be tested using FPGA as illustrated in Fig. 10. The response of filter number 3 which indicates to target speed of 70 km/hr. From this figure, it is clear that, the output response of any filter can be used to calculate the target speed correctly (Table 2).

1.5 Real-Time implementation and experimental results

The real-experiment includes hardware components and software programming using FPGA. The hardware components are FPGA signal processor kit, ADC and DAC for analog and digital signal interface, power spectrum analyzer, digital oscilloscope, and LCD display. The experiment setup is illustrated in Fig. 11.

Figure 12 represents target speed detection at velocity 80 km/hr as illustrates on digital oscilloscope. The response of digital filter associated with this speed at 13 MHz is measured and tested as shown in Fig. 13. The measured target speed is then appeared on LCD display to ensure the accurate speed as shown in Fig. 14.

According to these results from the real experiment, it is clear that, the target speed can be detected and measured using low- cost components and with suitable accurate according to the design parameters of doppler filter bank.

From this comparison, it is clear that, the proposed radar processor has lower complexity compared with the other radar processor and any modifications can be achieved on the proposed algorithm to enhance the output detection with keeping lower complexity.

2 Conclusion

This study describes the design of a low-cost CW radar signal processor that uses FPGA technology to determine vehicle speed. In addition to using FPGA, the system is scalable and flexible, which makes it easy to modify for improvements and optimizations down the road.

A Doppler filter bank is constructed with bandwidths corresponding to the upper limit of the vehicle's speed range thanks to programming in the FPGA. Every filter response is connected to the desired speed based on user-controlled accuracy. The usability of the radar signal processor is further improved by integrating it with a Raspberry Pi and a monitor, which offers a user-friendly interface for visualizing and presenting the velocity of the discovered targets.

This hardware configuration enables a small and affordable radar system that may be used for several tasks, including object tracking, speed measurement, and traffic monitoring. As technology advances, it will be possible to improve the radar system, including range detection capabilities. Pulse compression approach can be added or any processing algorithms, including time-of-flight measurements. In addition to velocity detection, precise target range information can be acquired by incorporating these techniques into the radar system. In the future, this technique can be changed to employ the FFT algorithm for precise target speed measurement. Along with a high-quality camera, image processing can be added to this technique for more applications using the same hardware.

Finally, the parameters of the signal processor are adjusted for optimal performance based on the Doppler filter bank bandwidths and the range of vehicle velocities. As various scenarios are applied in real time, the radar settings are changed. When compared to other processors, the suggested radar signal processor is inexpensive and small. For the future scope, this paper can be considered as a first step to design a complete radar system with low cost and moderate accuracy according to the other subsystem design such as the antenna and the transceiver.

References

Cardillo E, Li C, Caddemi A (2021) Embedded heating, ventilation, and air-conditioning control systems: From traditional technologies toward radar advanced sensing. Adv Measure Instrument Leveraging Embedded Syst Rev Sci Instrum 92:061501

Shao Y, Chen P, Cao T A grid projection method based on ultrasonic sensor for parking space detection. In: Proceedings of the IGARSS 2018, IEEE International Geoscience and Remote Sensing Symposium, Valencia, Spain; pp. 3378–3381, 2018.

Son Y, Heo SW (2018) A novel multi-target detection algorithm for automotive FMCW radar. In: Proceedings of the 2018 international conference on electronics, information, and communication (ICEIC), Honolulu, USA; pp 1–3.

Han J, Liao Y, Zhang J, Wang S, Li S (2018) Target fusion detection of LiDAR and camera based on the improved YOLO algorithm. Mathematics, vol. 6

Salem SG Design and implementation of proposed pipelined adaptive recovery CAMP algorithm for LFMCW radar, Journal of Signal, Image and Video Processing (SIVP), Springer-Verlag London Ltd, 2020.

Hyun E, Jin YS, Lee JH Moving and stationary target detection scheme using coherent integration and subtraction for automotive FMCW radar systems. In: Proceedings of the IEEE Radar Conference (Radar Conf), Seattle, WA, USA; pp 0476–0481, 2017.

Zhang Z, Tian Z, Zhou M, Latern (2018) Dynamic continuous hand gesture recognition using FMCW radar sensor. IEEE Sens J, 18: 3278–3289

Kim JC, Jeong HG, Lee S (2021) Simultaneous target classification and moving direction estimation in millimeter-wave radar system. Sensors 21:5228

Di Mattia V, Manfredi G, De Leo A, Russo P, Scalise L, Cerri G, Cardillo E A feasibility study of a compact radar system for autonomous walking of blind people. In: Proceedings of the IEEE 2nd International Forum on Research and Technologies for Society and Industry Leveraging a Better Tomorrow (RTSI), Bologna, Italy, pp. 1–5, 2016.

Hyun E, Jin YS, Lee JH (2016) A pedestrian detection scheme using a coherent phase difference method based on 2D range-Doppler FMCW radar. Sensors 16:124

Salem SG, Kader FA Analysis and Design of Compressive Pulsed Radar Based on Adaptive Pipelined Algorithm, IETE Journal of Research, 2022.

Rekha Y, Pawan K, Rajesh M (2020) Comparative analysis of automotive radar sensor for collision detection and warning system. Int j inf Tecnol 12:289–294

Galati1 G, Pavan1 G, Wasserzier C Signal design and processing for noise radar, EURASIP Journal on Advances in Signal Processing, SprongerOpen,vol.52, 2022.

Nabiha B, Rim G, Hassen F, Chokri S (2019) VLSI implementation of residue number system based efficient digital signal processor architecture for wireless sensor nodes. Int j inf Tecnol 11:829–840

Jankiraman M FMCW Radar Design, Artech House Boston London, ISBN 13: 978-1-63081-567-7 MA, 2018.

Bassem RM (2022) Radar systems analysis and design using MATLAB, 4th edn. CRC Press, Taylor & Francis Group

Rupal G, Adesh K, Gaur S Design and implementation of I2C interface on FPGA for space borne AIS receiver in embedded system, Int J Inf Tecnol, 11: 331–340, 2019.

Karim E, Memon T, Hussain I (2019) FPGA based on-line fault diagnostic of induction motors using electrical signature analysis. Int j inf Tecnol 11:165–169

Iman F (2022) Real‑Time FPGA Implementation of FIR Filter Using OpenCL Design. J Signal Process Syst, Springer, 94: 117–129.

Dhan M, Priya R, Sree Sharm T (2019) Acoustic image denoising using various spatial filtering techniques, Int J Inf Tecnol. 11: 659–665

Funding

Open access funding provided by The Science, Technology & Innovation Funding Authority (STDF) in cooperation with The Egyptian Knowledge Bank (EKB).

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

No Conflict-of-Interest.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Salem, S.G., Hosseny, M.E. Signal processing implementation of low-cost target speed detection of CW radar using FPGA. Int. j. inf. tecnol. (2024). https://doi.org/10.1007/s41870-024-02033-3

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s41870-024-02033-3