Abstract

Thin-film solar cell devices based on copper indium gallium diselenide (CIGSe) chalcogenide materials fabricated by vacuum-based deposition techniques have already achieved lab scale efficiency beyond 21%. For industrial-scale applications, non-vacuum deposition technique such as electrodeposition and screen printing is considered to be suitable approaches for reducing the device fabrication cost. Moreover, electrodeposition has the potential to prepare large area thin films as it requires cheap raw material sources and equipment capital. Hence, it is imperative to understand the current status and advancements in the electroplating techniques of the CIGSe thin films. This article reviews on the experimental advances in electroplating of ternary CuInSe2 and quaternary CIGSe. Various approaches in electrodeposition, influential experimental parameters, and the deposition mechanisms which are related to the final cell efficiency are discussed in detail.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

Introduction

Increasing demand for energy has spurred academic and technological interest to research into new resources, among which solar energy seems to be the most ideal to meet the target as it is abundant, clean, and inexhaustible. Gradually, solar energy is getting attention as an important source of renewable energy, since the other renewable technologies like solar heating, photovoltaics, solar thermal energy, solar architectures, and artificial photosynthesis are emerging to harness the radiant light and heat from sun. Furthermore, active solar techniques which convert solar energy from sunlight into electricity are primarily done using semiconducting materials that exhibit the photovoltaic effect (generating photocurrent upon illumination). A typical photovoltaic system employs solar panels, each comprising a number of solar cells, which generate electrical power. With a global market share of about 90%, silicon wafer-based solar cells are the first generation solar cells which started with single crystalline (mono-Si) and later developed to polycrystalline silicon (poly-Si or multi-crystalline Si). They exhibit a power conversion efficiency ranging between 12 and 16%, based on the variation of fabrication procedure and the wafer quality [1]. Though mono-Si devices exhibit high efficiency and a dominant place in commercial market, setbacks such as expensive purification process, poor defect tolerance, indirect band-gap nature (less absorption coefficient) have made researchers seek for a better alternative.

The second generation or thin-film-based devices utilizing semiconducting materials like CISe/CIGSe, cadmium telluride (CdTe), and Si (a-Si) are then emerged as the alternatives to the first generation devices. Solar devices based on dye-sensitized solar cells (DSSC), organic photovoltaics (OPV), quantum dots, perovskite, tandem cells, hot carrier cells, impurity photovoltaics, and thermo-photovoltaics fall in the third generation solar cells. In specific, tandem configurations are designed to evade the power-loss mechanisms which take place in the conventional single band-gap (Eg) cells due to the inability to absorb photons beyond their Eg and thermalization of photons exceeding their Eg. By implementing semiconductor stacks exhibiting different bandgap, tandem configurations are realized with efficiencies exceeding the Shockley–Queisser limit [2].

Among the second generation photovoltaic (PV) cells, CIGSe-based devices are considered to be the most efficient solar energy converter of any single band-gap thin-film device. They can be easily fabricated on flexible substrates which make them light weight, and thus, they have the potential to reduce the device fabrication as well as the installation cost [3]. Recently, Chirilă et al. reported an efficiency of 20.4% for potassium fluoride post-deposition-treated (KF-PDT) CIGSe devices fabricated over flexible polyimide substrates. This efficiency is considered to be the highest until date for flexible CIGSe solar cells [4]. After discovering the beneficial effects of heavy alkali doping [potassium fluoride (KF), rubidium fluoride (RbF), and caesium fluoride (CsF) PDT treatment] [5], the CIGSe solar cell performance was boosted beyond 20%. A record device efficiency of 22.6% (0.4092 cm2) was also reported by Jackson et al. for RbF-PDT-treated CIGSe/CdS device [6]. Friedlmeier et al. reported an efficiency of 21% [7] using Zn(O,S) buffer as a replacement for the conventional CdS/CIGSe devices. Similarly, a record efficiency of 22.3% [8] was achieved for Cd-free device by SoloPower, utilizing (Zn,Mg)O/Zn(O,S,OH) as the window/buffer layer. Impressive efficiencies (~ 15.7 ± 0.5%) are also reported for CIGSe modules of 9703 cm2 aperture area [9]. These efficiency percentages motivate researchers to explore chalcogenide materials for industrial-scale production.

The above-reported CIGSe device record efficiency evolutions have been fabricated by vacuum deposition techniques, which are being challenged due to the expensive vacuum systems, target materials, and percentage of materials wastage. Hence, an alternative cost-effective deposition technique with competitive efficiency of the fabricated devices is sought for. Electrodeposition is a major technique which can respond to the challenges of reducing the PV device production cost due to cost-effective equipment capital, less material wastage, and its compatibility towards industrial-scale production. Electrochemically fabricated commercial solar cell devices with a reported efficiency of 14.2% have been obtained by SoloPower [10]. NEXCIS has achieved a record efficiency of 17.3% (0.484 cm2) and 14% for CIGSe module of aperture area 60 × 120 cm2. Excellent review on electrodeposition of semiconductors [11] and CIGSe electrodeposition [12] can be found. However, the technique has not yet been optimized for a single-step co-deposition of the quaternary alloy, and hence, it needs further research attention.

Hence, this review would be a complimentary addition to the research pool emphasizing on the recent technological advancements in the field of electrodeposition of CISe/CIGSe thin films. The review has been classified into five sections which provides some of the important aspects of the research area on electroplating of CISe/CIGSe thin films: (1) material properties of CISe/CIGSe: the review starts with this section which deals with copper chalcopyrite group material being explored as the second generation solar cells; (2) experimental concerns in electrodeposition explaining about the electrodeposition process of CIGSe and strategies to improve the quality of the electrodeposited final CIGSe thin films; (3) electrocrystallization mechanism of CIGSe; this section elaborates about the deposition mechanism of the four elements to form the alloy (4) advancements in CISe/CIGSe electrodeposition routes; recent advancements in the electroplating procedures and the reported power conversion efficiency has been briefed in this section; and (5) CdS-free buffer layers; the attempts that are being made and explored to replace this layer to avoid the involvement of hazardous chemicals have been cited in this section.

CISe/CIGSe material properties and device structure

The intermixing of ternary CuInSe2 (CISe) and CuGaSe2 (CGSe) of I–III–VI group (I = Cu, III = In, Ga and VI = Se) crystallizes to form a quaternary CuInGaSe2 tetragonal chalcopyrite structure, where the In and Ga atoms share the same atomic sites. The crystal structure of CIGSe chalcopyrite material is shown in Fig. 1a [13]. The crystal structure can be realized as a doubled unit cell of zinc blend structure with alternating Cu and In atoms [15]. Each of the Cu or In atoms are bonded tetragonally with four Se anion atom, whereas each of the Se atoms are coordinated with 2 Cu and 2 In atoms. As the bond strength existing between the I–VI and III–VI is different, the lattice constants (c, a, where ‘a’ is base dimension and ‘c’ is cell height) are not always of the desired value 2:1 (c/a ratio), which may lead to lattice distortion [16]. The magnitude of distortion can be realized from the deviation of (c/a) value from 2:1. For a pure CuInSe2, the ratio is close to 2. However, due to the substitution of In by Ga atoms, the c/a ratio deviates towards lower values along with grain refinement, as shown in Fig. 1b [14].

Now, concentrating on the band structure, the valance band of the CIGSe is derived from the weak Cu–Se bond group (I–VI) due to the hybridization of Cu-d and Se-p orbitals. The bottom of the conduction band (CB) is mainly contributed from the In and Ga atoms (group III—S orbital) [17]. Chalcopyrite-based absorber materials are direct band-gap semiconductor with an optical absorption coefficient of α = 105 cm−1 which makes them a suitable candidate as p-type ‘absorber’ layers in thin-film solar cells. The Cu-poor CIGSe chalcopyrite absorber (with a composition of [Cu/In + Ga] or CGI ratio is < 1 and [Ga/In + Ga] or GGI ratio ≈ 0.25–0.35]) contains a large number of defects, most likely the Cu vacancies (VCu) and InCu or GaCu anti-sites [18, 19]. In the Cu-poor CIGSe, the In2+ Cu anti-sites pair easily with \(2{\text{V}}^{ - } \,_{\text{Cu}}\) in the Cu-poor CIGSe to form (\(2{\text{V}}^{ - } \,_{\text{Cu}} + {\text{In}}^{2 + } \,_{\text{Cu}}\)) neutral defect complex [20]. However, the presence of small excess of shallow acceptor like VCu vacancies (energy position close to the valance band) contributes to the intrinsic p-type doping of the CIGSe absorbers. The (\(2{\text{V}}^{ - } \,_{\text{Cu}} + {\text{In}}^{2 + } \,_{\text{Cu}}\)) neutral defects complex with an average composition of Cu2In4Se7,CuIn3Se5,CuIn5Se8, etc., is known as the ordered vacancy compounds (OVC) [21]. The existence of the OVCs in the CIGSe absorber is anticipated at the interface of CdS/CISe thin films. The structure of the OVC layers can be derived as the chalcopyrite structure with randomly introduced copper vacancies or (\(2{\text{V}}^{ - } \,_{\text{Cu}} + {\text{In}}^{2 + } \,_{\text{Cu}}\)) defect pairs and is assumed to be beneficial for the device performance [22]. However, increased OVC content in CIGSe may deteriorate the open-circuit voltage (VOC) of the device due to the formation of excess Cu-deficiency-related defects such as Ga on Cu (InCu or GaCu) anti-sites [23]. These deep electron traps (InCu, GaCu, and its complex-DX centers) limits VOC of the devices through fermi level pinning [24,25,26]. Other defects such as copper interstitial (Ci), selenium vacancies (VSe), and (VSe–InCu) di-vacancy defect complex are considered as origin of metastable-related effects such as persistent photoconductivity (PPC) and red–blue illuminations. During electrical bias or illumination, this di-vacancy complex (VSe–VCu) can shift from a donor into an acceptor configuration in p-type CIGS, increasing the hole concentration and thus acts as a recombination channel for the minority charge carriers (electrons) [27, 28]. The prevalence of these intrinsic defects and compensations is considered to be the origin of potential fluctuations in the material.

The schematic of the state-of-the-art CIGSe device structure as Mo/CIGSe/CdS/i-ZnO/Al–ZnO with the corresponding band diagram of the device is shown in Fig. 2a. These devices have reported maximum reported efficiency (η) of 21% [29]. The working principle of the device is followed after a brief introduction of the structure and properties of the individual layers along with advancements.

Owing to the high bandgap and optical transparency, aluminum doped ZnO, as the front contact TCO layer, ensures maximum light incoming to the device. The sputtered i-ZnO/ZnO:Al layers are classically used as the window/front TCO layers in high-efficiency devices. With an optical bandgap of Eg = 3.3 eV, ZnO is considered to be the promising TCO, as it is cheap, earth-abundant, and non-toxic [30]. It has been reported that the devices with i-ZnO window layers exhibit good stability towards the damp-heat stress. In addition, the buffer/window i-ZnO/CdS combination mitigates electrical shunt paths in the devices by covering the local inhomogeneity in the CIGSe absorber [31, 32]. Until date, most of the widely reported high-efficiency CIGSe devices have utilized cadmium sulfide (CdS) as the buffer layer component [9]. The CdS (Eg = 2.4 eV) buffer material transmits the light up to the wavelength of 2.4 eV to the P-CIGSe absorber.

According to Nakada [33], the Cu-poor surface at CIGSe is favorable for the substitution of Cd ions on Cu vacancies (CdCu+ donor defects) [34] due to the closest matching atomic radii of Cu+ (0.96 Å) and Cd+ (0.97 Å) [35]. The infiltrated Cd in the absorber inhomogeneity acts as a buried CIGSe/CdS homo-junction [36]. Thus, Cd doping at the CIGSe/CdS grain boundaries and conductivity inversion of the absorber from p- to n-types is inevitable. Other significant observations such as Se–S exchange within CdS–CIGSe, Cd diffusion in CIGSe, Cu–Cd interdiffusion at CdS/CIGSe interface, alkali–oxygen (Na–O) impurity accumulations at the interface, Cu2−xSe secondary phase, and Cd–Se formations are also reported [36,37,38,39]. However, the CdS/CIGSe junction interface study is still a debatable research topic which needs further clarifications.

For substrate configuration CIGSe devices (Fig. 2a), the light entering through the metal grid spacing and TCO (Al:ZnO/i-ZnO) may suffer reflection loss due to difference in the refractive index (n). These reflection losses can be minimized by employing anti-reflective coating such as MgF2 [30]. The operation of the devices can be explained on the principle that upon illumination, the generated electron–hole pair is swept away by the built-in electric field at the CdS/CIGSe heterojunction interface towards the respective contacts to produce photocurrent. Some of the electrons can also move towards the wrong contact (back contact) and recombine. This can be avoided by introducing a back surface field, an additional energy barrier for preventing the electron back flow. The band-gap gradient can be achieved by varying the GGI ratio. Figure 2b shows the energy-band diagram of CIGSe device with (dotted), without double grading (continuous line) and the energy-band-gap profile of the CIGS absorber layer used in simulation is given in Fig. 2b, inset. The experimental and simulation studies have shown that double grading in the CIGS absorber layer has greatly improved the performance of single-junction CIGS cells [40, 41]. For detailed information on grading schemes and their benefits in device performance, the readers can refer the cited literatures [42,43,44].

Until date, all high-efficiency devices reported so far are of low band-gap (1.15 eV—CuIn0.7Ga0.3Se2) values with Cu-poor composition in the final device stage having a GGI ratio of 0.3–0.35 and CGI ratio of 0.8–0.9. A slightest increase in the Cu content is considered to be Cu-rich (≥ 25% of at wt%) as the excess Cu content reacts to form Cu–Se secondary phase, which are detrimental to the device performance [46]. Hence, Cu-rich stoichiometry refers to the overall Cu content including Cu–Se secondary phase in the absorber. Though Cu-rich absorbers exhibits better crystallinity, low defect concentrations, less bulk recombination, and high mobility, they exhibited poor efficiency than Cu-poor devices [47]. For improving the Cu-rich device performance, the excess Cu x Se phase can be removed by selective etching using potassium cyanide (KCN) [48]. The interface recombination problems which is prevalent in Cu-rich CISe devices can be eliminated by controlling the doping level. Through simulation studies (Fig. 3), it has been realized that low doping levels (Na = 1016 cm3) can increase the recombination barrier existing between the fermi level (EF) and valance band edge reduces the tunnel assisted recombination at the interface. The doping level of Cu-rich devices can be controlled by the Se flux. In contrast to the Cu-poor CISe device, Cu-rich device exhibited better efficiency of η = 8.6% under low Se flux conditions, whereas η = 6.2% at very high Se flux conditions [49]. Furthermore, by depositing a thin In–Se layer, the device efficiency of 13.1% was achieved. Such treatment recovers the open-circuit voltage loss by reducing the interface recombination [50]. These results are promising in the context that compositionally altered Cu-rich devices have the potential to compete in terms of efficiency to the Cu-poor ones.

Permission granted by the authors to reuse the figure, Copyright© 2013 Society of Photo-optical Instrumentation Engineers (SPIE) [45]

Simulated energy-band model of a Cu-poor (red) and a Cu-rich (blue) CuInSe2 solar cell (higher doping of the Cu-rich absorber is assumed). The horizontal arrow indicates the tunnel recombination process due to high doping levels.

In the future, compositionally altered Cu-rich absorbers may be a major theme of study in the development of CIGSe absorbers. Moreover, mimicking such studies in electrochemical route is much easier when compared to vacuum deposition techniques. A detailed recent review on the progress in CIGSe solar cells defects mechanisms and the state-of-the-art CIGSe devices have been discussed in the cited literature [51, 52].

Experimental concerns in CIGSe electrodeposition

Irrespective of synthesis route, generally, the CIGSe/CISe absorber deposition is carried out by two ways (1) simultaneous deposition and selenization/sulfurization and (2) precursor deposition followed by sequential selenization/sulfurization. The vacuum-based deposition techniques mostly follow the simultaneous selenization and other processes like electrodeposition, roll-to-roll printing, Ink/paste precursor coating follow the sequential selenization. Regardless of deposition techniques employed in thin film CIGSe/CISe fabrication, the ultimate goal of every route is to prepare a compositional film exhibiting good crystallinity leading to a material with good photovoltaic characteristics.

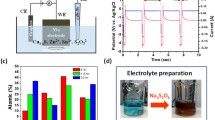

Electrodeposition is a non-vacuum technique in which the electro-reduction of ions at particular reduction potential takes place over a conductive substrate to form thin films by the influence of applied electric field. The equilibrium reduction potential (in Fig. 5) of Cu, In, Ga, and Se ions in the EMF series is + 0.337/SHE, − 0.342/SHE, − 0.529/SHE, and + 0.741/SHE, respectively. The difficultness arises during electrodeposition of CIGSe is due to the active standard reduction potential of In and Ga ions. Though increasing the concentrations of In(III) and Ga(III) shifts the potential closer to Cu(II) [53], excessive currents generated due to high bath concentrations may cause significant pitting and corrosion of Mo/glass substrates [54]. Recent impedance studies by Saji et al. also verified that excessive In ions can interact or complex with Mo/surface oxides and that in effect can cause a certain extent of Mo dissolution [55]. Electrodeposition at high cathodic potential conditions affects the In and Ga plating efficiency due to the parallel occurrence of hydrogen evolution, which is considered to be the origin for film inhomogeneity and pin holes formation. This makes electrodeposition of stoichiometric and pinhole free CIGSe thin films even more challenging. This shortfall arised as an attempt for the controlled inclusion of In(III) and Ga(III) ions can be taken care by adding complexing agents. Complexing agents can play a major role in shifting the reduction potential of noble ions (Cu) towards active ions (In, Ga), hence making the co-deposition easier. These agents diminish hydrogen generation avoid pinholes and improve the compactness of the as-deposited film. Other additives such as supporting electrolytes, surfactants, and brighteners are often used for improving the bath chemistry and film quality. However, most complexing agents have no effect on In (III) and Ga (III) ions and forms strong complex only with copper and selenium ions [10].

Hence, in the following sections, attention has been given towards significant recent advancements in the electrolyte chemistry for the controlled inclusion of In3+ and Ga3+ ions in CISe/CIGSe thin films both in aqueous- and non-aqueous-based electrolytic deposition conditions.

CISe/CIGSe electrodeposition using aqueous electrolytes and complexing agents

Bhattacharya et al. group was the first to report single-step electrodeposition of CISe thin films using triethanol amine (TEA) as complexing agents [56]. Since then, several works on electrodeposition of CISe/CIGSe using TEA have been reported as it can form strong complexes with Cu2+ and HSeO2– ions and weak complexing with the In3+ ions [57]. Calixto et al. reported the electrodeposition of pinhole free stoichiometric CIGSe using low concentrations of 2.56 mM Cu2+, 2.40 mM In3+, 5.7 mM Ga3+, and 4.5 mM Se4+ ions in the bath at a pH of 2.5. The electrolyte was stabilized using a buffer of pH 3 (pHydrion mixture of sulphamic acid and potassium biphthalate) along with LiCl as supporting electrolyte [55]. Recent works by Liu et al. have suggested that by increasing the sodium sulfamate concentration, (Cu + Se)/(In + Ga) decreases, while gallium content increases and the film composition transforms from Cu rich to Cu poor [58]. Using KCN− as the complexing agent, the reduction potential difference between of Cu2+ and Ga3+ was only 80 mV, whereas 870 mV difference for un-complexed (Cu,Ga) species [59]. At high thiocyanate complex concentrations, the predominant species is Cu (I) in soluble form. Furthermore, the reduction of Ga can get catalyzed in the presence of thiocyanate (CNS−) ions. This makes thiocyanate a suitable complexing agent in CIGSe/CGSe electroplating [60].

Using potassium sodium tartrate as complexing agent for In and trisodium citrate for Ga ions, Aksu et al. were able to electroplate In–Se and Ga–Se thin films even at high alkaline conditions. For In–Se, the plating efficiency of 68% was obtained at a pH of 13. For Ga–Se complexed with trisodium citrate, below the pH of 5, the Se percentage was dominated, and at high pH of 13.5, Ga was dominant. They were able to co-deposit Ga–Se films within the pH window of 7–8.5 [61]. The same group could co-deposit Cu–In–Ga alloy at alkaline conditions (9–13.5) using blends of complexing agents for solubilizing and preventing hydroxide formation of ions at such high alkaline conditions. Though the processing conditions were not disclosed, common chelating agents such as TEA, EDTA, citric acid or trisodium citrate, potassium sodium tartrate, and tartaric acid can be used as they have the tendency to form complexes with Cu, In, and Ga ions. The grading of Ga is also possible by modulating the current density during electroplating [62].

An interesting alternative route for the inclusion of In (III) and Ga (III) is in the form of oxides/hydroxides using respective nitrate salts as reported by Duchatelet et al. [63]. During the process, the reduction of indium and gallium takes place as two simultaneous steps involving nitrate reduction and oxides precipitation. During the nitrate reduction, the consumption of proton will induce a local change in pH at the vicinity of the cathode followed by In and Ga depositions in the form of precipitated oxides or hydroxide. As shown in the standard deposition potential diagram (Fig. 4), deposition of In and Ga in the form of oxides/hydroxides takes place at very low cathodic potential compared to the Cu–In–Ga electrodeposition using conventional chloride/sulfate electrolytes. The crystalline CIGSe absorber deposited and after subsequent H2 reduction and selenization pre-treatment (in Fig. 5a–c) revealed a power conversion efficiency of η = 9.4% [64].

Reprinted with permission from Duchatelet et al. [63]. Copyright 2014, The Electrochemical Society

Comparative diagram of the standard deposition potentials of copper, indium and gallium in the form of metals or hydroxide/oxide during nitrate reduction.

Reprinted from Duchatelet et al. [64], with the permission of AIP Publishing, Copyright©2013 AIP

SEM cross-sectional pictures of as-electrodeposited Cu–In–Ga mixed oxide precursor films (a), after reduction under Ar-5% H2 into metallic alloy (b), and after selenization and front contact layers deposition (c).

Yang et al. reported on the controlled Ga(III) inclusion using hydrogen peroxide (H2O2) as the oxygen precursor facilitating the Ga incorporation in the form of Ga(OH)3 [65]. The reduction starts with the cupric ion followed by the reduction of H2O2 which facilitates the inclusion of In and Ga in the form of oxides/hydroxides. Precipitations of In and Ga were observed for higher concentration of H2O2 (20 mM) for which the deposition takes place by a controlled mass transfer of the hydroxide species [66].

Without any complexing agents and supporting electrolytes, Chaure et al. reported the possibility to electrodeposit CISe (p, i, and n-type) [67] and CIGSe (p+, p, i, n, and n+) [68] by varying the deposition potential from the same bath. The major hindrance in using the aqueous electrolytes is the abrupt changes in the (Ga/III) ratio, as even for a slight change in the deposition, potential can alter the composition and thus the deposition mechanism [69]. Hence, the morphology of the as-deposited film is strongly dependent on the applied deposition potential. As shown in Fig. 4, the narrow deposition potential window is often difficult to balance the film composition and quality. Moreover, tuning the (Ga/III) ratio is possible up to a certain extent beyond which the parallel occurrence of hydrogen evolution reaction (HER) takes place and has negative impact on the film quality such as formation of pinholes and dendritic morphology [70]. However, the metal-oxide/hydroxide depositions are more promising, where the problem of hydroxide formation during the conventional CuInGa electrodeposition is taken as an advantage. The difficultness of Ga inclusion in conventional CuInGa plating can be easily overcome by metal-oxide/hydroxide depositions.

The recent advancements in electrolyte chemistry in the CIGSe depositions such as (1) complexing agent blends, (2) nitrate precursor, and (3) hydrogen peroxide source are promising as the problem of Ga inclusion can be avoided easily when compared to conventional deposition schemes. Further studies pertaining to the electrolyte stability and replenishment of ions or reusing the electrolytes may contribute towards the cost-effective industrial-scale deposition.

CISe/CIGSe electrodeposition in non-aqueous electrolytes

The HER interference can be overcome using non-aqueous electrolytes without complexing agents such as ionic liquids [71], ethylene glycol [72], and alcohol or alcohol/ionic liquid combinations [73]. Long et al. reported electrodeposition of compact and quality CIGSe thin films at − 1.6 V/SCE using alcohol and LiCl electrolyte (pH 1.9–2.2) [74]. Availability of such wide electrochemical deposition window in non-aqueous electrolytes allows electrodeposition of In (III) and Ga(III) ions conveniently.

Electrodeposition using ionic liquids has gained attention due to their advantages like biocompatibility, non-toxic, cost-effectiveness, and wide electrochemical potential window that make them a suitable electrolyte to electrodeposit elements which are difficult to plate in conventional aqueous bath conditions. Especially, choline chloride (ChCl)-based ionic liquids and aprotic deep eutectic solvents (DES) have emerged as an efficient replacement for conventional ionic liquids and volatile organic solvents. A mixture of choline chloride/urea (ChCl/U—1/2) termed reline is one of the popular DES used in CIGSe electrodeposition. Unlike aqueous electrolytes (where the metal ions solubility is limited by oxides/hydroxides precipitation), high solubility, and ligand concentrations can be achieved in water-free ionic liquids. Moreover, the high ligand concentrations ensure greater control on the metal speciation in the electrolyte [76, 77]. Therefore, reline forms strong metal complexes with the ions, and hence, the necessity of using complexing agents is eliminated. Reline is highly stable and does not decompose even after prolonged heating conditions. By lowering the viscosity (η) of the reline, better mass transport properties of the ions can be achieved. For this reason, the optimal bath temperature during electroplating is usually maintained within 60–70 °C.

Harati et al. was the first to report the one-step electrodeposition of quaternary CIGSe thin film using reline. The deposition temperature was fixed to 65 °C [71]. Steichen et al. reported the electrodeposition of Cu–Ga thin films using reline at 60 °C. The selenized CuGaSe2 PV devices (processed at 550 °C in Se atmosphere) achieved 4.1% total-area power conversion efficiency. When only Ga or In–Ga thin films were electrodeposited on Mo substrates, no alloying phenomena are observed and the obtained films were found to be physical mixtures of In–Ga in the form of droplets (Fig. 6a). However, for Mo/Cu substrates, an improvement in the Cu–Ga films film adhesion (Fig. 6b) was observed due to the CuGa2 alloy formation [75]. Zhang et al. reported CIGSe device efficiency of 10.1% for pulse electrodeposited CIG alloy. The selenization (using Se powder) was carried by rapid thermal annealing (RTA) at 550 °C for 1 h. in the Ar atmosphere [78]. Malaquias et al. showed the possibility to alter the [Ga/In] ratio from 0 to 1 by adjusting the electrolyte flux ratio of [Ga3+/In3+] ions [79]. The same group reported an efficiency of 9.8% for CIGSSe thin films. The electrodeposition of In–Ga thin film was performed over the Mo/Cu thin films followed by a three-step annealing process (H2Se, Argon, and H2S) [80].

Adapted from Steichen et al. [75] with permission of The Royal Society of Chemistry

a Cross-sectional images of metallic Ga droplets electrodeposited on Mo from Reline–GaCl3 50 mM at 1.1 V/Ag for 30 min at 60 °C, b SEM top-view of a Ga deposit on Mo/Cu from Reline–GaCl3 50 mM at 0.9 V for 15 min at 60 °C.

Electrodeposition of CuGaSe2 thin films

We have also reviewed the approaches for electrodeposition of wide band-gap absorber CGSe thin films. Electroplating of CGSe is more difficult due to the standard potential (− 0.53 V SHE) of gallium. The parallel occurrence of HER hinders the electrodeposition process hence resulting in films with poor morphology and pin holes. Table 1 gives the deposition parameters for one-step deposition technique of CGSe thin films.

Until date, thiocyanate (KCN−) is reported to be a suitable complexing agent for single-step electrodeposition of CuGaSe2 films. The shift in the reduction potential of Cu towards the lower cathodic potential makes assimilation of Ga3+ ions easier in the form of Ga2Se3 to the growing of CuGaSe2 film. Oda et al. reported crack free CGS thin films with lithium sulfate (Li2SO4) and gelatin [82]. Using DES such as reline, successful electrodeposition of CGSe has been reported [75]. Electrodeposition of Cu–Ga alloy using copper–gallium nitrate salts is also a good approach, where the inclusion of Ga takes place in the form of oxides/hydroxides [63].

Strategies for improving the quality of electrodeposited CIGSe thin films

For an industrial-scale production of electrodeposited CIGSe, the thin films should be free from voids, cracks, surface, and compositional inhomogeneities. In this section, we have discussed some of the reported experimental approaches for improving the quality of the CIGSe absorbers for the high-performance devices.

Pre-treatment (PT) process

Calixto et al. reported the significance of the pre-treatment process in CIGSe electrodeposition [54]. In their observation, for CIGSe thin films deposited without PT exhibited (Fig. 7a) pinholes, micro-cracks, and secondary Cu–Se phase which were avoided by carrying out pre-treatment before deposition (Fig. 7b). Similar process was adopted for CISe electrodeposition (4 mM—Cu2+, 9.75 mM—In3+, 6 mM—Se4+, 0.4 M citric acid and 0.35 g sodium dodecyl sulfate, − 0.6 V/SCE for 20 min, and PT at − 0.5 V/SCE for 1 min over FTO substrates) to understand the effect of PT. For CISe without PT, the surface nonuniformties, cracks and pinholes were present, as shown in Fig. 7c, which was reduced after PT (Fig. 7d). In addition to this, the surface without PT was found to have In nano-islands which may affect the efficiency of the devices. Whereas the micro-structural studies revealed the presence of uniform particle morphology with reduced In-nano-islands for PT–CISe. Hence, this would help in maintaining the composition throughout the film. Though the exact role of pre-treatment have not been studied extensively, it has certain influence in altering the deposition mechanism during the single-step deposition and hence the film quality. The pre-treatment process seems to be applicable to all baths; however, further investigation is required to understand its role and mechanism in morphological and compositional changes. The homogenized distribution of In and Ga seems to be possible by this pre-treatment process.

Reprinted with permission from Calixto et al. [54]. Copyright 2006, The Electrochemical Society

a SEM cross section of CIGSe electrodeposition without (a) and with PT (b), FE-SEM of CISe electrodeposited without pre-treatment, photographic image (c, e) and (d, f) with pre-treatment (original work).

Compositional tuning to avoid micro-cracks

The studies related to the interdependence of CIGSe film quality and stoichiometry with respect to the bath composition was reported by Bhattacharya et al., as shown in Fig. 8 [84]. For a diffusion controlled deposition process, CIGSe films deposited using low Cu2+ and In3+ bath concentration exhibited micro-cracks. Micro-crack-free CIGSe precursor films were obtained when electrodeposited at low Se4+ and high Cu2+, In3+, and Ga3+ bath concentrations. Moreover, the composition of CIGSe can also be controlled by tuning the specific ion concentration.

Reprinted from Fernandez et al. [84]. Copyright (2003) with permission from Elsevier

Composition variation of CIGSe as a function of Cu, In, Ga and Se ions concentration.

For increased Cu2+ concentration, Cu content was found to be increasing and Se decreased. With the increase in In3+ concentration, In content increases steadily and Ga was found to be decreased. Cu and Se contents were found to be unaffected by In3+ concentration. All the ions are found to be unaffected towards the Ga3+ ions at lower concentration. At high Ga3+, a steady increase in Cu and In, and decrease in Ga, Se content was observed. For Se4+, Cu and In contents decrease steeply, while Ga and Se contents increase.

Selenization/sulfurization of electrodeposited CISe/CIGSe absorbers

Apart from electrodeposition parameters, the final device efficiencies are highly influenced by the post-processing annealing steps such as selenization and sulfurization. The post-processing annealing schemes follow either a conventional furnace annealing (slow or fast heating rate/prolonged annealing time) and rapid thermal processing (fast heating rate for a short annealing time) in H2Se/selenium/sulfur/Ar/N2/vacuum atmospheres. The simplest post-processing annealing scheme is annealing the CIGSe absorber in vacuum or Ar or N2 atmosphere. However, the major drawback encountered during Ar and N2 annealing is the Se loss. Some of the literatures have reported the retainment of Se in CISe successfully even after annealing at 400 °C in argon atmosphere for 30 min [85]. Frontini et al. reported the diode characteristics behavior of electrodeposited CISe annealed at 350 °C for 15 min in Ar atmosphere [86]. Hamrouni et al. reported vacuum annealing of electrodeposited CuInSe2 at 400 °C. The CISe absorber of a bandgap 1.2 eV exhibited a rectifying behavior for the FTO/CISe/Al device structure [87]. Bamiduro et al. reported an Se loss of 1 at.wt % for the CIGSe films annealed at 300 °C in argon atmosphere [88]. For a pulse electrodeposited CIGSe films, Mandati et al. reported a stoichiometric CIGSe films after annealing at 550 °C for 30 min in Ar atmosphere [89]. As the device performance has not been studied for the N2 or Ar annealed CISe/CIGSe absorbers, it will be too early to conclude its benefits. A systematical study in this regard is required as it has the potential to reduce the device fabrication cost by eliminating the sulfurization/selenization steps.

The most common annealing treatment is selenization using either H2Se gas or Se powder in a controlled atmosphere. However, due to the toxic nature of the H2Se gas, the selenization using elemental Se powder is more preferable. During the annealing of CuInGaSe2, the binary selenides of Cu and In are formed initially followed by the formation of CuInSe2 phase between the temperature ranges of 370–380 °C. The formation of CuGaSe2 phase is induced only around 425 °C. A complete single-phase CIGSe is formed by the slow interdiffusion between CISe and CGSe at high temperature along with the Ga accumulation towards the back contact. The problem of Ga segregation towards the back contact in the CIGSe absorbers during selenization process is widely reported [90]. They tend to create an insufficient energy bandgap at the SCR, which leads to poor VOC. Studies by Mardudachalam et al. revealed that the accumulation of more Ga towards the back contact (Mo) takes place as a consequence of preferential reaction between In with H2Se than Ga [91]. During high-temperature selenization, the CIGSe/Mo heterocontact inverts from Schottky to a favorable Ohmic-type contact due to the formation of thin MoSe2 layer. Moreover, the formation of thin MoSe2 layer contributes towards the improvement of the adhesion at the CIGSe/Mo interface [92]. Yet, a high series resistance (Rs) is induced when the MoSe2 layer is too thick which can deteriorate the fill factor (FF) and VOC of the CIGSe devices [93].

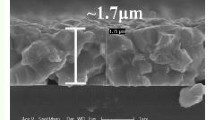

An extensive studies on the interdiffusion and phase formation of electrodeposited Cu/In, Cu/Ga, Cu/(In + Ga) stacks by Oliva et al., suggested that better incorporation/distribution of gallium in electrodeposited CIGSe precursor can be achieved through longer annealing time or a higher annealing temperature [94]. Ribeaucourt et al. reported an efficiency of 9.3% for an electrodeposited CuInGa alloy selenized at 450 °C. However, for CIGSe selenized at 600 °C, the obtained efficiency was only 4%. The MoSe2 layer thickness was found to be 1 µm and 500 nm thick for CIGSe selenized at 600 °C and 450 °C for 45 min. In both the conditions, the Ga accumulation towards the back contact was inevitable [70]. The same group reported an efficiency of 12.4% for CuInGa oxide precursor layer alloys after subsequent reduction (H2 atmosphere at 500-550 °C) and selenization at 550–600 °C for 45 min [95]. Bhattacharya et al. reported an efficiency of 11.7 and 10.9% for a stacked Cu/In/Ga and CIGSe/Cu/In precursor layers selenized at 550 °C for 45 min [96, 97]. Başol et al. reported a total-area efficiency of 13.76% for a 0.48 cm2 device, 12.5% for cells with area of 120 cm2, and 10% for a 1.07 m2 module exhibiting a total output of 107.5 W (Vm = 38.2 V and Im = 2.8 A) on flexible stainless steel (SS) substrates [98]. They also have reported a certified efficiency of 14% for 12 cm2 and 15.36% for 5.4 cm2 over flexible SS substrates. A record efficiency of 13.4% for flexible CIGS module for a device dimension of 147.1 × 26 cm2 by roll-to-roll electrodeposition was also reported [99]. Though the details of post-processing were not disclosed, they have mentioned that the devices were prepared from the electroplated metal stacked layers of Mo/Cu–In–Ga/In–Se or Ga–Se followed by rapid thermal annealing (RTA) at 500 °C. Similarly, NEXCIS also reported a record efficiency of 14% for a of 60 × 120 cm2 modules for Cu(In,Ga)(S,Se)2 solar cells. The electrodeposited Cu–In–Ga stacks were successively selenized and sulfurized between 500 and 550 °C [100]. Duchatelet et al. reported an efficiency of 8.7% for a 370 nm-thick CIGSe thin films by electrodeposition of Cu/In/Ga stacks. The as-deposited CuInGa precursor thickness was around 120 nm. Upon selenization at 550 °C for 15 min, they observed an increased VOC of 865 mV which was higher than the standard CIGSe (2100 nm) exhibiting VOC of 605 mV (η = 12.6%). The accumulated Ga in ultra-thin CIGSe devices played the role of back surface field and inhibited the electron recombination at the back contact [101].

Malaquias et al. reported an efficiency of 9.8% for electrodeposited CuInGa alloys with reduced Ga accumulation by employing a three-step annealing process [80]. To explain the impact of three-step annealing process, the work by Kim et al. has been explained below [102]. The three-step annealing process of vacuum-deposited CuInGa metal precursor involves (1) selenization in H2Se at 400 °C for 60 min, (2) annealing in Ar at 550 °C for 20 min, and (3) sulfization in H2S at 550 °C for 10 min. From the AES studies (in Fig. 9a–c), the sputter deposited CIGSe selenized samples were stoichiometric at the surface and Ga/Cu–Ga intermetallic rich at the back contact. However, the homogenization of In and Ga was observed after the Ar and H2S post-heat treatments. As shown in Fig. 9a–c (SEM cross-sectional images), an improvement in the CIGSe micro-structure (vacuum-based deposition) was observed followed by the disappearance of flat voids only after the Ar and H2S treatment. Bi et al. reported an efficiency of 11.04% of CIGSe thin films for the electrodeposited metal stacks of Cu/In/Ga annealed in three steps: (1) selenization at 400 °C for 10 min; (2) N2 for 30 min at 580 °C; and (3) selenization at 580 °C for 15 min [103].

Reprinted from Kim et al. [102] with the permission of AIP Publishing

Compositional depth profiles determined by AES of the reacted CIGSe (or CIGSeS) films after a H2Se (400 °C for 60 min), b Ar (550 °C for 20 min) and c H2S (550 °C for 10 min) and corresponding cross-sectional SEM images of reacted CIGSe or CIGSeS films after a 1st step, b 2nd step, and c 3rd step.

Apart from rapid thermal annealing schemes, three-step annealing is beneficial as during the N2 annealing, a slow interdiffusion step between CuInSe2 and CuGaSe2 is possible which ensures the homogenization In and Ga. Furthermore, the third selenization step avoids the formation of secondary phase at the surface.

Electrochemical formation mechanism of CISe/CIGSe

The formation mechanism of CIGSe is complex due to the involvement of multiple electrochemical and chemical reactions that takes place simultaneously during the quaternary CIGSe deposition. In the recent years, the deposition mechanism of CIGSe has been explained satisfactorily by several research groups. Here, we have summarized the significant results which complete the understanding of the deposition mechanism.

According to Mishra and Rajeshwar, the formation of CuSe binary phase occurs at the first place through underpotential deposition onto the previously reduced Cu from Cu2+ ions. Though Se is nobler than Cu, the formation of Se (IV) to Se (0) is sluggish, and hence, the initial formation of Cu is highly necessary for the direct reduction of Se(IV) [104]. During the initial stage of deposition, the formation of Cu nano-nuclei over the Mo substrates allows the incorporation of Se (0) to form Cu x Se binary phase. Moreover, the growth of Cu x Se phase can easily take place over molybdenum even at open-circuit potential.

Figure 10a shows the Raman spectra of Cu–Se films immersed for different periods at OCP conditions. Irrespective of the immersion time, no peak corresponding to Se (254 cm−1) was observed. Only characteristic Raman peaks corresponding to Cu3Se2 (106, 141, 197, and 216 cm−1) and Cu2Se (261 cm−1) were observed [105]. Hence, at lower cathodic potential, Cu–Se binary co-exists as mixtures of Cu3Se2, Cu2Se, CuSe, and Se(0) [107, 108]. For increased over potential, the direct reduction of Se(IV) to elemental Se(0) takes place over CuSe platelets, as shown in Fig. 10b. However, after selective dissolution of elemental Se, the atomic ratio of CuSe platelets [Se/Cu] was found to be close to unity (Fig. 10c) [106]. Increased Se concentration (over CuSe platelets) contributes to the formation of CuSe2 phase. CuSe2 can further reduce to form Cu2+ and H2Se at higher cathodic potentials which chemically react with H2Se to form a non-adherent Cu2Se particles dispersing back to the electrolyte [85]. This reaction is the key for the In3+ and Ga3+ incorporations as the In and Ga ions can react chemically with H2Se to form their respective selenides.

a Raman spectra of CuSe films obtained after immersion at OCP in Cu(II)–Se(IV) solutions (pH 2.2) (reprinted with permission from Ramdani et al. [105] Copyright 2007, The Electrochemical Society), b SEM of as-deposited Cu–Se at V = − 0.55 V/MSE, [Se/Cu] = 1.9, [In/Cu] = 0 and c SEM of Cu–Se after stripping in Na2S, [Se/Cu] = 0.95 (reprinted with permission from Chassaing et al. [106], Copyright© 2008 John Wiley and Sons)

The Indium incorporation at low cathodic potential has already been reported in several literatures. Kemell et al. reported that CuSe phase enables the incorporation of In3+ ions by induced co-deposition process [110]. Chassaing and co-workers reported that In3+ inclusion takes place when the [Se/Cu] ratio is greater than 1 to form CuInSe2. Excess selenium over CuSe phase is a perquisite of the indium incorporation at lower cathodic potential [106]. However, the inclusion of In through such surface-induced reactions (at lower cathodic potential) is often limited which is ascribed to the increased electrical resistance of the surface due to poor reacting nature of Se(0) species [111]. At higher cathodic potential conditions, the formed Se(–II) species chemically reacts with In3+ to form indium selenides (In2Se3) and assimilates to the growing CuInSe2 film. In3+ can also reduce directly to form In(0) at high precursor concentrations and deposition potential conditions. Figure 11a shows Raman spectra of as-electrodeposited CISe of thickness 2 µm. The presence of Cu-deficient CISe phase (160 cm−1) commonly known as OVC, A1 mode of CISe (177 cm−1), and elemental Se(0) (260 cm−1) can be observed. The peak at 260 cm−1 corresponds to the conductive Cu2Se phase [107].

a Raman spectra of electrodeposited CuInSe2 thin film (2 µm) (reprinted with permission, Roussel [107], Copyright 2007, The Electrochemical Society), b Raman spectra of CuGaSe2 (as-deposited and annealed) (reprinted from Liu et al. [81], Copyright (2012), with permission from Elsevier), c Raman spectra of CuInGaSe2 (as-deposited and annealed) (reprinted with permission, Lai et al. [109], Copyright 2011, The Electrochemical Society)

For CuGaSe2 or CuInGaSe2, the Ga inclusion in the as-deposited CIGSe films mainly depends on the applied potential. Unlike indium, such surface-induced reactions of In(III) ions with Cu x Se phase are not found for Ga species. The inclusion of Ga takes place either in the form of Ga(OH)3 (due to the local change in pH) [112] and Ga2Se3 (reaction with H2Se) at lower or higher cathodic potential, respectively. Further increase in deposition potential usually may lead to formation of gallium oxides and hydroxide due to the parallel occurrence of HER [81]. So far, there is no direct evidence for the assimilation of CuGaSe2 or Ga2Se3 species with CuInSe2 or In2Se3 forming CIGSe thin film. For as-deposited CGSe films, Liu et al. reported the absence of Raman peaks (Fig. 11b) corresponding to CuGaSe2 (184 cm−1) or Ga2Se3 (155 cm−1) peaks, instead only peaks corresponding to CuSe (255 and 263 cm−1) and elemental Se (238 cm−1) were observed. Lai et al. also reported the appearance of CIGSe A1 mode (174 cm−1) (Fig. 11c) for as-deposited and for annealed CIGSe thin films at 174 and 176 cm−1, suggesting that the Ga2Se3 phase must be in the dispersed nano-crystalline form which involves in the phase formation only during annealing [109].

The assimilation of In and Ga to the growing CIGSe is only stronger at higher cathodic potential. A judicious bath preparation and deposition potential are necessary to have controlled inclusion of Ga with minimal oxygen content.

CIGSe electrodeposition schemes and device performance

The approaches followed to electrodeposit CIGSe absorber layers can be classified into two routes: (1) by one-step deposition, where co-deposition of all the elements takes place at a single potential followed by post-treatments or (2) by two steps to multi-step depositions to deposit either via binary phase deposition or element by element. The deposition schemes which are already in practice and promising for large area CIGSe thin-film electrodeposition are presented Fig. 11. Irrespective of deposition schemes, a high-temperature annealing between 500 and 600 °C (under sulfur, selenium, or inert atmosphere) is required to enhance crystallinity and alloy formation process.

-

The fabrication route mentioned in Fig. 12a deals with deposition of one-step electrodeposition of Cu–In–Ga layers followed by selenization/sulfurization. Using such scheme, a record efficiency of 17.30% (0.5 cm2) and 14% (60 × 120 cm2) in industrial scale were achieved for CIGSSe devices by NEXCIS [100].

-

Using complexing agents, Başol et al. were able to electrodeposit Cu–In–Ga/In–Se or Ga–Se stacks (Fig. 12b) in alkaline conditions. The reported efficiency for the devices fabricated through this route is of 14.17% (11.8 cm2), 15.36% (5.4 cm2), and 13.4% (1.5 m2). The above-mentioned routes are presently the most efficient regarding the final efficiencies of CIGSe devices [62, 98].

-

Recently, Duchatelet et al. reported (Fig. 12c) an efficiency of 12.4% (0.1 cm2), where Cu–In–Ga are deposited in hydroxide form followed by H2 reduction and selenization [95].

-

In Fig. 12d, for a three-stage electrodeposition of CIGSe/Cu/In metal stacks (selenization at 550 °C), Bhattacharya et al. reported an efficiency of 10.9% for the device area of each cell is ~ 0.42 cm2. They were able to fabricate these devices reproducibly and all nine cells had comparable efficiencies indicating uniform deposition over 12.5 cm2 area [97].

-

For an electrodeposited stacked Cu/In/Ga layers as mentioned in Fig. 12e (selenized at 550 °C), Bhattacharya et al. reported an efficiency of 11.7% [96].

Recently, an efficiency of 11.04% was also reported by Biet al. using the deposition scheme-e. However, the Cu/In/Ga metal stacks were formed by employing a pulse electroplating technique and instead of conventional selenization. They carried out three-step annealing processes: (1) selenization at 400 °C for 10 min; (2) N2 for 30 min at 580 °C; and (3) selenization at 580 °C for 15 min [103].

In the above-mentioned schemes in Fig. 12, the direct current (DC) was employed to deposit CIGSe thin films. The rate determining step in one-step direct current is the charge transfer process. The increased supersaturated growth takes place over the same nucleation sites and hence results in the fine particles in porous/powdery deposits. Apart from DC depositions, there are other different plating techniques which includes pulse plating, pulse reverse plating and cyclic voltammetry techniques by which the secondary phase formation can be minimized [71, 113, 114]. Compared to conventional constant potential deposition techniques, electron charge transfer step is prevented in pulse plating as the deposition diffusion controlled process may lead thin films of large grain size morphology. Such deposition techniques are advantageous as we can have good control over the material composition.

CdS-free buffer layer in CIGSe devices

Until date, most of the reported record efficiency (η > 19%) CIGSe devices employ CdS buffer layer which comprises of the device, as shown in Fig. 13a [29].

The buffer layers play major role in the formation of a favorable heterojunction band alignment (ΔEc = 0–0.4 eV) with CIGSe to provide an unimpeded electron flow. A thin CdS of thickness ≈ 50 nm is so far the most successful and widely buffer layer employed in CIGSe solar cells. This thin layer is deposited by chemical bath deposition (CBD), which incurs huge environmental issues with the toxic chemicals involved in. Hence, on the aspect of mitigating environmental hazards, replacement of hazardous CdS is highly essential. Various alternative buffer layers with higher bandgap than CdS (2.4 eV) [ZnS (3.8 eV), ZnSe (2.7 eV), ZnMgO, In2Se3 (2.7 eV), In2S3 (2.45 eV)] have been synthesized using various wet and dry deposition techniques [115, 116]. The advantageous part is that these materials exhibit larger bandgap than CdS, thus minimizes the absorption loss between the wavelength regions of 350–550 nm. Yet, these materials lack in terms of stability and final efficiency when compared to CdS. Remarkably, CBD grown Zn(O,S)/CIGSe devices exhibited better stability even when subjected to 1000 h damp-heat testing and suffered no severe efficiency losses [117]. CBD is the most successful Zn(O,S) buffer layer deposition technique used in the CIGSe device fabrication. A comparison study by Ramanathan et al. revealed that Zn(O,S) buffer layers deposited by CBD exhibited highest power conversion efficiency (η = 18%) than the sputtered one (η = 13%) [118]. Furthermore, the thermal diffusion of Cd or Zn adatoms at the absorber surface creates donor anti-sites, thus can enhance inversion layer (more n-type). Recent results also indicated that Zn(O,S) with CIGSe functions to be a better substitution for CdS, exhibiting valence (VBO) and conduction band off-set (CBO) of 1.15 ± 0.15 and 0.09 ± 0.20 eV, respectively. The CBO of the hetero interface is sufficiently flat (with a small spike) providing better electron flow and a good blocking layer for the majority carriers and hence reduces the interface recombination. Furthermore, the band-gap tuning is possible in Zn(O,S) buffer layers by varying the [S/S + O] ratio [119, 120]. Even a minimal bandgap of 2.6 eV can be achieved with S/S + O = 45% which is 0.2 eV larger than CdS, thus avoiding the absorption losses. An increased device performance was observed when CIGSe/Zn(O,S) devices are annealed or HLS (heat and light soaked) treatments are performed. These treatments decrease the [S/S + O] composition at the CIGSe/Zn(O,S) interface and helps in the rearrangement of the CBO to be more favorable than the as-deposited Zn(O,S) [121, 122].

These results are encouraging which would pave the way to reduce the toxicity levels in the current CIGSe fabrication techniques.

Conclusion

Electrodeposition is probably one of the mature and scalable non-vacuum-based deposition techniques for CISe/CIGSe absorber layers. This review has provided some of the progresses in electrodeposition of these ternary and quaternary films which essentially covers formation mechanism of the alloys, experimental practices, deposition routes, and alternatives to replace the CdS buffer layer. The significant observations can be listed as mentioned below:

-

Until date, the reported highest efficiency of electrodeposited CIGSe devices is 17.30% in lab scale (0.5 cm2) and 14% in industrial modules (60 × 120 cm2). Though the reported efficiency is comparably less to vacuum-based techniques, electroplating technique is still a very promising technique for a simplified large scale solar cell manufacturing process.

-

The primary concern in electrodeposition is to gain control over the film stoichiometry and compactness. In addition, the current practice adopted by solar industries to fabricate efficient CIGSe modules is by electroplating of single Cu–In–Ga or Cu–In–Ga/In–Se or Ga–Se bi-layer stack deposition followed by selenization/sulfurization in acidic baths. Formation of Cu–In–Ga/Cu–Ga/In–Ga metal stacks in alkaline pH using complexing agents can be an alternative promising route too.

-

Electrodeposition of Cu–In–Ga in the mixed oxide form using nitrate precursors (of Cu, In, and Ga salts) or hydrogen peroxide (as the supporting electrolyte) is promising electrolyte recipes, as the oxides of Ga and In depositions take place at less cathodic potential. The complexity of Ga inclusion is reduced when compared to conventional electrodeposition routes.

-

Rapid thermal annealing (RTA) and successive selenization/sulfurization using elemental sulfur and selenium are the most preferred post-processing routes followed in the industrial scale. Other annealing schemes such as triple step annealing in H2Se/Ar/H2S or H2Se/Ar/H2Se were also reported to be effective towards minimizing the Ga accumulation problems and in terms of device efficiency. However, for reducing the fabrication cost, alternative routes for evading the Se loss during Argon/N2 annealing and its effect on the device performance are to be explored extensively.

-

Regarding buffer layers, Zn(O,S) grown by chemical bath deposition technique is found to be a more promising alternative to CdS in terms of its performance and stability. A record efficiency beyond 22% has been achieved utilizing CBD grown Zn(O,S) buffer layers. Employing alkali-PDT treatments can help in improving the CIGSe devices.

A full-fledged industrialization of the devices fabricated through electroplating routes requires further in-depth extensive and explorative studies on electronic characteristics of the CIS/CGS/CIGSe absorber layers. For avoiding H2Se or selenization steps, the annealing effects of the surface modified CIGSe (CIGSe/In–Se or Se or Ga–Se) stacks and its role in Se retainment are to be explored for a competitive and cost-effective deposition scheme.

References

Badawy Waheed, A.: A review on solar cells from Si-single crystals to porous materials and quantum dots. J. Adv. Res. 6, 123–132 (2015)

Brown, G.F., Wu, J.: Third generation photovoltaics. Laser Photon. Rev. 3, 394–405 (2009)

Pagliaro, M., Ciriminna, R., Palmisano, G.: Flexible solar cells. Chemsuschem 1, 880–891 (2008)

Chirilă, A., Reinhard, P., Pianezzi, F., Bloesch, P., Uhl, A.R., Fella, C., Kranz, L., Keller, D., Gretener, C., Hagendorfer, H., Jaeger, D., Erni, R., Nishiwaki, S., Buecheler, S., Tiwari, N.: Potassium-induced surface modification of Cu(In, Ga)Se2 thin films for high-efficiency solar cells. Nat. Mater. 12, 1107 (2013)

Reinhard, P., Bissig, B., Pianezzi, F., Avancini, E., Hagendorfer, H., Keller, D., Fuchs, P., Döbeli, M., Vigo, C., Crivelli, P., Nishiwaki, S., Buecheler, S., Tiwari, A.N.: Features of KF and NaF postdeposition treatments of Cu(In, Ga)Se2 absorbers for high efficiency thin film solar cells. Chem. Mater. 27, 5755–5764 (2015)

Jackson, P., Wuerz, R., Hariskos, D., Lotter, E., Witte, W., Powalla, M.: Effects of heavy alkali elements in Cu(In, Ga)Se2 solar cells with efficiencies up to 22.6%. Phys. Status Solidi RRL 10, 583–586 (2016)

Friedlmeier, T.M., Jackson, P., Bauer, A., Hariskos, D., Kiowski, O., Wuerz, R., Powalla, M.: Improved photocurrent in Cu(In, Ga)Se2 solar cells: from 20.8% to 21.7% efficiency with CdS buffer and 21.0% Cd-free. IEEE J. Photovolt. 5, 1487–1491 (2015)

Kamada, R., Yagioka, T., Adachi, S., Handa, A., Tai, K. F., Kato, T., Sugimoto, H.: New world record Cu(In,Ga)(Se,S)2 thin film solar cell efficiency beyond 22%. In: IEEE 43rd Photovoltaic Specialists Conference (PVSC), Portland, 2016. https://doi.org/10.1109/pvsc.2016.7749822

Green, M.A., Emery, K., Hishikawa, Y., Warta, W., Dunlop, E.D., Levi, D.H., Ho-Baillie, A.W.Y.: Solar cell efficiency tables (version 49). Prog. Photovolt. Res. Appl. 25, 3–13 (2017)

Aksu, S., Pinarbasi, M.: Electrodeposition methods and chemistries for deposition of CIGS precursor thin films. In: 37th IEEE Photovoltaic Specialists Conference, Seattle, 2011. https://doi.org/10.1109/pvsc.2011.6185907

Lincot, D.: Electrodeposition of semiconductors. Thin Solid Films 487, 40–48 (2005)

Saji, V.S., Choi, I.H., Lee, C.W.: Progress in electrodeposited absorber layer for CuIn(1−x)Ga x Se2 (CIGS) solar cells. Sol. Energy 85, 2666–2678 (2011)

Ghorbani, E., Kiss, J., Mirhosseini, H., Roma, G., Schmidt, M., Windeln, J., Kühne, T.D., Felser, C.: Hybrid-functional calculations on the incorporation of Na and K impurities into the CuInSe2 and CuIn5Se8 solar-cell materials. J. Phys. Chem. C 119, 25197–25203 (2015)

Abou-Ras, D., Caballero, R., Kaufmann, C.A., Nichterwitz, M., Sakurai, K., Schorr, S., Unold, T., Schock, H.W.: Impact of the Ga concentration on the microstructure of CuIn1−xGa x Se2. Phys. Status Solidi RRL 2, 135–137 (2008)

Continenza, A., Massidda, S., Freeman, A.J., De Pascale, T.M., Meloni, F., Serra, M.: Structural and electronic properties of narrow-gap ABC2 chalcopyrite semiconductors. Phys. Rev. B. 46, 10070–10077 (1992)

Shafarman, W.N., Stolt, L.: Cu (InGa)Se2 Solar Cells. In: Luque, A., Hegedus, S. (eds.) Handbook of photovoltaic science and engineering, pp. 567–616. Wiley, Chichester (2005)

Jaffe, J.E., Zunger, A.: Theory of the band-gap anomaly in ABC2 chalcopyrite semiconductors. Phys. Rev. B. 29, 1882–1906 (1984)

Zunger, A.: New insights on chalcopyrites from solid-state theory. Thin Solid Films 515, 6160–6162 (2007)

Zhao, Y.J., Persson, C., Lany, S., Zunger, A.: Why can CuInSe2 be readily equilibrium-doped n -type but the wider-gap CuGaSe2 cannot? Appl. Phys. Lett. 85, 5860–5862 (2004)

Guillemoles, J.F., Kronik, L., Cahen, D., Rau, U., Jasenek, A., Schock, H.W.: Stability issues of Cu(In, Ga)Se2-based solar cells. J. Phys. Chem. B. 104, 4849–4862 (2000)

Zhang, S.B., Wei, S.-H., Zunger, A., Katayama-Yoshida, H.: Defect physics of the CuInSe2 chalcopyrite semiconductor. Phys. Rev. B. 57, 9642–9656 (1998)

Siebentritt, S., Gütay, L., Regesch, D., Aida, Y., Deprédurand, V.: Why do we make Cu(In, Ga)Se2 solar cells non-stoichiometric? Sol. Energy Mater. Sol. Cells 119, 18–25 (2013)

Insignares-Cuello, C., Broussillou, C., Bermúdez, V., Saucedo, E., Pérez-Rodríguez, A., V, Izquierdo-Roca: Raman scattering analysis of electrodeposited Cu(In, Ga)Se2 solar cells: Impact of ordered vacancy compounds on cell efficiency. Appl. Phys. Lett. 105, 021905 (2014)

Siebentritt, S., Igalson, M., Persson, C., Lany, S.: The electronic structure of chalcopyrites-bands, point defects and grain boundaries. Prog. Photovolt. Res. Appl. 18, 390–410 (2010)

Turcu, M., Rau, U.: Fermi level pinning at CdS/Cu(In, Ga)(Se, S)2 interfaces: effect of chalcopyrite alloy composition. J. Phys. Chem. Solids 64, 1591–1595 (2003)

Dharmadasa, I.M., Chaure, N.B., Samantilleke, A.P., Hassan, A.: Multi Fermi level pinning at metal/Cu(InGa)(SeS)2 interfaces. Sol. Energy Mater. Sol. Cells 92, 923–928 (2008)

Lany, S., Zunger, A.: Light- and bias-induced metastabilities in Cu(In, Ga)Se2 based solar cells caused by the (VSe–VCu]) vacancy complex. J. Appl. Phys. 100, 113725 (2006)

Jensen, S.A., Kanevce, A., Mansfield, L.M., Glynn, S., Lany, S., Kuciauskas, D.: Optically induced metastability in Cu(In, Ga)Se2. Sci. Rep. 7, 13788 (2017)

Jackson, P., Hariskos, D., Wuerz, R., Kiowski, O., Bauer, A., Friedlmeier, T.M., Powalla, M.: Properties of Cu(In, Ga)Se2 solar cells with new record efficiencies up to 21.7%. Phys. Status Solidi RRL 9, 28–31 (2015)

Repins, I., Glynn, S., Duenow, J., Coutts, T.J., Metzger, W.K., Contreras, M.A.: Required material properties for high-efficiency CIGS modules. Proc. SPIE 7409, 74090M (2009)

Misic, B., Pieters, B.E., Theisen, J.P., Gerber, A., Rau, U.: Shunt mitigation in ZnO:Al/i-ZnO/CdS/Cu(In, Ga)Se2 solar modules by the i-ZnO/CdS buffer combination. Phys. Status Solidi A 212, 541–546 (2015)

Scheer, R., Messmann-Vera, L., Klenk, R., Schock, H.-W.: On the role of non-doped ZnO in CIGSe solar cells. Prog. Photovolt. Res. Appl. 20, 619–624 (2012)

Nakada, T.: Nano-structural investigations on Cd-doping into Cu(In, Ga)Se2 thin films by chemical bath deposition process. Thin Solid Films 361–362, 346–352 (2000)

Cojocaru-Mirédin, O., Choi, P., Wuerz, R., Raabe, D.: Exploring the p–n junction region in Cu(In, Ga)Se2 thin-film solar cells at the nanometer-scale. Appl. Phys. Lett. 101, 181603 (2012)

Abou-Ras, D., Kostorz, G., Romeo, A., Rudmann, D., Tiwari, A.N.: Structural and chemical investigations of CBD- and PVD–CdS buffer layers and interfaces in Cu(In, Ga)Se2-based thin film solar cells. Thin Solid Films 480–481, 118–123 (2005)

Lei, C., Duch, M., Robertson, I.M., Rockett, A.: Effects of solution-grown CdS on Cu(InGa)Se2 grain boundaries. J. Appl. Phys. 108, 114908 (2010)

Liao, D., Rockett, A.: Cu depletion at the CuInSe2 surface. Appl. Phys. Lett. 82, 2829 (2003)

He, X., Paulauskas, T., Ercius, P., Varley, J., Bailey, J., Zapalac, G., Poplavskyy, D., Mackie, N., Bayman, A., Spaulding, D., Klie, R., Lordi, V., Rockett, A.: Cd doping at PVD–CdS/CuInGaSe2 heterojunctions. Sol. Energy Mater. Sol. Cells 164, 128–134 (2017)

Salome, P.M.P., Ribeiro-Andrade, R., Teixeira, J.P., Keller, J., Torndahl, T., Nicoara, N., Edoff, M., Gonzalez, J.C., Leitao, J.P., Sadewasser, S.: Cd and Cu interdiffusion in Cu(In, Ga)Se2/CdS hetero-interfaces. IEEE J. Photovolt. 7, 858–863 (2017)

Sozzi, G., Di Napoli, S., Menozzi, R., Carron, R., Avancini, E., Bissig, B., Buecheler, S., Tiwari, A.N.: Analysis of Ga grading in CIGS absorbers with different Cu content. In: 2016 IEEE 43rd Photovoltaic Specialists Conference (PVSC), Portland, 2016. https://doi.org/10.1109/pvsc.2016.7750042

Song, J., Li, S.S., Huang, C.H., Crisalle, O.D., Anderson, T.J.: Device modeling and simulation of the performance of Cu(In1 − x, Ga x )Se2 solar cells. Solid State Electron 48, 73–79 (2004)

Lundberg, O., Bodegård, M., Malmstro̊m, J., Stolt, L.: Influence of the Cu(In, Ga)Se2 thickness and Ga grading on solar cell performance. Prog. Photovolt. Res. Appl. 11, 77–88 (2003)

Richter, M., Schubbert, C., Eraerds, P., Parisi, J., Riedel, I., Dalibor, T., Palm, J.: Comprehensive simulation model for Cu(In, Ga)(Se, S)2 solar cells. Sol. Energy Mater. Sol. Cells 132, 162–171 (2015)

Avancini, E., Carron, R., Bissig, B., Reinhard, P., Menozzi, R., Sozzi, G., Di Napoli, S., Feurer, T., Nishiwaki, S., Buecheler, S., Tiwari, A.N.: Impact of compositional grading and overall Cu deficiency on the near-infrared response in Cu(In, Ga)Se2 solar cells. Prog. Photovolt. Res. Appl. 25, 233–241 (2017)

Deprédurand, V., Bertram, T., Siebentritt, S.: How does the selenium activity influence CuInSe2 devices grown under Cu-excess? In : Proceedings of SPIE 8823, Thin Film Solar Technology V, 882304, 2013

Gtay, L., Regesch, D., Larsen, J.K., Aida, Y., Depredurand, V., Siebentritt, S.: Influence of copper excess on the absorber quality of CuInSe2. Appl. Phys. Lett. 99, 151912 (2011)

Deprédurand, V., Tanaka, D., Aida, Y., Carlberg, M., Fèvre, N., Siebentritt, S.: Current loss due to recombination in Cu-rich CuInSe2 solar cells. J. Appl. Phys. 115, 44503–44508 (2014)

Kemell, M., Ritala, M., Leskelä, M.: Effects of post-deposition treatments on the photoactivity of CuInSe2 thin films deposited by the induced co-deposition mechanism. J. Mater. Chem. 11, 668–672 (2001)

Deprédurand, V., Bertram, T., Siebentritt, S.: Influence of the Se environment on Cu-rich CIS devices. Phys. B 439, 101–104 (2014)

Aida, Y., Depredurand, V., Larsen, J.K., Arai, H., Tanaka, D., Kurihara, M., Siebentritt, S.: Cu-rich CuInSe2 solar cells with a Cu-poor surface. Prog. Photovolt. Res. Appl. 23, 754–764 (2015)

Ramanujam, J., Singh, U.P.: Copper indium gallium selenide based solar cells—a review. Energy Environ. Sci. 10, 1306–1319 (2017)

Abou-Ras, D., Schmidt, S.S., Schäfer, N., Kavalakkatt, J., Rissom, T., Unold, T., Mainz, R., Weber, A., Kirchartz, T., Simsek Sanli, E., van Aken, P.A., Ramasse, Q.M., Kleebe, H.-J., Azulay, D., Balberg, I., Millo, O., Cojocaru-Mirédin, O., Barragan-Yani, D., Albe, K., Haarstrich, J., Ronning, C.: Compositional and electrical properties of line and planar defects in Cu(In, Ga)Se2 thin films for solar cells—a review. Phys. Status Solidi RRL 10, 363–375 (2016)

Savadogo, O.: Chemically and electrochemically deposited thin films for solar energy materials. Sol. Energy Mater. Sol. Cells 52, 361–388 (1998)

Calixto, M.E., Dobson, K.D., McCandless, B.E., Birkmire, R.W.: Controlling growth chemistry and morphology of single-bath electrodeposited Cu(In, Ga)Se2 thin films for photovoltaic application. J. Electrochem. Soc. 153, G521 (2006)

Saji, V.S., Jung, C.-Y., Lee, C.-W.: Electrodeposition of copper, selenium, indium, and gallium on molybdenum/surface oxides: unary, binary, ternary and quaternary compositions. J. Electrochem. Soc. 162, D465–D479 (2015)

Bhattacharya, R.N., Rajeshwar, K.: Electrodeposition of CuInX (X = Se, Te) thin films. Solar Cells. 16, 237–243 (1986)

Chiu, Y.-S., Hsieh, M.-T., Chang, C.-M., Chen, C.-S., Whang, T.-J.: Single-step electrodeposition of CIS thin films with the complexing agent triethanolamine. Appl. Surf. Sci. 299, 52–57 (2014)

Liu, J., Liu, F., Lai, Y., Zhang, Z., Li, J., Liu, Y.: Effects of sodium sulfamate on electrodeposition of Cu(In, Ga)Se2 thin film. J. Electroanal. Chem. 651, 191–196 (2011)

Muthuraj, J.J.J., Rasmussen, D.H., Suni, I.I.: Electrodeposition of CuGaSe2 from thiocyanate-containing electrolytes. J. Electrochem. Soc. 158, D54 (2011)

Stratieva, N., Tzvetkova, E., Ganchev, M., Kochev, K., Tomov, I.: Structural and optical properties of electrodeposited CuInSe2 layers. Sol. Energy Mater. Sol. Cells 45, 87–96 (1997)

Aksu, S., Wang, J., Basol, B.M.: Electrodeposition of In–Se and Ga–Se thin films for preparation of CIGS Solar Cells. Electrochem. Solid State Lett. 12, D33 (2009)

Aksu, S., Pinarbasi, M.: Electrodeposition of Cu–In–Ga films for the preparation of CIGS solar cells. In: 35th IEEE Photovoltaic Specialists Conference. Honolulu, 2010. https://doi.org/10.1109/pvsc.2010.5617115

Duchatelet, A., Savidand, G., Loones, N., Chassaing, E., Lincot, D.: Mechanism of electrochemical deposition of Cu–In–Ga mixed oxide/hydroxide thin films for Cu(In, Ga)Se2 solar cells. J. Electrochem. Soc. 161, D3120–D3129 (2014)

Duchatelet, A., Savidand, G., Vannier, R.N., Chassaing, E., Lincot, D.: A new deposition process for Cu(In, Ga)(S, Se)2 solar cells by one-step electrodeposition of mixed oxide precursor films and thermochemical reduction. J. Renew. Sustain. Energy. 5, 11203 (2013)

Yang, J., Huang, C., Jiang, L.X., Liu, F.Y., Lai, Y.Q., Li, J., Liu, Y.X.: Effects of hydrogen peroxide on electrodeposition of Cu(In, Ga)Se2 thin films and band gap controlling. Electrochim. Acta 142, 208–214 (2014)

Chassaing, E., Duchatelet, A., Lincot, D.: Mechanistic study of one-step cathodic electrodeposition of mixed Cu–In–Ga oxide/hydroxide films with hydrogen peroxide oxygen precursor. J. Electrochem. Soc. 164, D852–D860 (2017)

Chaure, N.B., Young, J., Samantilleke, A.P., Dharmadasa, I.M.: Electrodeposition of p–i–n type CuInSe2 multilayers for photovoltaic applications. Sol. Energy Mater. Sol. Cells 81, 125–133 (2004)

Chaure, N.B., Samantilleke, A.P., Burton, R.P., Young, J., Dharmadasa, I.M.: Electrodeposition of p+, p, i, n and n+-type copper indium gallium diselenide for development of multilayer thin film solar cells. Thin Solid Films 472, 212–216 (2005)

Li, Y., Shaikh, S.S., Menezes, S.: Film growth mechanism for electrodeposited copper indium selenide compounds. Thin Solid Films 524, 20–25 (2012)

Ribeaucourt, L., Chassaing, E., Savidand, G., Lincot, D.: Synthesis of Cu(In, Ga)Se2 absorber using one-step electrodeposition of Cu–In–Ga precursor. Thin Solid Films 519, 7241–7244 (2011)

Harati, M., Jia, J., Giffard, K., Pellarin, K., Hewson, C., Love, D.A., Lau, W.M., Ding, Z.: One-pot electrodeposition, characterization and photoactivity of stoichiometric copper indium gallium diselenide (CIGS) thin films for solar cells. Phys. Chem. Chem. Phys. 12, 15282–15290 (2010)

Wellings, J.S., Samantilleke, A.P., Heavens, S.N., Warren, P., Dharmadasa, I.M.: Electrodeposition of CuInSe2 from ethylene glycol at 150 °C. Sol. Energy Mater. Sol. Cells 93, 1518–1523 (2009)

Lian, Y., Ji, S., Zhao, L., Zhang, J., Yang, P., Zhang, J., An, M.: One-step electrodeposition of CuIn x Ga1−x Se2 thin films from a mixture system of ionic liquid and ethanol. New J. Chem. 39, 7742–7745 (2015)

Long, F., Wang, W., Du, J., Zou, Z.: CIS(CIGS) thin films prepared for solar cells by one-step electrodeposition in alcohol solution. J. Phys. Conf. Ser. 152, 012074 (2009)

Steichen, M., Thomassey, M., Siebentritt, S., Dale, P.: Controlled electrodeposition of Cu–Ga from a deep eutectic solvent for low cost fabrication of CuGaSe2 thin film solar cells. Phys. Chem. Chem. Phys. 13, 4292–4302 (2011)

Simka, W., Puszczyk, D., Nawrat, G.: Electrodeposition of metals from non-aqueous solutions. Electrochim. Acta 54, 5307–5319 (2009)

Gadilohar, B.L., Shankarling, G.S.: Choline based ionic liquids and their applications in organic transformation. J. Mol. Liq. 227, 234–261 (2017)

Zhang, Y., Han, J., Liao, C.: Insights into the properties of deep eutectic solvent based on reline for Ga-controllable CIGS solar cell in one-step electrodeposition. J. Electrochem. Soc. 163, D689–D693 (2016)

Malaquias, J.C., Regesch, D., Dale, P.J., Steichen, M.: Tuning the gallium content of metal precursors for Cu(In, Ga)Se2 thin film solar cells by electrodeposition from a deep eutectic solvent. Phys. Chem. Chem. Phys. 16, 2561–2567 (2014)

Malaquias, J.C., Berg, D.M., Sendler, J., Steichen, M., Valle, N., Dale, P.J.: Controlled bandgap CuIn1−xGa x (S0.1Se0.9)2 (0.10 ≤ x≤0.72) solar cells from electrodeposited precursors. Thin Solid Films 582, 2–6 (2015)

Liu, F., Yang, J., Zhou, J., Lai, Y., Jia, M., Li, J., Liu, Y.: One-step electrodeposition of CuGaSe2 thin films. Thin Solid Films 520, 2781–2784 (2012)

Oda, Y., Minemoto, T., Takakura, H.: Electrodeposition of crack-free CuGaSe2 thin films from single bath. J. Electrochem. Soc. 155, H292 (2008)

Manfredy, L., Marquez, O.P., Lopez-Rivera, S.A., Marquez, J., Martínez, Y., Miranda, D.A.: Electrochemical preparation and structural characterization of CuGaSe2 thin films. J. Phys. Conf. Ser. 687, 12038 (2016)

Fernandez, A.M., Bhattacharya, R.N.: Electrodeposition of CuIn1−xGa x Se2 precursor films: optimization of film composition and morphology. Thin Solid Films 474, 10–13 (2005)

Thouin, L., Massaccesi, S., Sanchez, S., Vedel, J.: Formation of copper indium diselenide by electrodeposition. J. Electroanal. Chem. 374, 81–88 (1994)

Frontini, M.A., Vázquez, M.: Electrodeposition of CuInSe2 in citrate-containing electrolytes. J. Mater. Sci. 45, 2995–3000 (2010)

Hamrouni, S., AlKhalifah, M.S., Boujmil, M.F., Saad, K.B.: Preparation and characterization of CuInSe2 electrodeposited thin films annealed in vacuum. Appl. Surf. Sci. 292, 231–236 (2014)

Bamiduro, O., Chennamadhava, G., Mundle, R., Konda, R., Robinson, B., Bahoura, M., Pradhan, A.K.: Synthesis and characterization of one-step electrodeposited CuIn(1−x)Ga x Se2/Mo/glass films at atmospheric conditions. Sol. Energy 85, 545–552 (2011)

Mandati, S., Sarada, B.V., Dey, S.R., Joshi, S.V.: CuIn1−xGa x Se2 thin-film absorber layers for solar photovoltaics fabricated by two-stage pulsed current electrodeposition. Mater. Lett. 118, 158–160 (2014)

Ganchev, M., Kois, J., Kaelin, M., Bereznev, S., Tzvetkova, E., Volobujeva, O., Stratieva, N., Tiwari, A.: Preparation of Cu(In, Ga)Se2 layers by selenization of electrodeposited Cu–In–Ga precursors. Thin Solid Films 511–512, 325–327 (2006)

Marudachalam, M., Birkmire, R.W., Hichri, H.: Phases, morphology, and diffusion in CuIn x Ga1−xSe2 thin films. J. Appl. Phys. 82, 2896 (1997)

Kohara, N., Nishiwaki, S., Hashimoto, Y., Negami, T., Wada, T.: Electrical properties of the Cu(In, Ga)Se2/MoSe2/Mo structure. Sol. Energy Mater. Sol. Cells 67, 209–215 (2001)

Hsiao, K.J., Liu, J.D., Hsieh, H.H., Jiang, T.-S.: Electrical impact of MoSe2 on CIGS thin-film solar cells. Phys. Chem. Chem. Phys. 15, 18174–18178 (2013)

Oliva, F., Broussillou, C., Annibaliano, M., Frederich, N., Grand, P.P., Roussy, A., Collot, P., Bodnar, S.: Formation mechanisms of Cu(In, Ga)Se2 solar cells prepared from electrodeposited precursors. Thin Solid Films 535, 127–132 (2013)

Duchatelet, A., Sidali, T., Loones, N., Savidand, G., Chassaing, E., Lincot, D.: 12.4% Efficient Cu(In, Ga)Se2 solar cell prepared from one step electrodeposited Cu–In–Ga oxide precursor layer. Sol. Energy Mater. Sol. Cells 119, 241–245 (2013)

Bhattacharya, R.N.: CIGS-based solar cells prepared from electrodeposited stacked Cu/In/Ga layers. Sol. Energy Mater. Sol. Cells 113, 96–99 (2013)

Bhattacharya, R.N., Oh, M.-K.K., Kim, Y.: CIGS-based solar cells prepared from electrodeposited precursor films. Sol. Energy Mater. Sol. Cells 98, 198–202 (2012)

Başol, M., Pinarbaşi, M., Aksu, S., Freitag, J., Gonzalez, P., Johnson, T., Matus, Y., Metin, B., Narasimhan, M., Nayak, D., Norsworthy, G., Soltz, D., Wang, J., Wang, T., Zolla, H.: Status of electroplating bases CIGS technology development. In: Proceedings of the 34th IEEE PVSC. https://doi.org/10.1109/pvsc.2009.5411342

Aksu, S., Pethe, S., Shwarsctein, A.K., Kundu, S., Pinarbasi, M.: Recent advances in electroplating-based CIGS solar cell fabrication, In: Proceedings of the 38th IEEE Photovoltaics Specialists Conference. Texas, 2012. https://doi.org/10.1109/pvsc.2012.6318235

Broussillou, C., Viscogliosi, C., Rogee, A., Angle, S., Grand, P.P., Bodnar, S., et al.: Statistical process control for Cu(In,Ga)(S,Se)2 electrodeposition-based manufacturing process 60 × 120 cm2 modules up to 14.0% efficiency. In: 42nd IEEE Photovoltaic Specialist Conference (PVSC), New Orleans, 2015. https://doi.org/10.1109/pvsc.2015.7356224

Duchatelet, A., Letty, E., Ferrer, J.S., Grand, P.P., Mollica, F., Naghavi, N.: The impact of reducing the thickness of electrodeposited stacked Cu/In/Ga layers on the performance of CIGS solar cells. Sol. Energy Mater. Sol. Cells 162, 114–119 (2017)

Kim, K., Hanket, G.M., Huynh, T., Shafarman, W.N.: Three-step H2 Se/Ar/H2S reaction of Cu–In–Ga precursors for controlled composition and adhesion of Cu(In, Ga)(Se, S)2 thin films. J. Appl. Phys. 111, 83710 (2012)

Bi, J., Ao, J., Gao, Q., Zhang, Z., Sun, G., He, Q., Zhou, Z., Sun, Y., Zhang, Y.: Controllable growth of Ga film electrodeposited from aqueous solution and Cu(In, Ga)Se2 solar cells. ACS Appl. Mater. Interfaces 9, 18682–18690 (2017)

Mishra, K.K., Rajeshwar, K.: A voltammetric study of the electrodeposition chemistry in the Cu + In + Se system. J. Electroanal. Chem. 271, 279–294 (1989)