Abstract

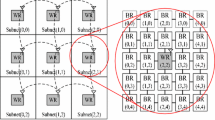

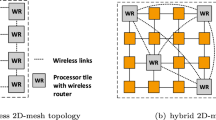

Hybrid architecture is becoming a promising solution for today’s high-performance on-chip communication networks, commonly known as Networks-on-Chip (NoCs). For example, a mesh-based hybrid on-chip network has wired and wireless routers. The intent is to achieve better performance in low latency, high throughput, and low energy than a traditional wired or wireless mesh NoC. The performance of a hybrid mesh NoC is heavily affected by the positions of the wireless routers in the NoC. This paper proposes a placement strategy for placing a wireless router in a wired Mesh NoC (MoC) into a hybrid MoC. The proposed method involves partitioning an underlying network into multiple equal-size subnetworks. Each subnetwork includes two wireless routers for better connectivity between communicating nodes. The proposed strategy on evaluation of a 32-bit 8 × 8 hybrid MoC shows that the basic performance metrics- latency, network throughput, and energy consumption ranges from 18.64 to 42822 cycles, 5.02–11.23 flits/cycle, and 14.91–34.42 μJ, respectively. Furthermore, results improve packet loss, latency, and throughput metrics up to 96%, 98.36%, and 25.77%, respectively, compared to the wired 8 × 8 MoC. Furthermore, the proposed approach improves latency reduction by 1347% and scales by 15 × than a set of previous methods.

Similar content being viewed by others

References

Bhowmik B (2021) Dugdugi: an optimal fault addressing scheme for octagon-like on-chip communication networks. IEEE Trans Very Large Scale Integr (VLSI) Syst 29(5):1009–1021

Ganguly A, Chang K, Deb S, Pande PP, Belzer B, Teuscher C (2010) Scalable hybrid wireless network-on-chip architectures for multicore systems. IEEE Trans Comput 60(10):1485–1502

Tatas K, Siozios K, Soudris D, Jantsch A (2014) Network-on-chip technology: a paradigm shift. Designing 2D and 3D network-on-chip architectures. Springer, Cham, pp 3–18

Das A, Kumar A, Jose J, Palesi M (2021) Revising NoC in future multi-core based consumer electronics for performance. IEEE Consum Electron Mag 11(3):79–86

Gagan N, Bhowmik B (2021) Long-distance communication via pseudo-3d networks-on-chip. In: 2021 IEEE 18th India council international conference (INDICON), p 1–6

Deb S, Ganguly A, Pande PP, Belzer B, Heo D (2012) Wireless NoC as interconnection backbone for multicore chips: promises and challenges. IEEE J Emerg Sel Top Circuits Syst 2(2):228–239

Achballah AB, Othman SB, Saoud SB (2017) Problems and challenges of emerging technology networks- on- chip: a review. Microprocess Microsyst 53:1–20

Karali A, Bhowmik B (2022) Hybrid MoCS for long-distance on-chip communications. In: 2022 IEEE region 10 symposium (TENSYMP), p 1–6

Deb S, Chang K, Yu X, Sah SP, Cosic M, Ganguly A, Pande PP, Belzer B, Heo D (2012) Design of an energy-efficient MoCs-compatible NoC architecture with millimeter-wave wireless interconnects. IEEE Trans Comput 62(12):2382–2396

Carloni LP, Pande P, Xie Y (2009) Networks-on-chip in emerging interconnect paradigms: advantages and challenges. In: 2009 3rd ACM/IEEE international symposium on networks-on-chip. IEEE, p 93–102

Catania V, Mineo A, Monteleone S, Palesi M, Patti D (2017) Improving energy efficiency in wireless network-on-chip architectures. ACM J Emerg Technol Comput Syst (JETC) 14(1):1–24

Pande PP, Ganguly A, Chang K, Teuscher C (2009) Hybrid wireless network on chip: a new paradigm in multi-core design. In: 2009 2nd international workshop on network on chip architectures. IEEE, p 71–76

Gade SH, Deb S (2016) Hywin: hybrid wireless NoC with sandboxed sub-networks for CPU/GPU architectures. IEEE Trans Comput 66(7):1145–1158

Deb S, Chang K, Ganguly A, Pande P (2010) Comparative performance evaluation of wireless and optical NoC architectures. In: 23rd IEEE international SOC conference, p 487–492

Dehghani A, Jamshidi K (2016) A novel approach to optimize fault-tolerant hybrid wireless network-on-chip architectures. ACM J Emerg Technol Comput Syst (JETC) 12(4):1–37

Abbas D, Jamshidi K (2015) A fault-tolerant hierarchical hybrid mesh-based wireless network-on-chip architecture for multicore platforms. J Supercomput 71(8):3116–3148

Rezaei A, Daneshtalab M, Safaei F, Zhao D (2016) Hierarchical approach for hybrid wireless network-on-chip in many-core era. Comput Electr Eng 51:225–234

Bhowmik B, Hazarika P, Kale P, Jain S (2021) Ai technology for NoC performance evaluation. IEEE Trans Circuits Syst II Express Briefs 68(12):3483–3487

Wettin P, Vidapalapati A, Gangul A, Pande PP (2013) Complex network-enabled robust wireless network-on-chip architectures. ACM J Emerg Technol Comput Syst (JETC) 9(3):1–19

Jindal N, Gupta S, Ravipati DP, Panda PR, Sarangi SR (2020) Enhancing network-on-chip performance by reusing trace buffers. IEEE Trans Comput Aided Des Integr Circuits Syst 39(4):922–935

Psarras A, Moisidis S, Nicopoulos C, Dimitrakopoulos G (2017) Networks-on-chip with double-data-rate links. IEEE Trans Circuits Syst I Regul Papers 64(12):3103–3114

Song Y, Lin B (2019) Uniform minimal first: latency reduction in throughput-optimal oblivious routing for mesh-based networks-on-chip. IEEE Embed Syst Lett 11(3):81–84

Zhao D, Wang Y, Wu H, Kikkawa T (2015) I (re) 2-winoc: exploring scalable wireless on-chip micronetworks for heterogeneous embedded many-core socs. Digit Commun Netw 1(1):45–56

Jiang G, Li Z, Wang F, Wei S (2014) A low-latency and low-power hybrid scheme for on-chip networks. IEEE Trans Very Large Scale Integr (VLSI) Syst 23(4):664–677

Gagan N, Bhowmik B (2021) Topology exploration for long-distance communication. In: TENCON 2021 - 2021 IEEE region 10 conference (TENCON), p 875–880

Catania V, Mineo A, Monteleone S, Palesi M, Patti D (2016) Cycle-accurate network on chip simulation with noxim. ACM Trans Model Comput Simul (TOMACS) 27(1):1–25

Funding

The authors received no financial support for this article’s research, authorship, and/or publication.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare no potential conflict of interest concerning research, authorship, and/or publication of this article. No financial or non-financial interests are directly or indirectly related to the work submitted for publication.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Karali, A., Bhowmik, B. Wireless Router Placements for Long-Distance Communications in MoCs. CSIT 11, 163–175 (2023). https://doi.org/10.1007/s40012-023-00386-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40012-023-00386-x