Abstract

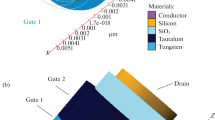

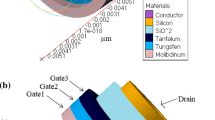

In the present work, the authors have studied the Quasi-Static Capacitance–Voltage (QSCV) characteristics of 10 nm gate length double gate (DG) NMOSFETs of different channel materials namely, Si, Ge, and \({In}_{0.53}G{a}_{0.47}As\), the results are reported using Silvaco ATLAS TCAD. The QSCV approach provides the advantage of immunity against frequency-dependent effects and has the ability to measure the small capacitance in the range of 100 fF. In this device, we consider the self-consistent solution of Schrodinger’s equation with Poisson’s equation. Further, the conduction band splitting in multiple sub-bands has been considered with light doping in the channel region. For this, the authors have studied C-V behaviour of the devices by observing the effect of metal gate work function engineering (using Ta, W, Mo, Ni, Au and Pt), channel engineering (using Si, \({{\text{In}}}_{0.53}{{\text{Ga}}}_{0.47}{\text{As}}\) and Ge) and variation of channel thickness (2 nm, 5 nm, 10 nm and 1502 nm) with gate oxide \((Si{O}_{2})\) of thickness 1.2 nm. In further studies, \(Si{O}_{2}\) was replaced its EOT with \(Hf{O}_{2}\) and results were again studied. The comparison of the behavior of C-V curve has been done for the above-mentioned channel materials. It was found that there is a significant reduction in inversion mode Capacitance with voltage for all the channel materials used for both SiO2 based devices and with HfO2 based devices. This has been attributed to quantization which results in a decrease in the overall gate to channel capacitance (CGC) and hence increases the threshold voltage in MOS device. The quantization effect is lightly seen in Si for channel thickness of 2 nm, however for the same thickness, quantization is seen in Ge. Also for In0.53Ga0.47As quantization is seen for channel thickness of 2nm, 5nm, and 10 nm because of its low electron effective mass. The QSCV characteristics are also used to measure oxide thickness, flat-band voltage, threshold voltage, maximum depletion region thickness, distribution of charges in dielectric, interface traps charge and interface states between channel and gate oxide before fabrication of the device.

Similar content being viewed by others

Data Availability

All the data are available within this paper.

Change history

18 April 2024

A Correction to this paper has been published: https://doi.org/10.1007/s12633-024-02955-4

References

Tao J, Zhao CZ, Zhao C, Taechakumput P, Werner M, Taylor S, Chalker PR (2012) Extrinsic and Intrinsic Frequency Dispersion of High-κ Materials in Capacitance-Voltage Measurements. Materials 5:1005–1032

Moore Gordon E (1965) Cramming more components onto integrated circuits. Electronics 38(8):114–117

Robertson J, Wallace RM (2015) High-κ and metal gates for CMOS applications. Mater Sci Eng R 88:1–41

Muller RS, Theodore I (2009) Kamins with Mansun Chan. In: Device electronics for integrated circuits, 3rd edn. WILEY

Riel H, Wernersson L-E, Hong M, del Alamo JA (2014) III-V compound semiconductor transistor–-from planar to nanowire structures. Mater Sci Soc 39:668–677

Chang Leland, Yang Kevin J, Yeo Yee-Chia, Polishchu Igor, King Tsu-Jae, Chenming Hu (2002) Direct-Tunneling Gate Leakage Current in Double-Gate and Ultrathin Body MOSFETs. IEEE Trans Electron Dev 49(12):2228–2295

Ranuárez JC, Deen MJ, Chen C-H (2006) A review of gate tunneling current in MOS devices. Microelectron Reliab 46:1939–1956

Wong H, Iwai H (2006) On the scaling issues and high-κ dielectric replacement of ultrathin gate dielectrics for nanoscale MOS transistors. Microelectron Eng 83:1867–1904

Krylov I, Ritter D, Eizeberg M (2017) HfxAlyO ternary dielectrics for InGaAs based metal-oxide-semiconductor capacitors. J Appl Phys 122:034505–034509

Kong X, Liang R, Zhou X, Li S, Wang M, Liu H, Wang J, Wang W, Pan J (2016) The Comparison of Current Ratio ION/IOFF and Mobility Between SiGe Substrate and GaAs Substrate In0.23Ga0.77As Channel MOSFETs. IEEE Trans Electron Devices 63:3084–3087

Tewari S, Biswas A, Mallik A (January 2012) Study of InGaAs-Channel MOSFETs for Analog/Mixed-Signal System-on-Chip Applications. IEEE Electron Device Lett 33(3):372–374

Jiang Z, Behin-Aein B, Krivokapic Z, Povolotskyi M (2015) KlimeckG, Tunneling and short channel effects in ultrascaled InGaAs double gate MOSFETs. IEEE Trans Electron Devices 62(2):525–531

Goley PS, Hudait MK (2014) Germanium based field-effect transistors: Challenges and opportunities. Materials 7:2301–2339

Robertson J, Falabretti B (2006) Band offsets of high-κ gate oxides on III-V semiconductors. J Appl Phys 100:014111

Hur J-H, Jeon S (2016) J Phys D Appl Phys 49:155101

Kim H, Saraswat KC, McIntyre PC (2005) Mater Res Soc 20(11)

Wang L (2006) Quantum mechanical effects on mosfet scaling limit

Mudanai S, Fan Y-Y, Ouyang QC, Tasch AlF (2000) EEE Trans Electron Devices 47(10)

Stucchi M, Velenis D, Katti G (2012) Capacitance Measurements of Two-Dimensional and Three-Dimensional IC Interconnect Structures by Quasi-Static C-V Technique. IEEE Trans Instrum Meas 61(7):1979–1980

Moreau M, Munteanu D, Autran JL (2011) Simulation study of Short-Channel Effects and quantum confinement in double-gate FinFET devices with high-mobility materials. Microelectron Eng 88:366–369

Pi TW, Lin YH, Fanchiang YT, Chiang TH, Wei CH, Lin YC, Wertheim GK, Kwo J, Hong M (2015) In-situ atomic layer deposition of trimethylaluminum and water on pristine single-crystal (In)GaAs surfaces: electronic and electric structures. Nanotechnology 26:164001

Chang TW, Lin KY, Lim YH, Young LB, Kwo J, Hong M (2017) Analysis of border and interfacial traps in ALD-Y2O3 and –Al2O3 on GaAs via electrical responses- A comparativ study. Microelectron Eng 178:199–203

Pirro L (2015) Electrical characterization and modeling of advanced SOI substrates. Ph.D. Thesis, Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, pp. 91

Lin D, Brammertz G, Sioncke S, Fleischmann C, Delabie A, Martens K, Bender H, Conard T, Tseng WH, Lin JC, Wang WE, Temst K, Vatomme A, Mitard J, Caymax M, Meuris M, Heyns M, Hoffmann T (2010) Enabling the high-performance InGaAs/Ge CMOS: a common gate stack solution. In: IEEE International Electron Devices Meeting (IEDM). Baltimore

OmarR Mohamed BA, Adel M (2015) Effects of series and parallel resistances on the C-V characteristics of Silicon-based metal oxide semiconductor (MOS) devices. Eur Phys J Plus 130:1–13

Schmitz J, Cubaynes FN, Havens RJ, de Kort R, Scholten AJ, Tiemeijer LF (2003) RF Capacitance-Voltage Characterization of MOSFETs With High Leakage Dielectrics. IEEE Electron Device Lett 24:37–39

Alam A, Ahmed S, Alam MK, Khosru QDM (20–22 December 2008) C-V Characteristics of n-channel Double Gate MOS Structures Incorporating the Effect of Interface States. 5th International Conference on Electrical and Computer Engineering (ICECE) 2008, Dhaka, Bangladesh

Sato S, Kobayashi K, Mori Y, Hisamoto D, Shima A (2020) Investigation of Interface State Density near Conduction Band Edge of 4H-SiC MOSFET based on Inversion Capacitance and Drain-Current Characteristics. Jpn J Appl Phys 59:SGGD09-04

Hossain MdA, Mahmud A, Chowdhury MH, Rahman MdM (2012) Capacitance-voltage characteristics of nanowire trigate MOSFET considering wave function penetration. Int J Electr Comput Eng 2:785–791

Novkovski N, Atanassova E (2017) Frequency dependence of C-V characteristics of MOS capacitors containing nanosized high-κ Ta2O5 dielectrics. Hindawi: Adv Mater Sci Eng 2017:1–11

Tang T-W, Li Y (2002) A SPICE-Compatible model for nanoscale MOSFET capacitor simulation under the inversion condition. IEEE Trans Nanotechnol 1:243–246

Atamuratov AE, YusupovA Atamuratova ZA, Chedjou JC, Kyamakya K (2020) Lateral Capacitance– VoltageMethod of NanoMOSFET for detecting the hot carrier injection. Appl Sci 10:1–9

Xuan Y, Lin HC, Ye PD (2006) Capacitance-voltage Characterization of Atomic-Layer-Deposited Al2O3/InGaAs and Al2O3/GaAs Metal –Oxide-Semiconductor Structures. Electrochem Soc 3:59

Stauffer L, Keithley Instruments (2009) Fundamentals of Semiconductor C-V Measurements. Keithley, p 1–4

Jeong Y-H, Baek R-H, Bae C-K, Yeo KH, Kim D-W, Chung JY, Kim DM (2010) Comparative Study of C-V Characteristics in Si-NWFET and MOSFET. IEEE Nanotechnology Materials and Devices Conference. p 26–29

Li S, Ojima N, Zule Xu, Iizuka T (2022) Analysis and simulation of MOSFET-based gate-voltage-independent capacitor. Jpn J Appl Phys 61:064501

Matacena I, Guerriero P, Lancellotti L, Bobeico E, Lisi N, Chierchia R, Veneri PD, Daliento S (2021) Forward bias capacitance investigation as a powerful tool to monitor graphene/silicon interfaces. Solar Energy 226:1–8

Taoka N, Kubo T, Yamada T, Egawa T, Shimizu M (2017) Understanding of frequency dispersion in C-V curves of metal oxide-semiconductor capacitor with wide-bandgap semiconductor. Microelectron Eng 178:182–185

Tsuji K, Terada K, Nakamoto T, Tsunomura T, Nishida A (2009) Measurement of MOSFET C-V Curve Variation Using CBCM Method. IEEE International Conference on Microelectronic Test Structures. p 81–84

TsuJil K, Teradal K, Takeda RI, Tsunomura T, Nishida A, Mogami T (2011) Threshold Voltage Variation Extracted from MOSFET C-V Curves by Charge-Based Capacitance Measurement. IEEE, International Conference on Microelectronic Test Structures. p 82–86

Boukredimi D, Allouche H (2013) Accurate quasi static capacitance for abrupt homojunction under forward and reverse polarization. Bull Mater Sci 36:251–258

Ucurum C, Goebel H (2013) Quasi-static capacitance–voltage characteristics of pentacene-based metal–oxide–semiconductor structures. Microelectron J 44:606–611

Gulyaev IB, Zhdan AG, Kukharskaya NF, Tikhonov RD, Chucheva GV (2004) Improvements in the Quasi-static Capacitance-Voltage Characterization of Semiconductor-Insulator Interface States (Si/SiO2). Russ Microlectron 33:224–235

Rho K-M, Lee K, Shur M, Fjeldly TA (1993) Unified Quasi-Static MOSFET Capacitance Model. IEEE Trans Electron Devices 40:131–136

Alam MdNK, Islam MS, Islam MdR (2013) Self-Consistent Quasi-Static C-V characteristics of In1-xGaxSb XOI FET. IEEE International Conference of Electron Devices and Solid-state Circuits. p 1–2

Chandrasekaran K, Chiah SB, Shangguan W, See GH, Bera LK, Balasubramanian N, Rustagi SC (2006) Effect of substrate doping on the capacitance-voltage characteristics of strained-silicon pMOSFETs. IEEE Electron Device Lett 27:62–64

Pirro L, Ionica I, Ghibaudo G, Mescot X, Faraone L, Cristoloveanu S (2016) Interface trap density evaluation on bare silicon-on-insulator wafers using the quasistatic capacitance technique. J Appl Phys 119:175702

Wang Baomin Ru, Guoping JY, Xinping Qu, Bingzong Li, Ran L (2009) Capacitance–voltage characterization of fully silicided gated MOS capacitor. J Semicond 30:034002–034011

Ren M, Ye C-Y, Zhou J-Y, Zhang X, Zheng F, Ma R-Y, Li Z-H, Zhang Bo (2023) A non-quasi-static model for nanowire gate-all-around tunneling field-effect transistors. Chin Phys B 32:068501–068511

Recart F, Cuevas A (2006) Application of junction capacitance measurements to the characterization of solar cells. IEEE Trans Electron Devices 53:442–448

Wang H, Wang J, Yan X, Shi J, Tian H, Geng Y, Yan D (2006) Ambipolar organic field-effect transistors with air stability, high mobility, and balanced transport. Appl Phys Lett 88:133508

Belanche M, Kumar P, Woerle J, Stark R, Grossner U (2022) Sensitivity of Dit extraction at the SiO2/SiC interface using quasi-static capacitance-voltage measurements. Mater Sci Forum 1062:346–350

Boukredimi A (2014) New capacitance–voltage model for linearly graded junction. J Comput Electron 13:477–489

Chen Y-M, Lin C-F, Lee J-H, Huang JianJang (2008) Quasi-static capacitance–voltage characterizations of carrier accumulation and depletion phenomena in pentacene thin film transistors. Solid-State Electron 52:269–274

Fare T, Spetz A, Armgarth M, Lundström I (1988) Quasi static and high frequency C(V)-response of thin platinum metal-oxide-silicon structures to ammonia. Sens Actuators 14:369–386

Kumari A, Kumar S, Sharma TK, Das MK (2019) On the C-V characteristics of nanoscale strained gate-all-around Si/SiGe MOSFETs. Solid State Electron 154:36–42

Lee S, Jeon YW, Kim S, Kong D, Kim DH, Kim DM (2011) Comparative study of quasi-static and normal capacitance–voltage characteristics in amorphous Indium-Gallium-Zinc-Oxide thin film transistors. Solid-State Electron 56:95–99

Kuhn M (1970) A quasi-static technique for MOS C-V and surface state measurements. Solid-State Electron 13:873–885

Silvaco ATLAS User Manual (TCAD Version: ATLAS 5.19.20.R, 2023).

Yeo Y-C, King T-J, Chenming Hu (2002) Metal-dielectric band alignment and its implications for metal gate complementary metal-oxide-semiconductor technology. J Appl Phys 92:7266–7271

Mondal K, Hasan Md.M, Arafath Y, Alam K (2016) Results Phys 6:339–341

Schmitz J, Weusthof MHH, Hof AJ (2004) Leakage current correction in quasi-static C-V measurements. Proc. IEEE 2004 Int. Conference on Microelectronic Test Structures, Vol 17, p 179–181

Razavi B (2002) Design of Analog CMOS Integrated Circuits. Tata McGraw-Hill Edition

Hinkle CL, Fulton C, Nemanich RJ, Lucovsky G (2004) Enhanced tunneling in stacked gate dielectrics with ultra-thin HfO2 (ZrO2) layers sandwiched between thickers SiO2 layers. Appl Surf Sci 566–568:1185–1189

Chang YH, Lin CA, Liu YT, Chiang TH, Lin HY, Huang ML, Lin TD, Pi TW, Kwo J, Hong M (2012) Effective passivation of In0.2Ga0.8As by HfO2 surpassing Al2O3 via in-situ atomic layer deposition. Appl Phys Lett 101:172104–172105

Acknowledgements

One of the authors, Sanjay, acknowledges the financial support in form of SRF from the University Grants Commission (UGC), New Delhi, India.

Funding

Not Applicable.

Author information

Authors and Affiliations

Contributions

The work has been done in collaborative manner with the authors collectively conceptualising the idea of the work including the structure of the device. Dr. Sanjay who specialises in simulation on Silvaco, took up the work on setup of the devices on the simulator and ran the simulations. Dr. Vibhor Kumar along with Dr. Sanjay created the various viewgrams and the results in the present form. The work was mainly done in the laboratory of Dr. Anil Vohra who brought out the novelty of the work that helped to complete the article in its present form.

Corresponding author

Ethics declarations

Ethical Approval

Not Applicable.

Consent of Publications

THE AUTHORs AGREE FOR PUBLICATIONS.

Consent of Participate

AUTHORs AGREE.

Competing Interests

The authors declare no competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Sanjay, Kumar, V. & Vohra, A. Quantization Effect in N-Channel Inversion Mode Si, In0.53Ga0.47As and Ge Based Double Gate MOSFET Using Quasi-Static Capacitance–Voltage Characteristics for Upcoming Sub 10 nm Technology Node. Silicon (2024). https://doi.org/10.1007/s12633-024-02919-8

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s12633-024-02919-8