Abstract

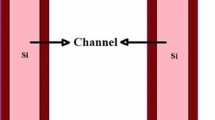

In this paper, for the first time, an optimized asymmetric U-shaped TFET, suitable for low power application, has been proposed after a hardcore performance analysis, considering the real-time adverse effect of gate/drain leakage phenomena known for deteriorating the subthreshold behaviour of a TFET. Two-level optimization – device-architecture level and gate-oxide level – remains the key factor of the work, ensuring its applicability even under extreme low power. For the proposed device with SiO2 as the material for asymmetric oxide arm, 7 nm turns out to be the optimized thickness, whereas it drops down to 5 nm and 4 nm, respectively, for Al2O3 and HfO2 arms. After a rigorous performance analysis, in terms of OFF-current, ON-current-OFF-current ratio, IDS-range for sub-60-mV/decade subthreshold swing, footprint, footprint-delay product, power-delay product, footprint-leakage-power density, the asymmetric TFET device with 5-nm asymmetric oxide arm of Al2O3 is found to be the most optimized device for the low power operation.

Similar content being viewed by others

Data Availability

The datasets generated during and/or analysed during the current study are available from the corresponding author on reasonable request.

References

Pu Y, Shi C, Samson G, Park D, Easton K, Beraha R, Newham A, Lin M, Rangan V, Chatha K, Butterfield D, Attar R (2018) A 9-mm2 ultra-low-power highly integrated 28-nm CMOS SoC for internet of things. IEEE J. Solid-State Circuits 53:936–948. https://doi.org/10.1109/JSSC.2017.2783680

Zhang X, Lok M, Tong T, Lee SK, Reagen B, Chaput S, Duhamel PEJ, Wood RJ, Brooks D, Wei GY (2017) A fully integrated battery-powered system-on-Chip in 40-nm CMOS for closed-loop control of insect-scale Pico-aerial vehicle. IEEE J. Solid-State Circ 52:2374–2387. https://doi.org/10.1109/JSSC.2017.2705170

Suguna M, Kaveri R, Sree VAN, Hemalatha M, Balamurugan NB (2021) Modeling and simulation based investigation of triple material surrounding gate tunnel FET for low power application. Silicon. https://doi.org/10.1007/s12633-021-01368-x

Mallik A, Chattopadhyay A (2012) Tunnel field-effect transistors for analog/mixed-signal system-on-Chip applications. IEEE Trans. On Electron Devices 59:888–894. https://doi.org/10.1109/TED.2011.2181178

Macko D, Jelemenska K, Cicak P (2018) Simplifying low-power SoC top-down design using the system-level abstraction and the increased automation. Integration 63:101–114. https://doi.org/10.1016/j.vlsi.2018.06.001

Zhu J, Zhao Y, Huang Q, Chen C, Wu C, Jia R, Huang R (2017) Design and simulation of a novel Graded-Channel heterojunction tunnel FET with high ION/IOFF ratio and steep swing. IEEE Electron Device Lett 38:1200–1203. https://doi.org/10.1109/LED.2017.2734679

Tripathy MR, Singh AK, Samad A, Chander S, Baral K, Singh PK, Jit S (2020) Device and circuit-level assessment of GaSb/Si heterojunction vertical tunnel-FET for low-power applications. IEEE Trans. Electron devices 67:1285–1292. https://doi.org/10.1109/TED.2020.2964428

Zhao Y, Liang Z, Huang Q, Chen C, Yang M, Sun Z, Zhu K, Wang H, Liu S, Liu T, Peng Y, Han G, Huang R (2019) A novel negative capacitance tunnel FET with improved subthreshold swing and nearly non-hysteresis through hybrid modulation. IEEE Electron Device Lett 40:989–992. https://doi.org/10.1109/LED.2019.2909410

Kukital K, Uechi T, Shimokawa J, Goto M, Yokota Y, Kawanaka S (2018) Simulation of planar single-gate Si tunnel FET with average subthreshold swing of less than 60 mV/decade for 0.3 V operation. Jpn. J. Appl. Phys. https://doi.org/10.7567/JJAP.57.04FD09

Pasupathy KR, Manivannan TS, Lakshminarayanan G (2021) A review of engineering techniques to suppress Ambipolarity in tunnel FET. Silicon. https://doi.org/10.1007/s12633-021-01018-2

Aydin C, Zaslavsky A, Luryi S, Cristoloveanu S, Mariolle D, Fraboulet D, Deleonibus S (2004) Lateral inteband tunneling transistor on silicon-on-insulator. Appl Phys Lett 84:1780–1782. https://doi.org/10.1063/1.1668321

Appenzeller J, Lin YM, Knoch J, Avouris P (2004) Band-to-band tunneling in carbon nanotube field-effect transistors. Phys Rev Lett 93. https://doi.org/10.1103/PhysRevLett.93.196805

Bhuwalka K, Sedlmaier S, Ludsteck A, Tolksdorf C, Schulze J, Eisele I (2004) Vertical tunnel field-effect transistor. IEEE Trans Electron Devices 51:279–282. https://doi.org/10.1109/TED.2003.821575

Toh EH, Wang GH, Samudra G, Yeo YC (2007) Device physics and design of double-gate tunneling field-effect transistor by silicon film thickness optimization. Appl Phys Lett 90:263507. https://doi.org/10.1063/1.2748366

Nayfeh OM, Chleirigh CN, Hennessy J, Gomez L, Hoyt JL, Antoniadis DA (2008) Design of tunneling field-effect transistors using strained-silicon/strained-germanium type—II staggered heterojunctions. IEEE Electron Device Lett. 29:1074–1077. https://doi.org/10.1109/LED.2008.2000970

Appenzeller J, Lin YM, Knoch J, Chen Z, Avouris P (2005) Comparing carbon nanotube transistors—the ideal choice: a novel tunneling device design. IEEE Trans. Electron Devices 52:2568–2576. https://doi.org/10.1109/TED.2005.859654

Choi WY, Park B, Lee JD, Liu TK (2007) Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett 28:743–745. https://doi.org/10.1109/LED.2007.901273

Kim SW, Kim JH, Liu TJK, Choi WY, Park BG (2016) Demonstration of L shaped tunnel field effect transistors. IEEE Trans Electron Devices 63:1774–1778. https://doi.org/10.1109/TED.2015.2472496

Wang W, Wang PF, Zhang CM, Lin X, Liu XY, Sun QQ, Zhou P, Zhang DW (2014) Design of U-Shape Channel tunnel FETs with SiGe source regions. IEEE Trans on Electron Devices 61:193–197. https://doi.org/10.1109/TED.2013.2289075

Chattopadhyay A, Mallik A, Omura Y (2015) Device optimization and scaling properties of a gate-on-germanium source tunnel field-effect transistor. Superlattice Microst 82:415–429. https://doi.org/10.1016/j.spmi.2015.02.022

Kao K, Verhulst AS, Vandenberghe WG, Soree B, Groeseneken G, Meyer KD (2012) Direct and indirect band-to-band tunneling in germanium-based TFETs. IEEE Trans. Electron Devices. 59:292–301. https://doi.org/10.1109/TED.2011.2175228

Yoon YJ, Seo JH, Kang HS, Kim YJ, Bae JH, Cho ES (2014) Effect of spacer dielectrics on performance characteristics of Ge-based tunneling field-effect transistors. Jpn J Appl Phys 53:06JE05. https://doi.org/10.7567/JJAP.53.06JE05

Chen S, Wang S, Liu H, Han T, Xie H, Chong C (2020) A novel Dopingless fin-shaped SiGe Channel TFET with improved performance. Nanoscale Res Lett 15:202. https://doi.org/10.1186/s11671-020-03429-3

The International Technology Roadmap for Semiconductors (ITRS), 2013, [Online]. Available: http://www.itrs2.net

SILVACO Inc. (2017) ATLAS User’s manual. Santa Clara, CA, A 2-D Device Simulator Software Package

Mallik A, Chattopadhyay A, Guin S, Karmakar A (2013) Impact of a spacer–drain overlap on the characteristics of a silicon tunnel field-effect transistor based on vertical tunnelling. IEEE Trans Electron Devices 60:935–943. https://doi.org/10.1109/TED.2013.2237776

Iannaccone G, Curatola G, Fiori G. in International Conference on Simulation of Semiconductor Processes and Devices proceedings 2004; 275. https://doi.org/10.1007/978-3-7091-0624-2

Selberherr S (1984) Analysis and simulation of semiconductor devicesfirst edn. Springer, Verlag Wien

Ionesue AM, Riel H (2011) Tunnel field effect transistors as energy efficient electronics switches. Nature 479:329–337. https://doi.org/10.1038/nature10679

Boucart K, Ionescu AM (2007) Double-gate tunnel FET with high-κ gate dielectric. IEEE Trans on Electron Devices 54:1725–1733. https://doi.org/10.1109/TED.2007.899389

Acknowledgements

Not applicable.

Funding

No funds, grants, or other support was received for conducting this study. The authors have no financial or proprietary interests in any material discussed in this article.

Author information

Authors and Affiliations

Contributions

All the authors made substantial contribution to the conception and design of the work. Material preparation and data acquisition were performed by Suman Das; analysis or interpretation of data was done by Avik Chattopadhyay and Suchismita Tewari. The first draft of the manuscript was written by Suchismita Tewari and all authors commented on previous versions of the manuscript. All authors read and approved the final manuscript.

Corresponding author

Ethics declarations

Ethics Approval

Not applicable.

Consent to Participate

Not applicable.

Consent for Publication

All the authors are agreed with the content and all have full consent for submission and subsequent publication.

Research Involving Human Participants and/or Animals

Not applicable.

Conflict of Interest

There are no potential conflicts of interest.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Das, S., Chattopadhyay, A. & Tewari, S. Architecture- and Gate-Oxide-Level Optimization of a Si-Based Asymmetric U-TFET for Low Power Operation: a Real-Time Gate/Drain Electrostatic Based Leakage Perspective. Silicon 14, 10719–10727 (2022). https://doi.org/10.1007/s12633-022-01810-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-022-01810-8