Abstract

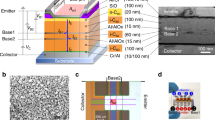

The present paper aims to propose silicon-based double-gate vertical TFET (DGV-TFET) for implementing different Boolean functions involving basic gates and universal gates. The motivation behind the usage of the vertical TFET for device design is that fewer transistors are required in comparison to the CMOS and MOSFET usage. On modification of the architectural design of the double gate Vertical TFET slightly with an appropriate choice of parameters, and logic functions, namely AND, OR, NAND and NOR, the proposed device can be implemented. A suitable combination of the inhibition functions and different logic functions are attained within single device. The implementations illustrate unique characteristic of TFET like ambipolar conduction as well as tunnelling dependency upon gate–source overlap which are achieved to realize mentioned Boolean functions. An n-type DGV-TFET is used to create OR logic functions, whereas a p-type DGV-TFET is used to implement NAND logic functions by independently biasing the two gates against different combinations of input logics. The AND and NOR logic functions are realised in the proposed DGV-TFET device by overlapping the gate and source of both n-type and p-type, respectively.

Similar content being viewed by others

Data Availability

Not applicable.

Code Availability

Not Applicable.

References

Park DG, Cha TH, Lim KY, Cho HJ, Kim TK, Jang SA, Suh YS, Misra V, Yeo IS, Roh JS, Park JW, Yoon HK (2001) Robust ternary metal gate electrodes for dual gate CMOS devices. In: IEDM Tech Dig, pp 616–619

Polishchuk I, Ranade P, King TJ, Hu C (2002) Dual work function metal gate CMOS transistors by Ni–Ti interdiffusion. IEEE Electron Device Lett 23:200–202

Wong CY, Sun JYC, Taur Y, Oh CS, Angelucci R, Davari B (1988) Doping of n and p polysilicon in a dual-gate process. In: IEDM Tech Dig, pp 238–241

Pfiester JR, Baker FK, Mele TC, Tseng HH, Tobin PJ, Hayden JD, Miller JW, Gunderson CD, Parrillo LC (1990) The effects of boron penetration on p polysilicon gates MOS devices. IEEE Trans Electron Devices 37:1842–1851

Mookerjea S, Krishnan R, Datta S, Narayanan V (2009) Effective capacitance and drive current for tunnel FET (TFET) CV/I estimation. IEEE Trans Electron Devices 56(9):2092–2098. https://doi.org/10.1109/TED.2009.2026516

Ahish S, Sharma D, Kumar YBN, Vasantha MH (2015) Performance enhancement of novel InAs/Si hetero double-gate tunnel FET using Gaussian doping. IEEE Trans Electron Devices 63(1):288–295. https://doi.org/10.1109/TED.2015.2503141

Liu L, Mohata D, Datta S (2012) Scaling length theory of double-gate interband tunnel field-effect transistors. IEEE Trans. Electron Devices 59(4):902–908. https://doi.org/10.1109/TED.2012.2183875

Khatami Y, Banerjee K (2009) Steep subthreshold slope n- and p-Type Tunnel-FET devices for low-power and energy-efficient digital circuits. IEEE Trans Electron Devices 56:2752–2761

Wadhwa G, Raj B (2020) An analytical modeling of charge plasma based Tunnel Field Effect Transistor with impacts of gate underlap region. Superlattices Microstruct 142:106512

Boucart K, Ionescu AM (2007) Double gate tunnel FET with high k gate dielectric. IEEE Trans Electron Devices 54(7):1725–1733

Wadhwa G, Singh J (2020) "Implementation of linearly modulated work function A σ B 1 – σ gate electrode and Si 0.55 Ge 0.45 N+ pocket doping for performance improvement in gate stack vertical-TFET" Appl Phys A 126(11):1–11

Wadhwa G, Singh J, Raj B (2021) Design and investigation of doped triple metal double gate vertical TFET for performance enhancement. Silicon 13(6):1839–1849

Saurabh S, Kumar MJ (2016) Fundamentals of tunnel field-effect transistors. CRC Press, Boca Raton. https://doi.org/10.1201/9781315367354-3

Singh J, Wadhawa G (2021) Novel linear graded binary metal alloy PαQ1-α gate electrode and middle N+ Pocket Si0. 5Ge0. 5 Vertical TFET for High Performance. Silicon 13(7):2137-2144

Wadhwa G, Raj B (2021) Surface potential modeling and simulation analysis of dopingless TFET biosensor. Silicon. https://doi.org/10.1007/s12633-021-01011-9

Jain G, Sawhney RS, Kumar R, Wadhwa G (2021) Analytical modeling analysis and simulation study of dual material gate underlap dopingless TFET. Superlattices Microstruct 153:106866

Krishnamohan T, Kim D, Nguyen CD, Jungemann C, Nishi Y, Saraswat KC (2006) High-mobility low band-to-band tunneling strainedgermanium double-gate heterostructure FETs: Simulations. IEEE Trans Electron Devices 53(5):1000–1009

Saurabh S, Kumar MJ (2010) Estimation and compensation of process induced variations in nanoscale tunnel field effect transistors (TFETs) for improved reliability. IEEE Trans Device Mater Rel 10(3):390–395

Banerjee S, Garg S, Saurabh S (2018) Realizing logic functions using single double-gate tunnel FETs: a simulation study. IEEE Electron Device Lett 39(5):773–776

Garg S, Saurabh S (2019) Implementing logic functions using independently-controlled gate in double-gate tunnel FETs: investigation and analysis. IEEE Access 7:117591–117599

Kamath A, Chen Z, Shen N, Singh N, Lo GQ, Kwong D-L, Kasprowicz D, Pfitzner A, Maly W (2012) Realizing AND and OR functions with single vertical-slit field-effect transistor. IEEE Electron Device Lett 33(2):152–154. https://doi.org/10.1109/LED.2011.2176309

Nigam K, Kondekar P, Sharma D (2016) High frequency performance of dual metal gate vertical tunnel field effect transistor based on work function engineering. Micro & Nano Letters 11(6):319–322. https://doi.org/10.1049/mnl.2015.0526

Padilla JL, Gamiz F, Godoy A (2012) Impact of quantum confinement on gate threshold voltage and subthreshold swings in double-gate tunnel FETs. IEEE Trans Electron Devices 59(12):3205–3211. https://doi.org/10.1109/TED.2012.2216531

Chiang MH, Kim K, Chuang CT, Tretz C (2006) High-density reduced-stack logic circuit techniques using independent-gate controlled double-gate devices. IEEE Trans Electron Devices 53(9):2370–2377. https://doi.org/10.1109/TED.2006.881052

Manual, ATLAS User’S (2018) Device simulation software. Silvaco Int., Santa Clara, CA

Vandenberghe WG, Sorée B, Magnus W, Groeseneken G, Fischetti MV (2011) Impact of field-induced quantum confinement in tunneling field-effect devices. Appl Phys Lett 98(14):143503. https://doi.org/10.1063/1.3573812

Abdi DB, Jagadesh Kumar M (2014) Controlling ambipolar current in tunneling FETs using overlapping gate-on-drain. IEEE J Electron Devices Soc 2(6):187–190

Wang H, Chang S, Hu Y, He H, He J, Huang Q, He F, Wang G (2014) A novel barrier controlled tunnel FET. IEEE Electron Device Lett 35(7):798–800

Author information

Authors and Affiliations

Contributions

All authors contributed to the design and simulation. Material preparation, data collection, and analysis were performed by Mirwaiz Rahaman and Pallab Banerji. The first draft of the manuscript was written by Mirwaiz Rahaman. All authors commented on previous versions of the manuscript. All authors read and approved the final manuscript.

Corresponding author

Ethics declarations

Ethics Approval and Consent to Participate

Not Applicable.

Consent for Publication

Not Applicable.

Conflicts of interest/Competing Interests

The authors have declared that no competing interests exist.

Disclosure of Potential Conflicts of Interest

No conflicts to report.

Research Involving Human Participants and/or Animals

Not applicable.

Informed Consent

Not applicable.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Rahaman, M., Banerji, P. Design and Realization of Logic Gates or Functions Using Vertical TEFT Structures. Silicon 14, 10413–10422 (2022). https://doi.org/10.1007/s12633-022-01752-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-022-01752-1