Abstract

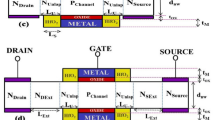

In this paper, we are proposing a gate oxide stack source halo symmetric and asymmetric underlap extension nanowire MOSFET with HfO2 spacer at 10 nm regime. The increased doping concentration at the source channel vicinity decreases the depletion width which increases the energy barrier levels at the source-channel interface and the lightly doped underlap increases the tunneling width in the lateral direction. Because of increased barrier width and height, the proposed device exhibits lowest OFF-state current 6.61 × 10–14 Amp and high \(\frac{{I}_{ON}}{{I}_{OFF}}\) ratio 2.48 × 108. Further, the proposed device performance is analyzed for the symmetrical and asymmetrical underlap, extension length variations. The device produces the highest improvement in the performance metrics for symmetric source-drain underlap extension as compared to other variations. The \(\frac{{I}_{ON}}{{I}_{OFF}}\) ratio of the device improves by 96% with symmetric source-drain underlap at LSUnlap = LDUnlap = LSDUnlap = 1.5 × LG and 76% with symmetric source-drain extension at LSExt = LDExt = LSDExt = 0.5 × LG. Furthermore, the \(\frac{{I}_{ON}}{{I}_{OFF}}\) ratio of the device improves by 25% with the gate oxide stack. As a result of the lower leakage current and high \(\frac{{I}_{ON}}{{I}_{OFF}}\) ratio (~ 108) even in the 10 nm regime, the proposed device is used in ultra-low power and memory applications.

Similar content being viewed by others

Data Availability

There are no linked research data sets for this submission. The following reason is given: No data was used for the research described in the article.

References

Kuhn KJ (2012) Considerations for Ultimate CMOS Scaling. IEEE Trans Electron Devices 59(7):1813–1828

Kranti A, Armstrong GA (2008) High Tolerance to Gate Misalignment in Low Voltage Gate-Underlap Double Gate MOSFETs. IEEE Electron Device Lett 29(5):503–505. https://doi.org/10.1109/LED.2008.920281

Xie Q, Lee C-J, Xu J, Wann C, Sun JY-C, Taur Y (2013) Comprehensive Analysis of Short-Channel Effects in Ultrathin SOI MOSFETs. IEEE Trans Electron Devices 60(6):1814–1819. https://doi.org/10.1109/TED.2013.2255878

S. -Y. Wu et al., "An enhanced 16nm CMOS technology featuring 2nd generation FinFET transistors and advanced Cu/low-k interconnect for low power and high performance applications," 2014 IEEE International Electron Devices Meeting, 2014, pp. 3.1.1–3.1.4, https://doi.org/10.1109/IEDM.2014.7046970.

Razavieh A, Zeitzoff P, Nowak EJ (2019) Challenges and Limitations of CMOS Scaling for FinFET and Beyond Architectures. IEEE Trans Nanotechnol 18:999–1004. https://doi.org/10.1109/TNANO.2019.2942456

Zheng P, Connelly D, Ding F, Liu TK (2015) FinFET Evolution Toward Stacked-Nanowire FET for CMOS Technology Scaling. IEEE Trans Electron Devices 62(12):3945–3950. https://doi.org/10.1109/TED.2015.2487367

Bidal G et al (2009) Gate-All-Around technology: taking advantage of ballistic transport ? Proc Eur Solid State Device Res Conf 2009:315–318. https://doi.org/10.1109/ESSDERC.2009.5331466

Singh N, Buddharaju KD, Manhas SK, Agarwal A, Rustagi SC, Lo GQ, Balasubramanian N, Kwong D-L (2008) Si, SiGe nanowire devices by top–down technology and their applications. IEEE Trans Electron Device 55(11):3107–3118

Han K, Zhang Y, Deng Z (2020) A Simulation Study of Gate-All-Around Nanowire Transistor With a Core-Substrate. IEEE Access 8:62181–62190. https://doi.org/10.1109/ACCESS.2020.2983724

Song Y et al (2010) High-performance silicon nanowire gate-all-around nMOSFETs fabricated on bulk substrate using CMOS-compatible process. IEEE Electron Device Lett 31(12):1377–1379

Barraud S et al (2013) Enhanced performance of P-FET omega-gate SoI nanowire with recessed-SiGe source-drain down to 13-nm gate length. IEEE Electron Device Lett 34(9):1103–1105

Kaushal G, Jeong H, Maheshwaram S, Manhas S, Dasgupta S, Jung S (2015) Low power SRAM design for 14nm GAA Si-nanowire technology. Microelectron J 46(12):1239–1247. https://doi.org/10.1016/j.mejo.2015.10.016

Thingujam T, Dai Q, Kim E, Lee J-H (2021) A Simulation Study on the Effects of Interface Charges and Geometry on Vertical GAA GaN Nanowire MOSFET for Low-Power Application. IEEE Access 9:101447–101453. https://doi.org/10.1109/ACCESS.2021.3097367

Fan J, Li M, Xu X, Yang Y, Xuan H, Huang R (2015) Insight into gate-induced drain leakage in silicon nanowire transistors. IEEE Trans Electron Devices 62(1):213–219

Hur J et al (2016) Comprehensive analysis of gate-induced drain leakage in vertically stacked nanowire FETs: Inversion-mode versus junctionless mode. IEEE Electron Device Lett 37(5):541–544

Sahay S, Kumar MJ (2016) Controlling L-BTBT and volume depletion in nanowire JLFETs using core–shell architecture. IEEE Trans Electron Devices 63(9):3790–3794

Sahay S, Kumar MJ (2016) Insight into lateral band-to-band-tunneling in nanowire junctionless FETs. IEEE Trans Electron Devices 63(10):4138–4142

Sahay S, Kumar MJ (2016) A Novel Gate-Stack-Engineered Nanowire FET for Scaling to the Sub-10-nm Regime. IEEE Trans Electron Devices 63(12):5055–5059

Sachid AB, Chen M-C, Hu C (2016) FinFET with high-k spacers for improved drive current. IEEE Electron Device Lett 37(7):835–838

A. B. Sachid et al., “Sub-20 nm gate length FinFET design: Can high-κ spacers make a difference?” in IEDM Tech. Dig. Dec. 2008, pp. 1–4.

Sachid AB, Manoj CR, Sharma DK, Rao VR (2008) Gate Fringe-Induced Barrier Lowering in Underlap FinFET Structures and Its Optimization. IEEE Electron Device Lett 29(1):128–130. https://doi.org/10.1109/LED.2007.911974

Chen G, Li M, Fan J, Yang Y, Zhang H, Huang R (2016) Multi-VT design of vertical channel nanowire FET for sub-10nm technology node. IEEE Int Nanoelectronics Conf (INEC) 2016:1–2

Singh A, Chaudhury S, Sarkar CK, Hussain I, Ganguly A (2018) A Multi Vt Approach for Silicon Nanotube FET with Halo Implantation for Improved DIBL. IEEE Electron Devices Kolkata Conf (EDKCON) 2018:328–331. https://doi.org/10.1109/EDKCON.2018.8770441

Kale S, Kondekar PN (2017) Design and Investigation of Dielectric Engineered Dopant Segregated Schottky Barrier MOSFET With NiSi Source/Drain. IEEE Trans Electron Devices 64(11):4400–4407

Lo S-H, Buchanan DA, Taur Y, Wang W (1997) Quantum-mechanical modeling of electron tunneling current from the inversion layer of ultrathin-oxide nMOSFET’s. IEEE Electron Device Lett 18(5):209–211. https://doi.org/10.1109/55.568766

Cheng B et al (1999) The impact of high-κ gate dielectrics and metal gate electrodes on sub-100 nm MOSFETs. IEEE Trans Electron Devices 46(7):1537–1544. https://doi.org/10.1109/16.772508

Amin SI, Sarin RK (2016) Enhanced analog performance of dopingless dual material and gate stacked architecture of junctionless transistor with high-k spacer. Appl Phys A Solids Surf 122(4):380. https://doi.org/10.1007/s00339-016-9904-2

Sharma RK, Gupta M, Gupta RS (2011) TCAD assessment of device design technologies for enhanced performance of nanoscale DG MOSFET. IEEE Trans Electron Devices 58(9):2936–2943. https://doi.org/10.1109/TED.2011.2160065

Chang H, Adams B, Chien P, Li J, Woo JCS (2013) Improved Subthreshold and Output Characteristics of Source-Pocket Si Tunnel FET by the Application of Laser Annealing. IEEE Trans Electron Devices 60(1):92–96. https://doi.org/10.1109/TED.2012.2228006

Guin S, Chattopadhyay A, Karmakar A, Mallik A (2014) Impact of a Pocket Doping on the Device Performance of a Schottky Tunneling Field-Effect Transistor. IEEE Trans Electron Devices 61(7):2515–2522. https://doi.org/10.1109/TED.2014.2325068

Bufler FM, Ritzenthaler R, Mertens H, Eneman G, Mocuta A, Horiguchi N (2018) Performance Comparison of ${n}$ –Type Si Nanowires, Nanosheets, and FinFETs by MC Device Simulation. IEEE Electron Device Lett 39(11):1628–1631. https://doi.org/10.1109/LED.2018.2868379

Wong HY, Braga N, Mickevicius RV (2018) Enhancement-Mode Recessed Gate and Cascode Gate Junctionless Nanowire With Low-Leakage and High-Drive Current. IEEE Trans Electron Devices 65(9):4004–4008. https://doi.org/10.1109/TED.2018.2856740

Espiñeira G, Nagy D, Indalecio G, García-Loureiro AJ, Kalna K, Seoane N (2019) Impact of Gate Edge Roughness Variability on FinFET and Gate-All-Around Nanowire FET. IEEE Electron Device Lett 40(4):510–513. https://doi.org/10.1109/LED.2019.2900494

Acknowledgements

“The authors would like to thank Department of Electronics and Communication Engineering, National Institute of Technology Silchar for providing necessary computation tools.”

Funding

The authors of the manuscript did not receive any funding, grants, or in kind support in support of the research or the preparation of the manuscript.

Author information

Authors and Affiliations

Contributions

Author 1 (P.Kiran Kumar): Conceived and design the analysis, Contributed data and analysis tools, and wrote the paper. Author 2 (B Balaji): Performed the analysis, Calibrated the results, and wrote the paper. Author 3 (K.Srinivasa Rao): Worked data analysis of the paper.

Corresponding author

Ethics declarations

Ethical Approval and Consent to participate

“All procedures performed in studies involving human participants were in accordance with the ethical standards of the institutional and/or national research committee and with the 1964 Helsinki declaration and its later amendments or comparable ethical standards.

Informed Consent

“Informed consent was obtained from all individual participants included in the study.”

Research involving Human Participants and/ or Animals

Not Applicable.

Consent for publication

“Informed consent was obtained from all individual participants included in the study.”

Conflict of Interest

All authors have participated in (a) conception and design, or analysis and interpretation of the data; (b) drafting the article or revising it critically for important intellectual content; and (c) approval of the final version. This manuscript has not been submitted to, nor is under review at, another journal or other publishing venue. The authors have no affiliation with any organization with a direct or indirect financial interest in the subject matter discussed in the manuscript. The following authors have affiliations with organizations with direct or indirect financial interest in the subject matter discussed in the manuscript:

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kumar, P.K., Balaji, B. & Rao, K.S. Performance analysis of sub 10 nm regime source halo symmetric and asymmetric nanowire MOSFET with underlap engineering. Silicon 14, 10423–10436 (2022). https://doi.org/10.1007/s12633-022-01747-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-022-01747-y