Abstract

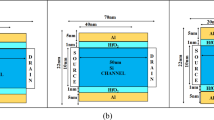

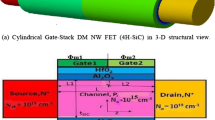

In this paper, Gallium Nitride (GaN) based Dielectric Engineered High-K GaN Schottky Nanowire Field Effect Transistor (DE-HK-GaN-SNWFET) is examined for enhancing analog performance for high-frequency applications using ATLAS 3D device simulator. Owed to the wider bandgap, a high breakdown field, and good transport properties GaN and Aluminium Oxide (Al2O3) is proposed to replace the conventional Silicon (Si) and Silicon Oxide (SiO2) respectively in Schottky Nanowire FET. A stack of Al2O3 with hafnium dioxide (HfO2) has been anticipated because of high thermal constancy, high dielectric constant, and high consistency of HfO2 with preventive interface eminence. An in-depth study is done between GaN and Si devices named Dielectric Engineered High-K GaN Schottky Nanowire FET (DE-HK-GaN-SNWFET), GaN Schottky Nanowire FET (GaN-SNWFET), High-K -Silicon Schottky Nanowire FET (HK-Si-SNWFET), and Silicon Schottky Nanowire FET (Si-SNWFET). Appraised electrical parameters show that the device passivated with a stack of Al2O3/HfO2 with GaN as channel material shows better results in terms of drain currents, transconductance, output conductance, Gate Capacitance, Cut off Frequency, unilateral power gain, Maximum Transducer Power Gain, subthreshold swing, threshold voltage, and Frequency Transconductance Product. The scattering parameters, i.e., reflection coefficient (S11, S22) and transmission coefficient (S12, S21), affirm analog performance of DE-HK-GaN-SNWFET than other contemplated devices.

Similar content being viewed by others

Data Availability

Not Applicable.

References

International technology roadmap for semiconductors (ITRS), 2014 [Online] Available: http://public.itrs.net

Dimitrijev S, Han J, Haasmann D, Moghadam HA, and Aminbeidokhti A, (2014) "A Survey of Wide Band Gap Power Semiconductor Devices" in Proceedings of International Conference on Microelectronics (ICM) ,p. 43

Y. Jin, "Simulation methodology to compare emerging technologies for alternatives to silicon gigascale logic device." (2007)

Yoon YJ, Lee JS, Kim DS, Lee JH, Kang IM (2020) Gallium nitride normally off MOSFET using dual-metal-gate structure for the improvement in current drivability. Electronics 9(9):1402

Millan J, Philippe G, Perpiñà X, Pérez-Tomás A, Rebollo J (2013) A survey of wide bandgap power semiconductor devices. IEEE Trans Power Electron 29(5):2155–2163

Sugiura S, Hayashi Y, Kishimoto S, Mizutani T, Kuroda M, Ueda T, Tanaka T (2010) Fabrication of normally-off mode GaN and AlGaN/GaN MOSFETs with HfO2 gate insulator. Solid State Electron 54(1):79–83

Madan J, Dassi M, Pandey R, Chaujar R, Sharma R (2020) Numerical analysis of Mg2Si/Si heterojunction DG-TFET for low power/high performance applications: impact of non-idealities. Superlattice Microst 139:106397

Madan J, Pandey R, Sharma R, Chaujar R (2019) Impact of metal silicide source electrode on polarity gate induced source in junctionless TFET. Appl Physics A 125(9):1–7

Sharma P, Madan J, Pandey R, Sharma R (2021) RF analysis of double-gate junctionless tunnel FET for wireless communication systems: a non-quasi static approach. J Electron Mater 50(1):138–154

Kumar P, Vashisht M, Gupta N, Gupta R (2021) Subthreshold current modeling of stacked dielectric triple material cylindrical gate all around (SD-TM-CGAA) Junctionless MOSFET for low power applications. Silicon:1–9

Kumar P, Gupta N, Sachdeva N, Sachdeva T, Vashishath M (2020) Performance investigation of dual-halo dual-dielectric triple material surrounding gate MOSFET with high-κ dielectrics for low power applications. J Semicond Technol Sci 20(3):297–304

Gupta N (2020) Sub-threshold modeling of dual-halo dual-dielectric triple-material surrounding-gate (DH-DD-TM-SG) MOSFET for improved leakages. J Eng Res 8(2):178–190

Gupta N, Kumar P (2021) Elicitation of scattering parameters of dual-halo dual-dielectric triple-material surrounding gate (DH-DD-TM-SG) MOSFET for microwave frequency applications. Adv Electr Electron Eng 19(1):66–73

Gupta N, Patel JK, Raghav AK (2018) An accurate 2D analytical model for Transconductance to drain current ratio (gm/id) for a dual halo dual dielectric triple material cylindrical gate all around MOSFETs. Int J Eng 31(7):1038–1043

Zhang L, Ma C, He J, Lin X, Chan M (2010) Analytical solution of subthreshold channel potential of gate underlap cylindrical gate-all-around MOSFET. Solid State Electron 54(8):806–808

Rewari S, Haldar S, Nath V, Deswal SS, Gupta RS (2016a) Numerical modeling of subthreshold region of junctionless double surrounding gate MOSFET (JLDSG). Superlattices Microstruct J 90:8–19

Goel A, Rewari S, Verma S, and Gupta RS, (2020) "Modeling of shallow extension engineered dual metal surrounding gate (SEE-DM-SG) MOSFET gate-induced drain leakage (GIDL)." Indian J Physics 1–10

Kumar M, Haldar S, Gupta M, Gupta RS (2014) Impact of gate material engineering (GME) on analog/RF performance of nanowire Schottky-barrier gate all around (GAA) MOSFET for low power wireless applications: 3D T-CAD simulation. Microelectron J 45(11):1508–1514

Zhu G, Zhou X, Lee TS, Ang LK, See GH, Lin S, Chin YK, Pey KL (2009) A compact model for undoped silicon- nanowire MOSFETs with Schottky-barrier source/drain. IEEE Trans Electron Devices 56(5):1100–1109

Larson JM, Snyder JP (2006) Overview and status of metal S/D Schottky-barrier MOSFET technology. IEEE Trans Electron Devices 53(5):1048–1058

Ho C, Chang Y (2017) Evaluation of Schottky barrier source/drain contact on gate-all-around polycrystalline silicon nanowire MOSFET. Mater Sci Semicond Process 61:150–155

Gang H, Gao J, Chen H, Cui J, Sun Z, Chen X (2014) Modulating the interface quality and electrical properties of HfTiO/InGaAs gate stack by atomic-layer-deposition-derived Al2O3 passivation layer. ACS Appl Mater Interfaces 6(24):22013–22025

Goel A, Rewari S, Verma S, Gupta RS (2020) High-K spacer dual-metal gate stack underlap junctionless gate all around (HK-DMGS-JGAA) MOSFET for high frequency applications. Microsyst Technol 26(5):1697–1705

Rewari S, Nath V, Haldar S, Deswal S, Gupta RS (2019) Hafnium oxide based cylindrical junctionless double surrounding gate (CJLDSG) MOSFET for high speed, high frequency digital and analog applications. Microsyst Technol 25(5):1527–1536

Kumar M, Haldar S, Gupta M, Gupta RS (2016) Physics based analytical model for surface potential and subthreshold current of cylindrical Schottky barrier gate all around MOSFET with high-k gate stack. Superlattice Microst 90:215–226

Nandy S, Srivastava S, Rewari S, Nath V, and Gupta RS, (2019) "Dual metal Schottky barrier asymmetric gate stack cylindrical gate all around (DM-SB-ASMGS-CGAA) MOSFET for improved analog performance for high frequency application." Microsyst Technol 1–10

ATLAS (2015) 3D Device Simulator, SILVACO International

Bertness KA, Sanders AW, Rourke DM, Harvey TE, Roshko A, Schlager JB, Sanford NA (2010) Controlled nucleation of GaN nanowires grown with molecular beam epitaxy. Adv Funct Mater 20(17):2911–2915

Wessely F, Krauss T, Schwalke U (2012) Virtually dopant-free CMOS: Midgap Schottky-barrier nanowire field-effect-transistors for high temperature applications. Solid State Electron 74:91–96

Robins LH, Horneber E, Sanford NA, Bertness KA, Brubaker MD, Schlager JB (2016) Raman spectroscopy based measurements of carrier concentration in n-type GaN nanowires grown by plasma-assisted molecular beam epitaxy. J Appl Phys 120(12):124313

Li W, Brubaker MD, Spann BT, Bertness KA, Fay P (2017) GaN nanowire MOSFET with near-ideal subthreshold swing. IEEE Electron Device Lett 39(2):184–187

Kale S. "Investigation of dual metal gate Schottky barrier MOSFET for suppression of ambipolar current." IETE J Res (2020): 1–6

Spaziani L, and Lucas L "(2018) Silicon, GaN and SiC: There's room for all: An application space overview of device considerations." In 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), pp. 8–11. IEEE

Kumar M, Pratap Y, Haldar S, Gupta M, Gupta RS (2017) Cylindrical gate all around Schottky barrier MOSFET with insulated shallow extensions at source/drain for removal of ambipolarity: a novel approach. J Semicond 38(12):124002

Kaur A, Mehra R, Saini A (2019) Hetero-dielectric oxide engineering on dopingless gate all around nanowire MOSFET with Schottky contact source/drain. AEU-Int Electron Commun 111:152888

Rewari S, (2020)"Core-Shell Nanowire Junctionless Accumalation Mode Field-Effect Transistor (CSN-JAM-FET) for High Frequency Applications-Analytical Study." Silicon 1–9

Goel A, Rewari S, Verma S, Gupta RS (2021) Novel dual-metal Junctionless nanotube field-effect transistors for improved analog and low-noise applications. J Electron Mater 50(1):108–119

Monthei LD (1999) The smith chart and S-parameters. In package electrical modeling, thermal modeling, and processing for GaAs wireless applications. Springer, Boston, pp 29–41

Acknowledgments

Authors are obligated to the Director, Maharaja Agrasen Institute of Technology for yielding essential resources to finish out this research effort.

Author information

Authors and Affiliations

Contributions

The authors have contributed mutually regarding this paper.

Corresponding author

Ethics declarations

Not Applicable.

Conflict of Interest

There are no conflicts of interest amongst the authors.

Consent to Participate

All the authors have complete consent to participate.

Consent for Publication

All the authors have complete consent for publication.

Ethics Approval

All the ethics have been followed.

Disclosure of Potential Conflicts of Interest

There are no conflicts of interest amongst the authors.

Research Involving Human Participants and/or Animals

No animals or human beings were harmed during this research.

Informed Consent

All the authors have Informed consent.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Sharma, S., Goel, A., Rewari, S. et al. Enhanced Analog Performance and High-Frequency Applications of Dielectric Engineered High-K Schottky Nanowire FET. Silicon 14, 9733–9749 (2022). https://doi.org/10.1007/s12633-022-01663-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-022-01663-1