Abstract

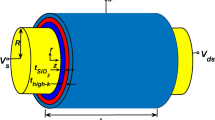

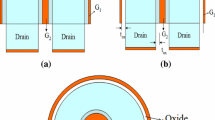

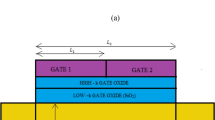

Stacked Dielectric Triple Material Cylindrical Gate All Around (SD-TM-CGAA) Junctionless MOSFET has been explored for low power applications. This paper presents an analytical model of subthreshold current of Stacked Dielectric Triple Material Cylindrical Gate All Around (SD-TM-CGAA) Junctionless MOSFET. The analytical results are compared with TMSG MOSFET and good agreement was obtained. The sub-threshold current of the device is very low and is considered for the implementation of CMOS inverter. A PMOS transistor is designed and the drive current of the PMOS transistor is tuned with the NMOS device to obtain the ideal matching in the drive current. A CMOS inverter has been designed. The transient and DC behavior of the device have been examined. The power dissipation of the CMOS inverter has been computed and compared with the CMOS DMG-SOI JLT inverter. The power dissipation is found to be 5 times less for the proposed device as compared to the CMOS DMG-SOI JLT inverter. This exhibits an excellent improvement in power dissipation which is useful for making low-power future generation devices.

Similar content being viewed by others

Data Availability

The datasets generated and analyzed during the current study are not publicly available but may be available from the corresponding author on reasonable request.

Code Availability

The code used during this work is not available.

References

Goel A, Rewari S, Verma S, Gupta RS (2020)Novel dual-metalJunctionless nanotube field-effecttransistors for improved analog and low-noiseapplications. J Electron Mater 50:108–119. https://doi.org/10.1007/s11664-020-08541-9

Goel A, Rewari S, Verma S, Gupta RS (2019)Temperature-dependentgate-induced drain leakages assessment of dual-metalnanowire field-effecttransistor—analyticalmodel. IEEE Trans Electron Devices 66(5):2437–2445. https://doi.org/10.1109/TED.2019.2898444

Rewari S, Nath V, Haldar S, Deswal SS, Gupta RS (2018)Gate-induceddrain leakage reduction in the cylindrical dual-metalhetero-dielectric gate all around MOSFET. IEEE Trans Electron Devices 65(1):3–10. https://doi.org/10.1109/TED.2017.2771814

Sharma A, Jain A, Pratap Y, Gupta RS (2016)Effect of High-Kand vacuum dielectrics as gate stack on junctionless cylindrical surrounding gate MOSFET. Solid-StateElectron 123:26–32. https://doi.org/10.1016/j.sse.2016.05.016

Verma JHK, Haldar S, Gupta RS, Gupta M (2015)Modeling and simulation of subthreshold behaviour of cylindrical surrounding double gate MOSFET for enhanced electrostatic integrity. Superlattices Microstruct 88:354–364. https://doi.org/10.1016/j.spmi.2015.09.024

Sood H, Srivastava VM, Singh G (2016)Performance analysis of undoped and Gaussian doped cylindrical surrounding-gateMOSFET with its small-signalmodeling. Microelectron J 57:66–75. https://doi.org/10.1016/j.mejo.2016.10.001

Kaur H, Kabra S, Haldar S, Gupta RS (2007)An analytical drain current model for graded channel cylindrical/surroundinggate MOSFET. Microelectron J 38:352–359. https://doi.org/10.1016/j.mejo.2007.01.003

kumar NM, Syamal B, Sarkar CK (2010)Influence of channel and gate engineering on the analog and RF performance of DG MOSFETs. IEEE TransElectron Devices 57(4):820–826. https://doi.org/10.1109/TED.2010.2040662

Jena B, Dash S, Mishra GP (2016)Electrostatic performance improvement of dual material cylindrical gate MOSFET using work-functionmodulation technique. Superlattice Microstruct 97:212–220. https://doi.org/10.1016/j.spmi.2016.06.024

Long W (1999)Dual-materialgate (DMG)Field effect transistor. IEEE Trans Electron Devices 46(5):865–870. https://doi.org/10.1109/16.760391

Dhanaselvam PS, Balamurugan NB (2013)Performance analysis of fully depleted triple material surrounding gate SOI MOSFETs. J Comput Electronics 12(4):449–455. https://doi.org/10.1007/s10825-014-0554-3

Goel A, Rewari S, Verma S, Gupta RS (2020)Physics-basedanalytic modeling and simulation of gate-induceddrain leakage and linearity assessment in dual-metaljunctionless accumulation nanotube FET (DM-JAM-TFET). Appl Phys A 126:1–14. https://doi.org/10.1007/s00339-020-03520-7

Dhanaselvam PS, Balamurugan NB (20013)A 2D transconductance and sub-thresholdbehavior model for triple material surrounding gate MOSFETs. Microelectron J 44(12):1159–1164. https://doi.org/10.1016/j.mejo.2013.07.005

Kumar MJ, Chaudhary A (2004)Two-dimensionalanalytical modeling of fully depleted SHDMG SOI MOSFET and evidence for diminished SCEs. IEEE Trans on Electron Devices 51(4):569–574. https://doi.org/10.1109/TED.2004.823803

Orouji A (2008)Nanoscale Triple Material Double Gate (TM-DG)MOSFET for improving short channel effects. Int Conference Advances in Electronics and Micro-electronics

Goel K, Saxena M, Gupta M, Gupta RS (2006)Modeling and simulation of a nanoscale three-regiontri-material gate stack (TRIMGAS)MOSFET for improved carrier transport efficiency and reduced hot-electroneffects. IEEE Trans Electron Devices 53(7):1623–1633. https://doi.org/10.1109/TED.2006.876272

Tiwari PK, Dubey S, Singh M, Jit S (2010)A two–dimensionalanalytical model for threshold voltage of short-channeltriple-material double-gatemetal-oxide-semiconductorfiled-effecttransistors. J Appl Phys 108(7):1–8. https://doi.org/10.1063/1.3488605

Vanitha P, Balamurugan NB, Priya GL (2015)Triple Material Surrounding Gate (TMSG)Nanoscale Tunnel FET-analyticalmodeling and simulation. J Semi Tech Sci 15(6):585–593. https://doi.org/10.5573/JSTS.2015.15.6.585

Charles JP, Nirmal D, Prajoon P, Ajayan J (2016)Implementation of nanoscale circuits using dual metal gate engineered nanowire MOSFET with high-kdielectrics for low power application. Phys E 83:95–100. https://doi.org/10.1016/j.physe.2016.04.017

Nirmal D, Vijayakumar P, Thomas DM, Jebalin BK, Kumar NM (2013)Subthreshold performance of gate engineered FinFET devices and circuit with high-kdielectrics. Microelectron Reliab 53(3):499–504. https://doi.org/10.1016/j.microrel.2012.09.008

Goel A, Rewari S, Verma S, Gupta RS (2019)Shallow Extension Engineered Dual Material Surrounding Gate (SEE-DM-SG) MOSFET for improved gate leakages, analysis of circuit and noise performance. AEU -Int J Electron Commun 111:1–9. https://doi.org/10.1016/j.aeue.2019.152924

Cheng B, Cao M, Voorde PV, Greene W, Stork H, Yu Z, Woo JCS (1999)Design considerations of high-Kgate dielectrics for sub-0.1-µm MOSFET’s. IEEE Trans Electron Devices 46:261–262

Goel A, Rewari S, Verma S, Gupta RS (2019)High-Kspacer dual metal gate stack Underlap Junctionless gate all around (HKDMGS-JGAA)MOSFET for high frequency applications. Microsyst Technol 26:1697–1705. https://doi.org/10.1007/s00542-019-04715-6

Goel A, Rewari S, Verma S, Gupta RS (2021)Modeling of shallow extension engineered dual metal surrounding gate (SEE-DM-SG) MOSFET gate-induceddrain leakage (GIDL). Indian J Phys 95(2):299–308. https://doi.org/10.1007/s12648-020-01704-8

Nandi S, Srivastava S, Rewari S (2019)Dual metal Schottky barrier asymmetric gate stack cylindrical gate all around (DM-SB-ASMGS-CGAA) MOSFET for improved analog performance for high frequency application. Microsyst Technol. https://doi.org/10.1007/s00542-019-04577-y

Rewari S, Haldar S, Nath V, Deswal SS, Gupta RS (2016)Numerical modeling of the subthreshold region of junctionless double surrounding gate MOSFET (JLDSG). Superlattice Microstruct 90:8–19. https://doi.org/10.1016/j.spmi.2015.11.026

Rewari S (2020)Core-ShellNanowire Junctionless Accumulation Mode Field-EffectTransistor (CSN-JAM-FET) for High-FrequencyApplications -Analytical Study. Silicon. https://doi.org/10.1007/s12633-020-00744-3

Yin C, Chan PCH, Chan VWC (2003)Fabrication of raised S/D gate-all-aroundtransistor and gate misalignment analysis. IEEE Electron Device Lett 24(10):658–660. https://doi.org/10.1109/LED.2003.817367

Lin R, Lu Q, Ranade P, Liu TK, Hu C (2002)An adjustable work function technology using Mo gate for CMOS devices. IEEE Electron Device Lett 23(1):49–51. https://doi.org/10.1109/55.974809

Gupta N, Raghav AK, Gupta R, Sharma A (2020)Sub-thresholdmodeling of dual-halodual-dielectric triple-materialsurrounding-gate (DH-DD-TM-SG) MOSFET for Improved Leakages. J Eng Res 8(2):178–190

Ganesh A, Goel K, Mayall JS, Rewari S (2021)Subthreshold analytical model of asymmetric gate stack triple metal gate all around MOSFET (AGSTMGAAFET)for improved analog applications. Silicon. https://doi.org/10.1007/s12633-021-01173-6

Goel E, Kumar S, Singh K, Singh B, Kumar M, Jit S (2016)2-Danalytical modeling of threshold voltage for graded-channeldual-material double-gateMOSFETs. IEEE Trans Electron Devices 63:966–973. https://doi.org/10.1109/TED.2016.2520096

(2020) ATLAS: 3D device simulator, SILVACO International

Goel A, Rewari S, Verma S, Deswal SS, Gupta RS (2021)Dielectric Modulated Junctionless Biotube FET (DM-JL-BT-FET) Bio-Sensor. IEEE Sens J 21(15):16731–16743. https://doi.org/10.1109/JSEN.2021.3077540

Mahmud MA, Subrina S (2016)Two-dimensionalanalytical model of threshold voltage and drain current of a double-halogate stacked triple-materialdouble-gate MOSFET. J Comput Electron 15(2):525–536. https://doi.org/10.1007/s10825-016-0820-7

Yadav R, Ahuja K, Rathee DS (2021)Performance enhancement of GAA multi-gatenanowire with asymmetric hetero-dielectricoxide. Silicon. https://doi.org/10.1007/s12633-021-00964-1

Wagaj SC, Patil SC (2019)Dual material gate silicon on insulator junctionless MOSFET for low power mixed signal circuits. Int J Electron 106:992–1007. https://doi.org/10.1080/00207217.2019.1570564

Author information

Authors and Affiliations

Contributions

The idea of the research was conceptualized by Prashant Kumar and Munish Vashisht carried out the analytical modeling and simulation of junctionless MOSFET. The formal analysis and resources for the research were arranged by Neeraj Gupta and Rashmi Gupta. Prashant Kumar also prepared the original draft of the paper and Neeraj Gupta did the review, proofreading and necessary editing in the article.

Corresponding author

Ethics declarations

Conflicts of Interest/Competing Interests

The authors declare that there is no conflict of interest regarding the content of this article.

Ethics Approval

Not applicable.

Consent to Participate

All authors are agreed.

Consent for Publication

There are no details on an individual reported in the manuscript.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kumar, P., Vashisht, M., Gupta, N. et al. Subthreshold Current Modeling of Stacked Dielectric Triple Material Cylindrical Gate All Around (SD-TM-CGAA) Junctionless MOSFET for Low Power Applications. Silicon 14, 6261–6269 (2022). https://doi.org/10.1007/s12633-021-01399-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01399-4