Abstract

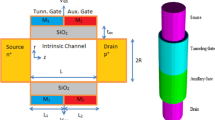

A two-dimensional analytical model is proposed in this paper for surface potential and drain current on Triple Material Surrounding Gate Junctionless Tunnel Field Effect Transistor (TFET). The purpose of this theoretical analysis is to break down two 1D equations of the 2D Poisson Equations. In this model, Triple Material Gates are decomposed into three different individual gates with different work functions. The Finite Differentiation Method is being enforced for this reason. By applying sufficient boundary constraints, the decomposed individual 1D Poisson equations are combined. In essence, this decreases the difficulty of solving Poisson equations in 2D. The analytical model proposed makes expressions of surface potential and drain current simpler. The reduction in the subthreshold swing which makes the device useful for low power applications. Finally, the outcomes of the study are correlated with the TCAD simulation. The proposed model is therefore validated to explain the nature of the Triple Material Surrounding Gate Junctionless TFETs.

Similar content being viewed by others

Data Availability

Data is available as Tables and Figures in appropriate places in the manuscript

References

Muller RS, Kamins TI, Chan M (2003) Device electronics for integrated circuits. Wiley, New York, pp 443–445

Ionescu AM, Riel H (2011) Tunnel field-effect transistors as energyefficient electronic switches. Nature 479:329–337

Toh E-H et al (2008) Device physics and design of germanium tunneling field-effect transistor with source and drain engineering for low power and high-performance applications. J Appl Phys 103(10):104504

ArunSamuel TS, Balamurugan NB (2014) Analytical surface potential model with TCAD simulation verification for evaluation of surrounding gate TFET. J Electr Eng Technol 9(2):655–661

SuveethaDhanaselvam P, Balamurugan NB, Vivek Chakaravarthi GC, Ramesh RP, Sathish Kumar BR (2014) A 2D analytical modeling of single halo triple material surrounding gate (SHTMSG) MOSFET. J Electr Eng Technol 9(4)

Priya GL, Balamurugan NB (2020) Improvement of subthreshold characteristics of dopingless tunnel FET using hetero gate dielectric material: analytical modeling and simulation. Silicon 12:2189–2201

Bhuwalka KK, Schulze J, Eisele I (2005) Scaling the vertical tunnel FET with tunnel band gap modulation and gate work function engineering. IEEE Trans Electron Dev 52(5):909–917

Zhang Q, Shao W, Seabaugh A (2006) Low subthreshold swing tunnel transistors. IEEE Trans Electron Devices 27(4):297–300

Choi WY, Park BG, Lee JD, King Liu TJ (2007) Tunneling Field effect transistors (TFETs) with subthreshold swing (SS) less than 60mV/dec. IEEE Trans Electron Devices 28(8):743–745

Colinge JP, Lee CW, Afzalian A, Akhavan ND, Yan R, Ferain I, Razavi P, O'Neill B, Blake A, White M, Kelleher AM, McCarthy B, Murphy R (2010) Nanowire transistors without junctions. Nat Nanotech 5(3):225

Ghosh B, Bal P, Mondal P (2013) A junctionless tunnel field effect transistor with low subthreshold. J Comput Electron 12(3):428

Venkatesh M, Balamurugan NB (2020) Influence of threshold voltage performance analysis on dual halo gate stacked triple material dual gate TFET for ultra low power applications. Silicon

Arun Samuel TS, Balamurugan NB, Bhuvaneswari S, Sharmila D Padmapriya K (2014) Analytical modelling and simulation of single-gate SOI TFET for low-power applications. Int J Electron 101(6)

Lakshmi Priya G, Balamurugan NB, Saraswathi D (2015) Impact of electric field distribution on the performance of dual material gate work function engineered surrounding gate nanowire tunnel FET. Int J Appl Eng Res 10(1):1018–1023

Arun Samuel TS, Balamurugan NB (2013) An analytical modeling and simulation of dual material double gate tunnel field effect transistor for low power applications. J Electr Eng Technol 8(6)

Manikandan S, Balamurugan NB, Nirmal D (2020) Analytical model of double gate stacked oxide junctionless transistor considering source/drain depletion effects for CMOS low power applications. Silicon 12:2053–2063

Venkatesh M, Balamurugan NB (2019) New subthreshold performance analysis of germanium based dual halo gate stacked triple material surrounding gate tunnel field effect transistor. Superlattices and Microstructures 130:485–498, ISSN 0749–6036

Vanitha P, Balamurugan NB, Priya GL (2015) Triple material surrounding gate (TMSG) nanoscale tunnel FET-analytical modeling and simulation. J Semicond Technol Sci 15(6):585–593

Preethi S, Balamurugan NB (2020) Analytical modeling of surrounding gate Junctionless MOSFET using finite differentiation method. Silicon:1–11

Samuel TSA, Balamurugan NB (2014) Analytical modeling and simulation of germanium single gate silicon on insulator TFET. J Semicond 35, Number 3,Citation:034002

Gola D, Singh B, Singh J, Jit S, Tiwari PK (2019) Static and quasi-static drain current modeling of tri-gate junctionless transistor with substrate bias induced effects. IEEE Trans Electron Devices 66(7):2876–2883

Singh D, Gola K, Singh E, Goel SK, Jit S (2017) Two-dimensional analytical threshold voltage model for dielectric pocket double-gate junctionless FETs by considering source/drain depletion effect. IEEE Trans Electron Devices 64(3):901–908

Verhulst AS, Sorée B, Leonelli D, Vandenberghe WG, Groeseneken G (2010) Modeling the single-gate, double-gate, and gate-all around tunnel field-effect transistor. J Appl Phys 107(2):024518

Luisier M, Klimeck G (2010) Simulation of nanowire tunneling transistors: from the Wentzel–Kramers–Brillouin approximation to full-band phonon-assisted tunneling. J Appl Phys 107(8):084507

Venkatesh M, Balamurugan NB (2021) Influence of threshold voltage performance analysis on dual halo gate stacked triple material dual gate TFET for ultra low power applications. Silicon 13(1):275–287

Acknowledgments

The authors are grateful to the Management of “Thiagarajar college of Engineering”, Madurai for the support extended to carry out this research work.

Funding

We did not receive funding support from any organization for the submitted work and we certify that they have no affiliations with or involvement in any organization or entity with any financial interest or non-financial interest in the subject matter or materials discussed in this manuscript.

Author information

Authors and Affiliations

Contributions

All authors read and approved the final manuscript.

Corresponding author

Ethics declarations

Ethics Approval and Consent to Participate

Yes.

Consent for Publication

Yes.

Competing Interests

There is no conflict of interest in this work (file attached).

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Suguna, M., Kaveri, R., Sree, V.A.N. et al. Modeling and Simulation Based Investigation of Triple Material Surrounding Gate Tunnel FET for Low Power Application. Silicon 14, 2363–2371 (2022). https://doi.org/10.1007/s12633-021-01368-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01368-x