Abstract

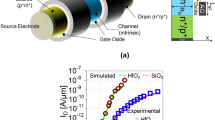

In this paper, we propose a novel “Teeth Junctionless Gate All Around Field Effect Transistor” (TH-JLGAA FET) based on gate engineering method, to obtain finer electrical characteristics. A 3 nm TH-JLGAA FET is designed and was scaled up to 14 nm to observe the effect of scaling on device performance. The characteristics are revealed and compared with contemporary JLGAA FETs. The results show that the novel TH-JLGAA FET appears to have finer Sub-thresholdSlope (SS), Drain Induced Barrier Lowering (DIBL), transconductance (gm), Ion/Ioff current ratio and threshold voltage roll-off. Moreover, these remarkable characteristics can be controlled by engineering the structure and volume of the gate. In addition, the sensitivities of the novel TH-JLGAA FET device with respect to structural parameters are probed.

Similar content being viewed by others

Data Availability

No supplementary materials.

References

Sahay S, Kumar MJ (2017) Nanotube junctionlessfet: Proposal, design, and investigation. IEEE Trans Electron Devices 64(4):1851–1856

Sallese J-M, Jazaeri F, Barbut L, Chevillon N, Lallement C (2013) A common core model for junctionless nanowires and symmetric double-gate fets. IEEE Trans Electron Devices 60(12):4277–4280

Hur J, Moon D-I, Choi J-M, Seol M-L, Jeong U-S, Jeon C-H, Choi Y-K (2015) A core compact model for multiple-gate junctionlessfets. IEEE Trans Electron Devices 62(7):2285–2291

Shih C-H, Liang J-T, Wang J-S, Chien ND (2011) A source-side injection lucky electron model for schottky barrier metal–oxide– semiconductor devices. IEEE Electron Device Lett 32(10):1331–1333

Colinge J, Lee C, Afzalian A (2009) In: Dehdashti N, Yan R, Ferain I, Razavi P, OÐŞNeill B, BlaNe A, White N, Kelleher AM, McCarthy B, Murphy R. ISOI Gated resistor: CMOS without Junctions, SOI Conference, p 1Y2

Zhang L, Chan M, He F (2010) The impact of device parameter variation on double gate tunnelingfet and double gate mosfet. In: 2010 IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC), IEEE, Piscataway, pp 1–4

Taur Y, Liang X, Wang W, Lu H (2004) A continuous, analytic draincurrent model for dg mosfets. IEEE Electron Device Lett 25(2):107–109

Santa Clara CA (2014) Atlas device simulation software. Santa Clara, CA, USA

Manual, Atlas User’S (2016) Silvaco, Santa Clara, CA, USA

Lin Y-S, Puthenkovilakam R, Chang J (2002) Dielectric property and thermal stability of hfo 2 on silicon. Appl Phys Lett 81(11):2041–2043

Hossain NM, Quader S, Siddik AB, Chowdhury MIB (2017) Tcad based performance analysis of junctionless cylindrical double gate all around fet up to 5 nm technology node. In: 2017 20th International Conference of Computer and Information Technology (ICCIT), IEEE, Piscataway, pp 1–4

Tsai M-J, Peng K-H, Sun C-J, Yan S-C, Hsu C-C, Lin Y-R, Lin Y-H, Wu Y-C (2019) Fabrication and characterization of stacked poly-si nanosheet with gate-all-around and multi-gate junctionless field effect transistors. IEEE J Electron Devices Soc 7:1133–1139

Lu Y-H, Kuo P-Y, Wu Y-H, Chen Y-H, Chao T-S (2011) Novel gaa raised source/drain sub-10-nm poly-sinw channel tfts with selfaligned corked gate structure for 3-d ic applications. In: 2011 Symposium on VLSI Technology-Digest of Technical Papers. IEEE, Piscataway, pp 142–143

Sacchetto D, Ben-Jamaa MH, DeMicheli G, UsufLeblebici Y (2009) Fabrication and characterization of vertically stacked gate-all-around si nanowire fet arrays. In: 2009 Proceedings of the European Solid State Device Research Conference, IEEE, pp 245–248

Razavi B (2002) Design of analog CMOS integrated circuits, Tata McGrawHill Education, New York

Acknowledgements

The authors would like to acknowledge Indian Institute of Technology Hyderabad (IIT Hyderabad) for backing us with the tools (Silvaco ATLAS) required for simulating this work. And M. Durga Prakash thankfully acknowledges this publication as an outcome of the R&D work undertaken project under the Start-up Research Grant "(SRG; File No.: SRG/2019/002236) Scheme of Department of Science and Technology (DST), Government of India, being Science Engineering Research Broad (SERB).

Author information

Authors and Affiliations

Contributions

M. Durga Prakash, Caleb Meriga and Ravi Teja Ponnuri: Conceptualization; M. Durga Prakash Caleb Meriga and Ravi Teja Ponnuri: investigation; M. Durga Prakash Caleb Meriga, Ravi Teja Ponnuri and B V V Satyanarayana: resources;Caleb Meriga and Ravi Teja Ponnuri, B. V. V Satyanarayana, A Arun Kumar Gudivada and Asisa KumarPanigrahy: data curation; M. Durga Prakash, Caleb Meriga and Ravi Teja Ponnuri: writing—original draft preparation; M. Durga Prakash, Caleb Meriga and Ravi Teja Ponnuri: writing—review and editing; M. Durga Prakash, Caleb Meriga,Ravi Teja Ponnuri andB. V. V Satyanarayana: visualization; M. Durga Prakash: supervision;

Corresponding author

Ethics declarations

This article does not contain any studies with human or animal subjects.

Conflict of Interest

The authors declare that they have no conflict of interest.

Consent to Participate

Additional informed consent was obtained from M. Durga Prakash identifyinginformation is included in this article.

Consent for Publication

Author(s):Dr. M. Durga Prakash.

Author’s signature: M. D. Prakash (  ).

).

Date: 07-12-2020.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Meriga, C., Ponnuri, R.T., Satyanarayana, B.V.V. et al. A Novel Teeth Junction Less Gate All Around FET for Improving Electrical Characteristics. Silicon 14, 1979–1984 (2022). https://doi.org/10.1007/s12633-021-00983-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-00983-y