Abstract

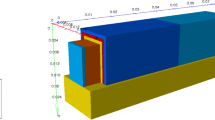

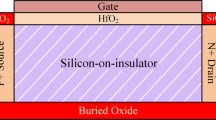

In this work, a tunneling field-effect transistor (TFET) in the structure that can maximize the electrostatic effects in determining its electrical performances is optimally designed and characterized. The featured device structure includes gate-all-around (GAA) channel and dual gates (DuGs) identified as control gate (CG) and adjust gate (AG), respectively. Not along with the design tasks, more fundamental studies on the effects of respective gates on device performances are sought. It has been found that the relatively different vicinities of the DuGs to source and drain junctions have differentiable dominances in controlling the primary direct-current (DC) parameters of the TFET including threshold voltage (Vth), on-state current (Ion), subthreshold swing (S), and on/off current ratio (Ion/Ioff). For the systematic study, four different cases have been presumably schemed giving the degree of freedom in gate workfunctions and inter-gate connectivity. It has been found that the CG at the source side more effectively modulates Vth, Ioff, and S, while the AG at the drain side shows the higher controllability over Ion and Ion/Ioff of the TFET. An optimally designed GAA DuG demonstrated Ion/Ioff > 1011 along with a small S of 14.6 mV/dec, which supports the strong potential of the GAA DuG TFET in the low-power applications.

Similar content being viewed by others

References

C. Jia, Z. Lin, Y. Huang, X. Duan, Chem. Rev. 119, 9074 (2019)

A.C. Seabaugh, Q. Zhang, Proc. IEEE 98, 2095 (2010)

International Roadmap for Devices and Systems (IRDSTM) 2018 Edition.https://irds.ieee.org/editions/2018. Accessed 15 July 2019

J.-T. Park, J.-P. Colinge, IEEE Trans. Electron. Devices 49, 2222 (2002)

S. Go, W.J. Lee, S. Cho, J. Semicond. Technol. Sci. 19, 551 (2019)

K. Boucart, A.M. Ionescu, IEEE Trans. Electron. Devices 54, 1725 (2007)

E. Ko, J.W. Lee, C. Shin, IEEE Electron. Device Lett. 38, 418 (2017)

S. Kim, G. Myeong, W. Shin, H. Lim, B. Kim, T. Jin, S. Chang, K. Watanabe, T. Taniguchi, S. Cho, Nat. Nanotechnol. 15, 203 (2020)

S. Cho, I.M. Kang, K.R. Kim, B.-G. Park, J.S. Harris, Appl. Phys. Lett. 103, 222102 (2013)

W.G. Vandenberghe, A.S. Verhulst, B. Sorée, W. Magnus, G. Groeseneken, Q. Smets, M. Heyns, M.V. Fischetti, Appl. Phys. Lett. 102, 013510 (2013)

S. Cristoloveanu, J. Wan, A. Zaslavsky, IEEE J. Electron. Devices Soc. 4, 215 (2016)

W.Y. Choi, B.-G. Park, J.D. Lee, T.-J.K. Liu, IEEE Electron. Device Lett. 28, 743 (2007)

W. Cao, D. Sarkar, Y. Khatami, J. Kang, K. Banerjee, AIP Adv. 4, 067141 (2014)

R. Jhaveri, V. Nagavarapu, J.C.S. Woo, IEEE Trans. Electron. Devices 58, 80 (2011)

A.S. Verhulst, W.G. Vandenberghe, K. Maex, S. De Gendt, M.M. Heyns, G. Groeseneken, IEEE Electron. Device Lett. 29, 1398 (2008)

W.Y. Choi, W. Lee, IEEE Trans. Electron. Devices 57, 2317 (2010)

J.H. Seo, Y.J. Yoon, S. Lee, J.H. Lee, S. Cho, I.M. Kang, Curr. Appl. Phys. 15, 208 (2015)

Y. Jeon, M. Kim, D. Lim, S. Kim, Nano Lett. 15, 4905 (2015)

W.C. Chen, H.T. Lue, Y.H. Hsiao, C.Y. Lu, IEEE Trans. Electron. Devices 64, 1336 (2017)

N. Navlakha, J.-T. Lin, A. Kranti, IEEE Electron Device Lett. 37, 1127 (2016)

J. S. Park, U.S. Patent No. 6168998, (2001).

Atlas User’s Manual, Device Simulation Software (Silvaco Inc, Santa Clara, 2018)

W. Shockley, W.T. Read, Phys. Rev. 87, 835 (1952)

J. Dziewior, W. Schmid, Appl. Phys. Lett. 31, 346 (1977)

A. Wettstein, A. Schenk, W. Fichtner, IEEE Trans. Electron. Devices 48, 279 (2001)

A. Schenk, J. Appl. Phys. 84, 3684 (1998)

C. Lombardi, S. Manzini, A. Saporito, M. Vanzi, IEEE Trans. Comput. Des. Integr. Circ. Syst. 7, 1164 (1988)

J. Wan, C. Le Royer, A. Zaslavsky, S. Cristoloveanu, Solid State Electron. 65–66, 226 (2011)

L. De Michielis, N. Dağtekin, A. Biswas, L. Lattanzio, L. Selmi, M. Luisier, H. Riel, A.M. Ionescu, Appl. Phys. Lett. 103, 123509 (2013)

A. Shaker, A. Maged, A. Elshorbagy, A. Abouelainain, M. Elsabbagh, Semicond. Sci. Technol. 35, 025007 (2020)

K. Han, S. Long, Z. Deng, Y. Zhang, J. Li, Micromachines 11, 164 (2020)

A.K. Gupta, A. Raman, N. Kumar, IEEE Trans. Electron. Devices 66, 3506 (2019)

K.E. Moselund, M.T. Björk, H. Schmid, H. Ghoneim, S. Karg, E. Lörtscher, W. Riess, H. Riel, IEEE Trans. Electron. Devices 58, 2911 (2011)

J. Madan, R.S. Gupta, R. Chaujar, Jpn. J. Appl. Phys. 54, 094202 (2015)

R. Gandhi, Z. Chen, N. Singh, K. Banerjee, S. Lee, IEEE Electron. Device Lett. 32, 1504 (2011)

J.S. Yoon, K. Kim, C.K. Baek, Sci. Rep. 7, 1 (2017)

Y.R. Jhan, Y.C. Wu, M.F. Hung, IEEE Electron. Device Lett. 34, 1482 (2013)

H.M. Fahad, M.M. Hussain, IEEE Trans. Electron. Devices 60, 1034 (2013)

N. Navlakha, A. Kranti, J. Appl. Phys. 122, 044502 (2017)

B. Jafari Touchaee, N. Manavizadeh, IEEE Trans. Electron Devices 62, 3147 (2015)

Funding

This work was supported by Brain Korea (BK) 21 Program in Seoul National University and also supported by the Gachon University Research Fund (GCU-2019-0324). The simulation task was supported by IDEC Program.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors have no conflicts of interest to declare that are relevant to the content of this article.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Ansari, M.H.R., Cho, S. & Park, BG. More physical understanding of current characteristics of tunneling field-effect transistor leveraged by gate positions and properties through dual-gate and gate-all-around structuring. Appl. Phys. A 126, 839 (2020). https://doi.org/10.1007/s00339-020-04015-1

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-020-04015-1