Abstract

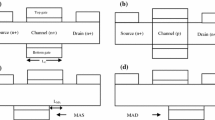

The paper presents the investigation of linearity distortion analysis of double gate junctionless transistor with high-k gate dielectrics and gate metals. As double gate junctionless transistors have shown high performance in digital circuits, linearity analysis is carried out to understand nonlinear behavior of the device for RFIC applications. In order to ensure minimum intermodulation and higher order harmonics at the system output, different linearity parameters like Second Order Voltage Intercept Point, Third Order distortion, Third Order Input Intercept Point and Third Order Intermodulation Distortion are evaluated. The results show that junctionless transistor should be biased at appropriate low voltage to ensure better linearity which is desired for RFICs. The effects of high-k gate dielectrics and gate metals on linearity characteristics of junctionless transistor are also investigated. Deterioration of the linearity is observed in junctionless transistor for the use of high-k insulators as gate dielectrics. It is also observed that low work function gate material is suitable to achieve higher linearity in low power applications.

Similar content being viewed by others

References

Frank DJ, Dennard RH, Nowak E, Solomon PM, Taur Y, Wong H-SP (Mar. 2001) Device scaling limits of Si MOSFETs and their application dependencies. Proc IEEE 89(3):259–288

M. Masahara, R. Surdeanu, L. Witters, G. Doornbos, V.H. Nguyen, G. Van den bosch, C. Vrancken, K. Devriendt, F. Neuilly, E. Kunnen, E. Suzuki, M. Jurczak, S. Biesmans, “Independent double-gate FinFETs with asymmetric gate stacks,” Microelectronic Engineering, 84–9/10, pp. 2097, 2007

A. Nitayama, H. Takato, N. Okabe, K. Sunouchi, K. Hieda, F. Horiguchi, F. Masuoka, “Multi-pillar surrounding gate transistor (M-SGT) for compact and high-speed circuits,” IEEE Transactions on Electron Devices, 38–3, pp. 579,1991

Singh N, Agarwal A, Bera LK, Liow TY, Yang R, Rustagi SC, Tung CH, Kumar R, Lo GQ, Balasubramanian N, Kwong DL (2006) High performance fully depleted silicon nanowire (diameter<5 nm) gate-allaroundCMOS devices. IEEE Electron Device Letters 27-5:383

Bhuwalka KK, Schulze J, Eisle I (2005) Scaling the vertical tunnel FET with tunnel band gap modulation and gate work function engineering. IEEE Trans Electron Devices 52(5):909–917

C.-W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, and J.-P. Colinge, “Junctionless multigate field-effect transistors,” Applied Physics Letter, vol. 94, no. 5, p. 053 511, Feb. 2009

Kranti A, Yan R, Lee CW et al (2010) Junctionless transistor (JNT): properties and design guidelines. IEEE Explore:357–360

Colinge, J. P., Lee, C. W., Akhavan, N. D., et al., “Junctionless Transistors: Physics and Properties,” Semiconductor-On-Insulator Materials for Nanoelectronics Applications, Engineering Materials, ISBN 978–3–642-15868-1 Springer-verlag, pp. 187–199, 2011

Colinge JP et al (2009) SOI gated register: CMOS without junction. SOI Conference, IEEE international, Foster city CA:1–2

W. Vitale, et al., “Monte Carlo Study Transport Properties in Junctionless transistor,” Computational Electronic (IWCE), pp. 1–3. Pisa, 2010

Lee CW, Borne A, Ferain I, Afzalian A, Yan R, Dehdashti Akhavan N, Razavi P, Colinge JP (Mar. 2010) High-temperature performance of silicon junctionless MOSFETs. IEEE Trans. Electron Devices 57(3):620–625

Bartsch ST, Arp M, Ionescu AM (March 2014) Junctionless silicon nanowire resonator. IEEE Journal of the Electron Devices Society 2(2):8–15

Singh P, Miao J, Pott V, Park W-T, Kwong D-L (December 2012) Piezoresistive sensing performance of Junctionless nanowire FET. IEEE Electron Device Letters 33(12):1759–1761

Jong Kyung Park, Seung-Yoon Kim, Ki-Hong Lee, Seung Ho Pyi, Seok-Hee Lee1 and Byung Jin Cho, “Surface-controlled ultrathin (2 nm) poly-Si Channel Junctionless FET towards 3D NAND flash memory applications,” Symposium on VLSI Technology Digest of Technical Papers, 2014

Choi S-J, Moon D-I, Kim S, Ahn J-H, Lee J-S, Kim J-Y, Choi Y-K (May 2011) Nonvolatile memory by all-around-gate Junctionless transistor composed of silicon nanowire on bulk substrate. IEEE Electron Device Letters 32(5):602–604

C. W. Lee, R. Yan, I. Ferain, A. Kranti, N. D. Akhavan, P. Razavi, R. Yu and J. P. Colinge, “Nanowire Zero-Capacitor DRAM Transistors with and without Junctions,” Proc. 10th IEEE Int. Conf. Nanotechnology, pp 242–245, August 2010

Elizabeth Buitrago, Giorgos Fagas, Montserrat Fernández-Bola˜nos Badia, Yordan M. Georgiev, Matthieu Berthomé and Adrian Mihai Ionescu, “Junctionless silicon nanowire transistors for the tunable operation of a highly sensitive, low power sensor,” Sensors Actuators B Chem, vol. 183, pp. 1–10, April, 2013

Pritish Narayanan, Pavan Panchapakeshan, Jorge Kina, Chi On Chui and Csaba Andras Moritz, “Integrated Nanosystems with Junctionless Crossed Nanowire Transistors,” Proc. 11th IEEE Conf. Nanotechnology, 2011

Wang J, Gang D, Wei K, Zhao K, Zeng L, Zhang X, Liu X (March 2014) Mixed-mode analysis of different mode silicon nanowire transistors-based inverter. IEEE Trans Nanotechnol 13(2):362–367

Baidya A, Krishnan V, Baishya S, Lenka TR (2015) Effect of thin gate dielectrics and gate materials on simulated device characteristics of 3D double gate JNT. Superlattice Microst 77:209–218

Ghosh P, Haldar S, Gupta RS, Gupta M (Dec. 2012) An investigation of linearity performance and intermodulation distortion of GME CGT MOSFET for RFIC designs. IEEE Trans Electron Dev 59(12):3263–3268

Woerlee PH, Knitel MJ, Langevelde RV, Klaassen DBM, Tiemeijer LF, Scholten AJ, Zegers-van Duijnhoven ATA (2001) RF-CMOS performance trends. IEEE Trans. Electron Devices 48(8):1776–1782

B. Murmann, P. Nikaeen, D. J. Connelly, R. W. Dutton., “Impact of scaling on analog performance and associated modeling needs,” IEEE Trans Electron Devices, vol.53, pp.2160–2167, 2006, Impact of Scaling on Analog Performance and Associated Modeling Needs

Pratap Y, Subhasis H, Gupta RS, Gupta M (March 2014) Performance evaluation and reliability issues of Junctionless CSG MOSFET for RFIC design. IEEE Trans Device Mater Reliab 14(1):418–425

L. F. Tiemeijer, R. van langevelde, O. Gaillard, R. J. Havens, P. G. M. Baltus, P. H. Woerlee, and D. B. M. Klaassen, “ RF Distortion Characterisation of Sub-Micron CMOS,” Proc. ESSDERC, pp. 464, 2000

Paliwoda P, Misra D (2011) Impact of constant voltage stress on high-κ gate dielectric for RF IC performance. ECS Trans 41(3):415–419

Abe Y, Miyata N, Shiraki Y, Yasuda T (2007) Dipole formation at direct-contact HfO2/Si interface. Applied Physics Letter 90:172906

Tzeng SD, Gwo S (2006) Charge trapping properties at silicon nitride/silicon oxide interface studied by variable-temperature electrostatic force microscopy. J Appl Phys 100:023711

R. Trevisoli, R. T. Doria, M. Souza, and M A Pavanello, “Analysis of the leakage current in junctionless nanowire transistors”, Applied Physics Letters, Vol:103, pp. 202103, 2013; https://doi.org/10.1063/1.4829465

Acknowledgments

The authors acknowledge TEQIP-III for facilitating Synopsys TCAD Tool in VLSI Lab, Department of Electronics and Communication Engineering of National Institute of Technology Silchar, India to carry out the research work.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Baidya, A., Lenka, T.R. & Baishya, S. Linear Distortion Analysis of 3D Double Gate Junctionless Transistor with High-K Dielectrics and Gate Metals. Silicon 13, 3113–3120 (2021). https://doi.org/10.1007/s12633-020-00669-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-020-00669-x