Abstract

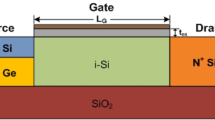

In this paper, we examine the impact of variation in the lateral straggle parameter on linearity and reliability performance for the Hetero-stacked TFET. By incorporating hetero-stack in the Source, both the subthreshold as well as the drain current can be improved. Although the tunnel field effect transistor is considered a valid candidate to replace the MOSFET for low power applications, the device performance depends on the precision in the fabrication process. During fabrication process, ion implantation technique is used to realize the variation in the tilt angle. This variation causes an extension of dopants from the regions of source and drain to the channel, which significantly affects the performance of the device. The linearity and reliability performances of the Hetero-stacked TFET (HS-TFET) are analyzed by varying the lateral straggle parameter (σ) from 0 to 8 nm. A higher value of the lateral straggling parameter causes an increase in the on current due to the enhanced electron tunneling rate. However, linearity performance tends to deteriorate as the lateral straggle parameter increases. The linearity and reliability of the device are studied in terms of transconductances of higher order (gm2 and gm3), VIP2, VIP3, IIP3, IMD3 and 1-dB compression point.

Similar content being viewed by others

References

Zhang Q, Zhao W, Seabaugh A (2006) Low-subthreshold-swing tunnel transistors. IEEE Electron Device Lett 27:297–300

Choi WY, Park BG, Lee JD, Liu TJK (2007) Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett 28:743–745

Appenzeller J, Radosavljević M, Knoch J, Avouris P (2004) Tunneling versus thermionic emission in one-dimensional semiconductors. Phys Rev Lett 92

Chander S, Bhowmick B, Baishya S (2015) Heterojunction fully depleted SOI-TFET with oxide/source overlap. Superlattice Microst 86:43–50

Fan ML, Hu VPH, Chen YN, Hsu CW, Su P, Chuang CT (2015) Investigation of Backgate-biasing effect for ultrathin-body III-V heterojunction tunnel FET. IEEE Trans Electron Devices 62:107–113

Goswami R, Bhowmick B (2017) An analytical model of drain current in a nanoscale circular gate TFET. IEEE Trans Electron Devices 64:45–51

Pal A, Dutta AK (2016) Analytical drain current modeling of double-gate tunnel field-effect transistors. IEEE Trans Electron Devices 63:3213–3221

Beneventi GB, Gnani E, Gnudi A, Reggiani S, Baccarani G (2014) Dual-metal-gate InAs tunnel FET with enhanced turn-on steepness and high on-current. IEEE Trans Electron Devices 61:776–784

Fan M, Hu VP, Chen Y, Hsu C, Su P, Chuang C (2015) Investigation of Back gate-biasing effect for ultrathin-body III-V heterojunction tunnel FET. IEEE Trans Electron Devices 62:107–113

Kao KH, Verhulst AS, Vandenberghe WG, Soree B, Magnus W, Leonelli D, Groeseneken G, Meyer KD (2012) Optimization of gate-on-source-only tunnel FETs with counter-doped pockets. IEEE Trans Electron Devices 59:2070–2077

Wu C, Huang Q, Zhao Y, Wang J, Wang Y, Huang R (2016) A novel tunnel FET design with stacked source configuration for average subthreshold swing reduction. IEEE Trans Electron Devices 63:5072–5076

Seabaugh AC, Zhang Q (2010) Low-voltage tunnel transistors for beyond CMOS logic. Proc IEEE 98:2095–2110

Dennard RH, Gaensslen FH, Yu HN, Rideout VL, Bassous E, Leblanc AR (1999) Design of ion-implanted MOSFET's with very small physical dimensions. Proc IEEE 87:668–678

Suzuki K, Sudo R, Nagase M (2001) Estimating lateral straggling of impurity profiles of ions implanted into crystalline silicon. IEEE Trans Electron Devices 48:2803–2807

Ghosh S, Koley K, Sarkar CK (2015) Impact of the lateral straggle on the analog and RF performance of TFET. Microelectron Reliab 55:326–331

Vanlalawmpuia K, Saha R, Bhowmick B (2018) Performance Evaluation of Heterostacked TFET for variation in lateral straggle and its application as digital inverter. Appl Phys A 24

Saha R, Vanlalawmpuia K, Bhowmick B, Baishya S (2019) Deep insight into DC, RF/analog, and digital inverter performance due to variation in straggle parameter for gate modulated TFET. Mater Sci Semicond Process 91:102–107

TCAD Sentaurus Device User’s Manual, (2013) Synopsys, Inc. Mountain View, CA, USA

Biswas A, Dan SS, Royer CL, Grabinski W, Ionescu AM (2012) TCAD simulation of SOI TFETs and calibration of non-local band-to-band tunneling model. Microelectron Eng 98:334–337

Hoyniak D, Nowak E, Anderson RL (2000) Channel electron mobility dependence on lateral electric field in field-effect transistors. J Appl Phys 87:876–881

Ghosh S, Koley K, Sarkar CK (2018) Deep insight into linearity and NQS parameters of tunnel FET with emphasis on lateral straggle. Micro & Nano Letters 13:35–40

Kumar A (2017) Effect of trench depth and gate length shrinking assessment on the analog and linearity performance of TGRC-MOSFET. Superlattice Microst 109:626–640

Nigam K, Pandey S, Kondekar PN, Sharma D, Parte PK (2017) A barrier controlled charge plasma-based TFET with gate engineering for Ambipolar suppression and RF/linearity performance improvement. IEEE Trans Electron Devices 64:2751–2757

Niu G, Liang Q, Cressler JD, Webster CS, Harame DL (2001) RF linearity characteristics of SiGe HBTs. IEEE Trans Microwave Theory Tech 49:1558–1565

Kumar SP, Agrawal A, Chaujar R, Gupta RS, Gupta M (2011) Device linearity and intermodulation distortion comparison of dual material gate and conventional AlGaN/GaN high electron mobility transistor. Microelectron Reliab 51:587–596

Kang S, Choi B, Kim B (2003) Linearity analysis of CMOS for RF application. IEEE Trans Microwave Theory Tech 51:972–977

Razavi B (1998) RF microelectronics. Prentice Hall, UCLA, Los Angeles

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Vanlalawmpuia, K., Bhowmick, B. Linearity Performance Analysis Due to Lateral Straggle Variation in Hetero-Stacked TFET. Silicon 12, 955–961 (2020). https://doi.org/10.1007/s12633-019-00189-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-019-00189-3