Abstract

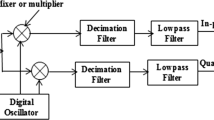

This brief presents an efficient binary common subexpression elimination (BCSE)-based approach for designing reconfigurable interpolation root-raised cosine (RRC) finite-impulse-response (FIR) filter, whose coefficients change during runtime for multistandard wireless communication system called software-defined radio (SDR). Reconfiguration can be done conveniently by storing the coded coefficients in the lookup tables (LUTs), and loading the required coefficient set over the interpolation filter. In the proposed method based on 4-bit BCSE algorithm, first the number of binary common subexpressions (BCSs) formed in the coefficients is reduced. Hence, multiplexers, shifters, and adders in the multiplier structure are reduced, which results in the improvement of operating frequency. The number of addition operations is further reduced using programmable adders and an efficient polyphase interpolation structure is implemented to reduce the hardware cost. The proposed design has 49.5% less area-delay product and 28.6% improved frequency of operation when compared to a 2-bit BCSE-based technique reported earlier when implemented on Xilinx field-programmable gate array (FPGA) device XC2VP4FF672-6. Similarly, the proposed design supports 93.14 MHz operating frequency, which is 59.2% and 74.2% greater when compared to 2-bit BCSE- and 3-bit BCSE-based approach when implemented on XC2V3000FF1152-4. The proposed structure also shows improved performance in terms of speed and area when compared to distributed arithmetic (DA)-based and multiply-accumulate (MAC)-based approaches.

Similar content being viewed by others

References

Joe Mitola 1995 The software radio architecture. IEEE Commun. Mag. 33(5): 26–38

Francois Rivet, Yann Deval, Jean-Baptiste Begueret, Dominique Dallet, Philippe Cathelin and Didier Belot 2008 A disruptive receiver architecture dedicated to software-defined radio. IEEE Trans. Circuits Syst-II: Exp. Briefs 55(4): 344–348

Asad A Abidi 2007 The path to the software-defined radio receiver. IEEE J. Solid-State Circuits 42(5): 954–966

Cristina de la Morena-Álvarez-Palencia, David Rodríguez-Aparicio and Mateo Burgos-García 2010 Software-defined radio technologies for emergency and professional communications. IEEE International Carnahan Conference on Security Technology, San Jose, CA, 357–363

Martin P, Praveen R, Min L, Antoine D, Liesbet Van der P and Francky C 2010 Future software-defined radio platforms and mapping flows. IEEE Signal Process. Mag. 27(2): 22–33

Sabbir A Osmany, Frank Herzel and J Christoph Schett 2010 An integrated 0.6–4.6 GHz, 5–7 GHz, 10–14 GHz, and 20–28 GHz frequency synthesizer for software-defined radio applications. IEEE J. Solid-State Circuits 45(9): 1657–1668

Tore Ulversoy 2010 Software defined radio: Challenges and opportunities. IEEE Commun. Surveys Tutorials 12(4): 531–550

Walter H W Tuttlebee 1999 Software-defined radio: Facets of a developing technology. IEEE Personal Commun. 6(2): 38–44

Rahul K, Joshi R C and Kota Solomon Raju 2009 A FPGA partial reconfiguration design approach for RASIP SDR. IEEE India Conference

Wang L and Wu F-Y 2009 Dynamic partial reconfiguration in FPGAs. IEEE Third International Symposium on Intelligent Information Technology Application. 445–448

Chandran J, Kaluri R, Singh J, Owall V and Velijanovski R 2004 Xilinx Virtex II Pro implementation of a reconfigurable UMTS digital channel filter. In: Proceedings of IEEE Workshop Electronic Design, Test, and Application 77–82

Chen K -H and Chieueh T -D 2006 A low-power digit-based reconfigurable FIR filter. IEEE Trans. Circuits Syst. II, Exp. Briefs 53(8): 617–621

Sheikh F, Miller M, Richards B, Markovic D and Nikolic B 2010 A 1–190 MSample/s 8–64 tap energy-efficient reconfigurable FIR filter for multi-mode wireless communication. In: Proceedings of IEEE Symposium on VLSI Circuits 207–208

Lee S -J, Choi J -W, Kim S W and Park J 2011 A reconfigurable FIR filter architecture to trade off filter performance for dynamic power consumption. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 19(12): 2221–2228

Hsiao S -F, Zhang Jian J -H and Chen M –C 2013 Low-cost FIR filter designs based on faithfully rounded truncated multiple constant multiplication/accumulation. IEEE Trans. Circuits Syst. II, Exp. Brief 60(5): 287–291

Mahesh R and Vinod A P 2010 New reconfigurable architectures for implementing FIR filters with low complexity. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 29(2): 275–288

Sagadevan K, Babu V and Arivumani Samson S 2012 Novel reconfigurable architecture with low complexity FIR filter. In: Proceedings of IEEE International Conference on PRIME 145–151

Sandhiya V, Karthick S and Valarmathy M 2014 A survey of new reconfigurable architectures for implementing FIR filters with low complexity. In: Proceedings of IEEE International Conference on Computer Communication and Informatics: 1–9

Indranil Hatai, Indrajit Chakrabarti and Swapna Banerjee 2015 An efficient VLSI architecture of a reconfigurable pulse-shaping FIR interpolation filter for multistandard DUC. IEEE Trans. VLSI Syst. 23(6): 1150–1154

Meher P K, Chandrasekaran S and Amira A 2008 FPGA realization of FIR filters by efficient and flexible systolization using distributed arithmetic. IEEE Trans. Signal Process. 56(7): 3009–3017

Park S Y and Kumar Meher P 2014 Efficient FPGA and ASIC realizations of a DA-based reconfigurable FIR digital filter. IEEE Trans. Circuits Syst. II, Exp. Briefs 61(7): 511–515

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Prasanna, S.C., Joy Vasantha Rani, S.P. An efficient implementation of reconfigurable interpolation root-raised cosine FIR filter for software-defined radio application. Sādhanā 41, 1189–1201 (2016). https://doi.org/10.1007/s12046-016-0551-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12046-016-0551-2