Abstract

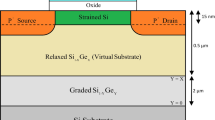

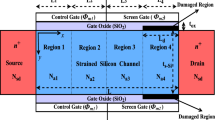

Growing a silicon (Si) layer on top of stacked Si-germanium (Ge) compressive layer can introduce a tensile strain on the former, resulting in superior device characteristics. Such a structure can be used for high performance complementary metal-oxide-semiconductor (CMOS) circuits. Down scaling metal-oxide-semiconductor field-effect transistors (MOSFETs) into the deep submicron/nanometer regime forces the source (S) and drain (D) series resistance to become comparable with the channel resistance and thus it cannot be neglected. Owing to the persisting technological importance of strained Si devices, in this work, we propose a multi-iterative technique for evaluating the performance of strained-Si/strained-Si1-y Ge y /relaxed-Si1-x Ge x MOSFETs and its related circuits in the presence of S/D series resistance, leading to the development of a simulator that can faithfully plot the performance of the device and related digital circuits. The impact of strain on device/circuit performance is also investigated with emphasis on metal gate and high-k dielectric materials.

Similar content being viewed by others

References

DALAPATI G K, CHATTOPADHYAY S, DRISCOLL L S, O’NEILL A G, KWA K S K, OLSEN S H. Extraction of strained-Si metal-oxide-semiconductor field-effect transistor parameters using small signal channel conductance method [J]. Journal of Applied Physics, 2006, 99(3): 034501–034508.

LEE M L, FITZGERALD E A, BULSARA M T, CURRIE M T, LOCHTEFELD A. Strained Si, SiGe, and Ge channels for high-mobility metal-oxide-semiconductor field-effect transistors [J]. Journal of Applied Physics, 2005, 97(1): 011101–011127.

RIM K, HOYT J L, GIBBONS J F. Fabrication and analysis of deep submicron strained-Si N-MOSFET’s [J]. IEEE Transactions on Electron Devices, 2000, 47(7): 1406–1415.

FOSSUM J G, ZHANG W. Performance projections of scaled CMOS devices and circuits with strained Si-on-SiGe channels [J]. IEEE Transactions on Electron Devices, 2003, 50(4): 1042–1049.

WANG Bin, ZHANG He-ming, HU Hui-yong, ZHANG Yu-ming, ZHOU Chun-yu, LI Yu-chen. Effect of substrate doping on threshold voltages of buried channel pMOSFET based on strained-SiGe technology [J]. Journal of Central South University, 2014, 21: 2292–2297.

FLACHOWSKY S, WEI A, ILLGEN R, HERRMANN T, HONTSCHEL J, HORSTMANN M, KLIX W, STENZEL R. Understanding strain-induced drive-current enhancement in strained-silicon n-MOSFET and p-MOSFET [J]. IEEE Transactions on Electron Devices, 2010, 57(6): 1343–1354.

AUTH C, CAPPELLANI A, CHUN J S, DALIS A, DAVIS A, GHANI T, GLASS G, GLASSMAN T, HARPER M, HATTENDORF M, HENTGES P, JALOVIAR S, JOSHI S, KLAUS J, KUHN K, LAVRIC D, LU M, MARIAPPAN H, MISTRY K, NORRIS B, RAHHAL-ORABI N, RANADE P, SANDFORD J, SHIFREN L, SOUW V, TONE K, TAMBWE F, THOMPSON A, TOWNER D, TROEGER T, VANDERVOORN P, WALLACE C, WIEDEMER J, WIEGAND C. 45 nm high-k + metal gate strain-enhanced transistors [C]// Symposium on VLSI Technology Digest of Technical Papers. Honolulu, HI, USA: IEEE, 2008: 128–129.

CHEN C H, LEE T L, HOU T H, CHEN C L, CHEN C C, HSU J W, CHENG K L, CHIU Y H, TAO H J, JIN Y, DIAZ C H, CHEN S C, LIANG M S. Stress memorization technique (SMT) by selectively strained-nitride capping for sub-65nm high-performance strained-Si device application [C]// Symposium on VLSI Technology Digest of Technical Papers. Honolulu, HI, USA: IEEE, 2004: 56–57.

GHANI T, ARMSTRONG M, AUTH C, BOST M, CHARVAT P, GLASS G, HOFFMANN T, JOHNSON K, KENYON C, KLAUS J, MCINTYRE B, MISTRY K, MURTHY A, SANDFORD J, SILBERSTEIN M, SIVAKUMAR S, SMITH P, ZAWADZKI K, THOMPSON S, BOHR M. A 90 nm high volume manufacturing logic technology featuring novel 45 nm gate length strained silicon CMOS transistors [C]// IEEE IEDM Technical Digest. Washington DC, USA: IEEE, 2003: 978–980.

ANG K W, CHUI K J, BLIZNETSOV V, DU A, BALASUBRAMANIAN N, LI M F, SAMUDRA G, YEO Y C. Enhanced performance in 50 nm n-MOSFETs with silicon-carbon source/drain regions [C]// IEEE IEDM Technical Digest. San Francisco, CA, USA: IEEE, 2004: 1069–1071.

CURRIE M T, LEITZ C W, LANGDO T A, TARASCHI G, FITZGERALD E A, ANTONIADIS D A. Carrier mobilities and process stability of strained Si n-and p-MOSFETs on SiGe virtual substrates [J]. Journal of Vacuum Science & Technology B, 2001, 19(6): 2268–2279.

LEITZ C W, CURRIE M T, LEE M L, CHENG Z Y, ANTONIADIS D A, FITZGERALD E A. Hole mobility enhancements in strained Si/Si1-yGey p-type metal-oxide-semiconductor field-effect transistors grown on relaxed Si1-xGex (x<y) virtual substrates [J]. Applied Physics Letters, 2001, 79(25): 4246–4248.

CHENG Z, JUNG J, LEE M L, PITERA A J, HOYT J L, ANTONIADIS D A, FITZGERALD E A. Hole mobility enhancement in strained-Si/strained-SiGe heterostructure p-MOSFETs fabricated on SiGe-on-insulator (SGOI) [J]. Semiconductor Science and Technology, 2004, 19: L48–L51.

JUNG J, YU S, LEE M L, HOYT J L, FITZGERALD E A, ANTONIADIS D A. Mobility enhancement in dual-channel P-MOSFETs [J]. IEEE Transactions on Electron Devices, 2004, 51(9): 1424–1431.

LEE M L, FITZGERALD E A. Hole mobility enhancements in nanometer-scale strained-silicon heterostructures grown on Ge-rich relaxed Si1-xGex [J]. Journal of Applied Physics, 2003, 94(4): 2590–2596.

TSANG Y L, CHATTOPADHYAY S, UPPAL S, ESCOBEDO COUSIN E, RAMAKRISHNAN H K, OLSEN S H, O’NEILL A G. Modeling of the threshold voltage in strained Si/Si1-xGex/Si1-yGey (x = y) CMOS architectures [J]. IEEE Transactions on Electron Devices, 2007, 54(11): 3040–3048.

JUNG J, YU S, OLUBUYIDE O O, HOYT J L, ANTONIADIS D A, LEE M L, FITZGERALD E A. Effect of thermal processing on mobility in strained Si/strained Si1-yGey on relaxed Si1-xGex (x<y) virtual substrates [J]. Applied Physics Letters, 2004, 84(17): 3319–3321.

OLSEN S H, O’NEILL A G, CHATTOPADHYAY S, DRISCOLL L S, KWA K S K, NORRIS D J, CULLIS A G, PAUL D J. Study of single-and dual-channel designs for high-performance strained-Si-SiGe n-MOSFETs [J]. IEEE Transactions on Electron Devices, 2004, 51(7): 1245–1253.

CHUN S K, WANG K L. Effective mass and mobility of holes in strained Si1-xGex layers on (001) Si1-yGey substrate [J]. IEEE Transactions on Electron Devices, 1992, 39(9): 2153–2164.

LIN Da-wen, CHENG Ming-lung, WANG Shyh-wei, WU Chung-Cheng, CHEN Ming-Jer. A novel method of MOSFET series resistance extraction featuring constant mobility criteria and mobility universality [J]. IEEE Transactions on Electron Devices, 2010, 57(4): 890–897.

CAMPBELL J P, CHEUNG K P, SUEHLE J S, OATES A. A simple series resistance extraction methodology for advanced CMOS devices [J]. IEEE Electron Device Letters, 2011, 32(8): 1047–1049.

BINDU B, DASGUPTA N, DASGUPTA A. Analytical model of drain current of strained-Si/strained-Si1-YGeY/relaxed-Si1-XGeX NMOSFETs and PMOSFETs for circuit simulation [J]. Solid-State Electronics, 2006, 50(3): 448–455.

ENGSIEW K, ANWAR S, ISMAIL R. Quantum mechanical effects on the threshold voltage of nanoscale dual channel strained Si/strained Si1-yGey/relaxed Si1-xGex MOSFETs [J]. Journal of Computational and Theoretical Nanoscience, 2013, 10(5): 1231–1235.

RABAEY J M, CHANDRAKASAN A, NIKOLIC B. Digital integrated circuits: A design perspective [M]. New Jersey: Pearson Education, 2003.

PSPICE User’s manual [M]// Cadence ORCAD 16.6. San Jose, CA, USA: Cadence Design Systems Inc, 2012.

TANNER Tools user’s manual [M]. Monrovia, CA: Tanner Research Inc, 2006.

ATLAS Users manual [M]. Santa Clara, CA, USA: Silvaco Inc, 2012.

TAURUS MEDICI user guide [M]. Mountain View, CA, USA: Synopsys Inc, 2012.

TABERKIT A M, BOUAZZA-GUEN A. Engineering of nano-scale strained-MOSFETs: A solution for the mobility enhancement [J]. World Academy of Science, Engineering and Technology, International Journal of Electrical, Computer, Energetic, Electronic and Communication Engineering, 2015, 9(12): 1330–1333.

TANG Zhao-huan, TAN Kai-zhou, CUI Wei, WANG Bin. µMAX enhanced 190% of a strained NMOS based on SiGe virtual substrate [J]. Advanced Materials Research, 2013, 756–759: 154–157.

YU J, WANG C, YANG Y. Progress on the numerical calculation of electrical characteristics of strained SiGe channel p-MOSFET [J]. Applied Mechanics and Materials, 2013, 320: 465–472.

ARORA N. MOSFET modeling for VLSI simulation: Theory and practice [M]. Singapore: World Scientific, 2007.

RIM K, CHU J, CHEN H, JENKINS K A, KANARSKY T, LEE K, MOCUTA A, ZHU H, ROY R, NEWBURY J, OTT J, PETRARCA K, MOONEY P, LACEY D, KOESTER S, CHAN K, BOYD D, IEONG M, WONG H S. Characteristics and device design of sub-100 nm strained Si n-and p-MOSFETs [C]// Symposium on VLSI Technology Digest of Technical Papers. Honolulu, HI, USA: IEEE, 2002: 98–99.

JUNG J, LEE M L, YU S, FITZGERALD E A, ANTONIADIS D A. Implementation of both high-hole and electron mobility in strained Si/strained Si1-yGey on relaxed Si1-xGex (x<y) virtual substrate [J]. IEEE Electron Device Letters, 2003, 24(7): 460–462.

TEMPLE M P, PAUL D J, TANG Y T, WAITE A M, EVANS A G R, O’NEILL A G, ZHANG J, GRASBY T, PARKER E H C. The relative performance enhancement of strained-Si and buried channel p-MOS as a function of lithographic and effective gate lengths [C]// International Semiconductor Device Research Symposium. Washington DC, USA: IEEE, 2003: 51–52.

BSIM Model. [2013-11-01]. http://www-device.eecs.berkeley. edu/bsim.

RAMAKRISHNAN H. Strained silicon technology for low-power high-speed circuit applications [R]. U.K.: Newcastle University, 2008.

HWANG J R, HO J H, TING S M, CHEN T P, HSIEH Y S, HUANG C C, CHIANG Y Y, LEE H K, LIU A, SHEN T M, BRAITHWAITE G, CURRIE M, GERRISH N, HAMMOND R, LOCHTEFELD A, SINGAPOREWALA F, BULSARA M, XIANG Q, LIN M R, SHIAU W T, LOH Y T, CHEN J K, CHIEN S C, WEN F. Performance of 70 nm strained-silicon CMOS devices [C]// Symposium on VLSI Technology Digest of Technical Papers. Kyoto, Japan: IEEE, 2003: 103–104.

KANG S M, LEBLEBICI Y. CMOS digital integrated circuits: analysis and design [M]. New York: McGraw–Hill, 2003.

KUMAR S, JHA S. Impact of elliptical cross-section on the propagation delay of multi-channel gate-all-around MOSFET based inverters [J]. Microelectronics Journal, 2013, 44: 844–851.

FITZGERALD E A, GERRISH N. CMOS inverter and integrated circuits utilizing strained silicon surface channel MOSFETS: US, 0034529 [P]. 2003.

FRANCO J, KACZER B, MITARD J, TOLEDANO-LUQUE M, ROUSSEL P J, WITTERS L, GRASSER T, GROESENEKEN G. NBTI reliability of SiGe and Ge channel pMOSFETs with SiO2/HfO2 dielectric stack [J]. IEEE Transactions on Device and Materials Reliability, 2013, 13(4): 497–506.

BEISTER J, WACHOWIAK A, BOSCHKE R, HERRMANN T, UHLARZ M, MIKOLAJICK T. Mobility investigations on strained 30-nm high-k metal gate MOSFETs by geometrical magnetoresistance effect [J]. IEEE Transactions on Electron Devices, 2015, 62(6): 1819–1825.

GHOSH K, DAS S, FISSEL A, OSTEN H J, LAHA A. Epitaxial Gd2O3 on strained Si1-xGex layers for next generation complementary metal oxide semiconductor device application [J]. Applied Physics Letters, 2013, 103(15): 153501–153504.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Subindu, K., Amrita, K. & Mukul K, D. Strain induced changes in performance of strained-Si/strained-Si1-y Ge y /relaxed-Si1-x Ge x MOSFETs and circuits for digital applications. J. Cent. South Univ. 24, 1233–1244 (2017). https://doi.org/10.1007/s11771-017-3527-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11771-017-3527-4