Abstract

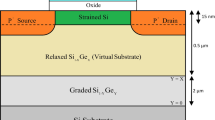

A physically based analytical model was developed to predict the performance of the plateau observed in the gate C-V characteristics of strained-Si/SiGe pMOSFET. Experimental results were used to validate this model. The extracted parameters from our model were t OX=20 nm, N D=1×1016 cm−3, t SSi=13.2 nm, consistent with the experimental values. The results show that the simulation results agree with experimental data well. It is found that the plateau can be strongly affected by doping concentration, strained-Si layer thickness and mass fraction of Ge in the SiGe layer. The model has been implemented in the software for strained silicon MOSFET parameter extraction, and has great value in the design of the strained-Si/SiGe devices.

Similar content being viewed by others

References

WEI Bao-lin, DAI Yu-jie, ZHANG Xiao-xing, LU Ying-jie. 1.0 V low voltage CMOS mixer based on voltage control load technique [J]. Journal of Central South University of Technology, 2011, 18(5): 1572–1578.

JANKOVIC N D, O’NELL A. Enhanced performance virtual substrate heterojunction bipolar transistor using strained-Si/SiGe emitter [J]. Semicond Sci Technol, 2003, 18(8): 901–906.

WU Tie-feng, ZhANG He-ming, HU Hui-yong. Effects of gate tunneling current on the static characteristics of CMOS circuits [J]. International Journal of Innovative Computing, Information and Control, 2011, 7(6): 3229–3237.

LI Bin, LIU Hong-xia, YUAN Bo, LI jin, LU Feng-ming. Model of electron mobility in inversion layer of strained Si/Si1−x Gex n type metal-oxide-semiconductor field-effect transistors [J]. Acta Phys Sin, 2011, 60(1): 017202. (in Chinese)

SONG Jian-jun, ZhANG He-ming, ShU Bin. The KP dispersion relation near Δi valley in strained Si1−x Gex/Si [J]. Chin J Semicond, 2008, 29(3): 441–446.

QIN Shan-shan, ZhANG He-ming, HU Hui-yong, DAI Xian-ying, XUAN Rong-xi, SHU Bin. An analytical threshold voltage model for dual-strained channel PMOSFET [J]. Chin Phys B, 2010, 19(11):117309.

SUGII N, HISAMOTO D, WASHIO K, YOKOYAMA N, KIMURA S. Performance enhancement of strained-Si MOSFETs fabricated on a chemical-mechanical-polished SiGe substrate [J]. IEEE Trans on Electron Devices, 2002, 49(12): 2237–43.

FLACHOWSKY S, WEI A, ILLGEN R, HERMANN T. Understanding strained-induced drive current enhancement in strained-silicon n-MOSFET and p-MOSFET [J]. IEEE Trans on Electron Devices, 2010, 57(6): 1343–1453.

WEI J Y, MAIKAP S, LEE M H. Hole confinement at Si/SiGe hetero-junction of strained-Si N and PMOS devices [J]. Solid-State Electronics, 2006, 50(2): 109–113.

BERA L K, MATHEW S, BALASUBRAMANIAN N. Analysis of carrier generation lifetime in strained-Si/SiGe hetero-junction MOSFETs from capacitance transient [J]. Appl Surf Sci, 2004, 224(1): 278–282.

LIAO J H, CANONICO M, ROBINSON M, SCHRODER D K. Characterization of strained Si/SiGe with pulsed MOS capacitor and gate oxide integrity measurements [J]. ECS Trans, 2006, 3(7): 1211–1222.

ZAINUDDIN A N M, HAQUE A. An analytical model for electrostatics of strained-Si n-type metal-oxide-semiconductor capacitors [J]. Semicond Sci Technol, 2007, 22(2): 125–127.

KELADIS N, SKARLATOS, TSAMIS C. Simulation of the electrical characteristics of MOS capacitors on strained-silicon substrates [J]. Physica Status Solidi C, 2008, 5(12): 3647–3650.

CHANDRASEKARAN K, XING Zhou, CHIAH S B, SHANGGUAN W, GUAN Huei See. Effect of substrate doping on the capacitance-voltage characteristics of strained-silicon pMOSFETS [J]. IEEE Electron Device Letters, 2006, 27(1): 62–64.

BINDU B, DASGUPTA N, DASGUPTA A. A unified model for gate Capacitance-Voltage characteristics and extraction of parameters of Si/SiGe hetero-structure pMOSFETs [J]. IEEE Trans on Electron Devices, 2007, 54(8): 1889–1896.

CHENG Y H, HU C M. Mosfet modeling & bsim3 user’s guide [M]. New York: Kluwer Academic Publishers, 2002.

Author information

Authors and Affiliations

Corresponding author

Additional information

Foundation item: Projects(51308040203, 6139801) supported by National Ministries and Commissions, China; Projects(72105499, 72104089) supported by the Fundamental Research Funds for the Central Universities, China; Project(2010JQ8008) supported by the Natural Science Basic Research Plan in Shaanxi Province of China

Rights and permissions

About this article

Cite this article

Wang, B., Zhang, Hm., Hu, Hy. et al. Physically based analytical model for plateau in gate C-V characteristics of strained silicon pMOSFET. J. Cent. South Univ. 20, 2366–2371 (2013). https://doi.org/10.1007/s11771-013-1745-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11771-013-1745-y